# Netra™ 20 Service and System Reference Manual

Sun Microsystems, Inc. 4150 Network Circle Santa Clara, CA 95054 U.S.A. 650-960-1300

Part No. 806-7336-14 February 2004 Rev A Copyright 2003 Sun Microsystems, Inc., 4150 Network Circle, Santa Clara, California 95054, U.S.A. All rights reserved.

Sun Microsystems, Inc. has intellectual property rights relating to technology embodied in the product that is described in this document. In particular, and without limitation, these intellectual property rights may include one or more of the U.S. patents listed at http://www.sun.com/patents and one or more additional patents or pending patent applications in the U.S. and in other countries.

This document and the product to which it pertains are distributed under licenses restricting their use, copying, distribution, and decompilation. No part of the product or of this document may be reproduced in any form by any means without prior written authorization of Sun and its licensors, if any.

Third-party software, including font technology, is copyrighted and licensed from Sun suppliers.

Parts of the product may be derived from Berkeley BSD systems, licensed from the University of California. UNIX is a registered trademark in the U.S. and in other countries, exclusively licensed through X/Open Company, Ltd.

Sun, Sun Microsystems, the Sun logo, AnswerBook2, docs.sun.com, and Solaris are trademarks or registered trademarks of Sun Microsystems, Inc. in the U.S. and in other countries.

All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. in the U.S. and in other countries. Products bearing SPARC trademarks are based upon an architecture developed by Sun Microsystems, Inc.

The OPEN LOOK and  $Sun^TM$  Graphical User Interface was developed by Sun Microsystems, Inc. for its users and licensees. Sun acknowledges the pioneering efforts of Sun Kerox in researching and developing the concept of visual or graphical user interfaces for the computer industry. Sun holds a non-exclusive license from Sun Kerox Graphical User Interface, which license also covers Sun icensees who implement OPEN LOOK GUIs and otherwise comply with Sun swritten license agreements.

U.S. Government Rights—Commercial use. Government users are subject to the Sun Microsystems, Inc. standard license agreement and applicable provisions of the FAR and its supplements.

DOCUMENTATION IS PROVIDED "AS IS" AND ALL EXPRESS OR IMPLIED CONDITIONS, REPRESENTATIONS AND WARRANTIES, INCLUDING ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT, ARE DISCLAIMED, EXCEPT TO THE EXTENT THAT SUCH DISCLAIMERS ARE HELD TO BE LEGALLY INVALID.

Copyright 2003 Sun Microsystems, Inc., 4150 Network Circle, Santa Clara, California 95054, Etats-Unis. Tous droits réservés.

Sun Microsystems, Inc. a les droits de propriété intellectuels relatants à la technologie incorporée dans le produit qui est décrit dans ce document. En particulier, et sans la limitation, ces droits de propriété intellectuels peuvent inclure un ou plus des brevets américains énumérés à http://www.sun.com/patents et un ou les brevets plus supplémentaires ou les applications de brevet en attente dans les Etats-Unis et dans les autres pays.

Ce produit ou document est protégé par un copyright et distribué avec des licences qui en restreignent l'utilisation, la copie, la distribution, et la décompilation. Aucune partie de ce produit ou document ne peut être reproduite sous aucune forme, par quelque moyen que ce soit, sans l'autorisation préalable et écrite de Sun et de ses bailleurs de licence, s'il y ena.

Le logiciel détenu par des tiers, et qui comprend la technologie relative aux polices de caractères, est protégé par un copyright et licencié par des fournisseurs de Sun.

Des parties de ce produit pourront être dérivées des systèmes Berkeley BSD licenciés par l'Université de Californie. UNIX est une marque déposée aux Etats-Unis et dans d'autres pays et licenciée exclusivement par X/Open Company, Ltd.

Sun, Sun Microsystems, le logo Sun, AnswerBook2, docs.sun.com, et Solaris sont des marques de fabrique ou des marques déposées de Sun Microsystems, Inc. aux Etats-Unis et dans d'autres pays.

Toutes les marques SPARC sont utilisées sous licence et sont des marques de fabrique ou des marques déposées de SPARC International, Inc. aux Etats-Unis et dans d'autres pays. Les produits protant les marques SPARC sont basés sur une architecture développée par Sun Microsystems, Inc.

L'interface d'utilisation graphique OPEN LOOK et Sun™ a été développée par Sun Microsystems, Inc. pour ses utilisateurs et licenciés. Sun reconnaît les efforts de pionniers de Xerox pour la recherche et le développement du concept des interfaces d'utilisation visuelle ou graphique pour l'industrie de l'informatique. Sun détient une license non exclusive de Xerox sur l'interface d'utilisation graphique Xerox, cette licence couvrant également les licenciées de Sun qui mettent en place l'interface d'utilisation graphique OPEN LOOK et qui en outre se conforment aux licences écrites de Sun.

LA DOCUMENTATION EST FOURNIE "EN L'ÉTAT" ET TOUTES AUTRES CONDITIONS, DECLARATIONS ET GARANTIES EXPRESSES OU TACITES SONT FORMELLEMENT EXCLUES, DANS LA MESURE AUTORISEE PAR LA LOI APPLICABLE, Y COMPRIS NOTAMMENT TOUTE GARANTIE IMPLICITE RELATIVE A LA QUALITE MARCHANDE, A L'APTITUDE A UNE UTILISATION PARTICULIERE OU A L'ABSENCE DE CONTREFAÇON.

## Contents

### Part I Service

| 1. | System   | Description | 1–1 |

|----|----------|-------------|-----|

| 1. | Dystelli | Description |     |

- 1.1 System Features 1–1

- 1.2 System Unit Components 1–5

- 1.3 Environmental Performance 1–5

- 1.4 LEDs 1-6

- 1.4.1 System LEDs 1–6

- 1.4.2 LOMlite2 LEDs 1–9

- 1.4.3 PSU LEDs 1-11

### 2. Power-On Self Test 2-1

- 2.1 POST Overview 2–1

- 2.1.1 How to Use POST 2-2

- 2.2 Pre-POST Preparation 2–3

- 2.3 Running POST 2–4

- 2.4 POST Diagnostic Levels 2–4

- 2.4.1 diag-level Variable Set to max 2-5

- 2.4.2 diag-level Variable Set to min 2-5

- 2.4.3 Error Messages 2–6

#### 3. $SunVTS^{TM}$ 3–1

- 3.1 The Validation Test Suite 3–1

- 3.1.1 SunVTS Requirements 3–2

- 3.1.2 SunVTS References 3–2

- 3.1.3 Installation 3–3

- 3.1.4 New and Modified Features and Options 3–3

- 3.1.5 Starting SunVTS 3–5

- 3.2 SunVTS Tests 3-6

- 3.2.1 Guide to Using SunVTS 4.4 3–8

#### 4. Troubleshooting 4–1

- 4.1 Power-On Failure 4–2

- 4.2 System LEDs 4–2

- 4.3 Drive Failure 4–2

- 4.4 Power Supply Unit Troubleshooting 4–4

- 4.5 OpenBoot PROM Diagnostics 4–7

- 4.5.1 New Features 4–8

- 4.5.2 New and Modified Commands and Tests 4–9

- 4.5.3 Device Tree 4–14

- 4.5.4 Running the Diagnostics 4–18

- 4.6 OpenBoot Emergency Procedures 4–30

- 4.6.1 Stop-A 4-30

- 4.6.2 Stop-N 4-31

- 4.6.3 Stop-F 4-31

- 4.6.4 Stop-D 4-31

### 5. Before Servicing the System 5–1

- 5.1 Accessibility 5–1

- 5.2 Tools 5–2

5.3 System ON/STBY Switch 5–2 5.3.1 Powering On the System 5–2 5.3.2 Powering Off the System 5–4 5.4 Disconnection and Isolation 5–5 5.4.1 Netra 20 AC System 5–5 5.4.2 Netra 20 DC System 5–5 5.5 Antistatic Precautions 5–5 5.5.1 Attaching the Antistatic Wrist Strap 5–6 5.6 Top Access Cover 5–8 5.6.1 Preparation 5–9 5.6.2 Removing the Top Access Cover 5–9 5.6.3 Fitting the Top Access Cover 5–9 Front Fascia 5–10 5.7 5.7.1 Removing the Front Fascia 5–11 5.7.2 Fitting the Front Fascia 5–12 5.8 Air Filter 5–13 5.8.1 Removing and Fitting the Mesh Screen 5–13 5.8.2 Replacing the Filter 5–14 Power Subassemblies 6–1 6.1 Power Supply Unit 6–1 6.1.1 Preparation 6–2 6.1.2 Removing the PSU 6–2 6.1.3 Installing the PSU 6–3 6.2 Power Distribution Board 6–4 6.2.1 Preparation 6–4 6.2.2 Removing the PDB 6–5 6.2.3 Installing the PDB 6–6 6.3 System Switch and LED Assembly 6–8

6.

- 6.3.1 Preparation 6–8

- 6.3.2 Removing the System Switch and LED Assembly 6–9

- 6.3.3 Installing the System Switch and LED Assembly 6–10

#### 7. Fan Subassemblies 7–1

- 7.1 PSU Fans 7–2

- 7.1.1 Preparation 7–3

- 7.1.2 Removing the PSU Fans Assembly 7–4

- 7.1.3 Installing the PSU Fans Assembly 7–4

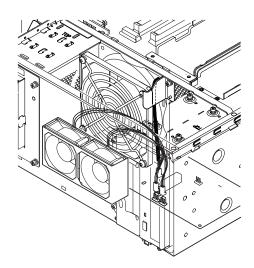

- 7.2 CPU Fan Assembly 7–5

- 7.2.1 Preparation 7–5

- 7.2.2 Removing the CPU Fan Assembly 7–7

- 7.2.3 Installing the CPU Fan Assembly 7–7

### 8. Storage Devices 8-1

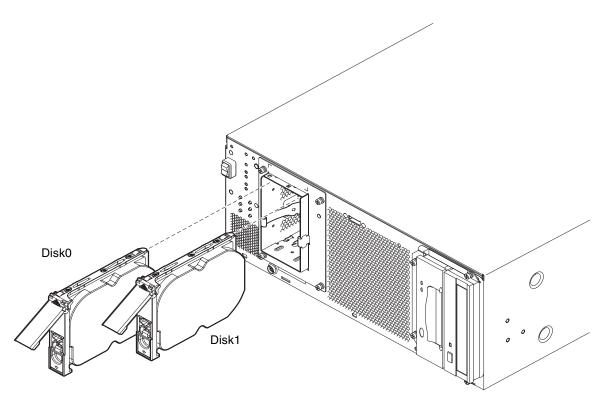

- 8.1 FC-AL Hard Disk Drive 8–1

- 8.1.1 Preparing to Remove a Disk Drive (Hot Swap) 8–2

- 8.1.2 Removing a Disk Drive (Hot Swap) 8–3

- 8.1.3 Hot Swapping a Disk Drive (Installation) 8–4

- 8.1.4 Preparing to Remove an Unmirrored Root Disk 8–5

- 8.1.5 Removing an Unmirrored Root Disk 8–5

- 8.1.6 Installing an Unmirrored Root Disk 8–6

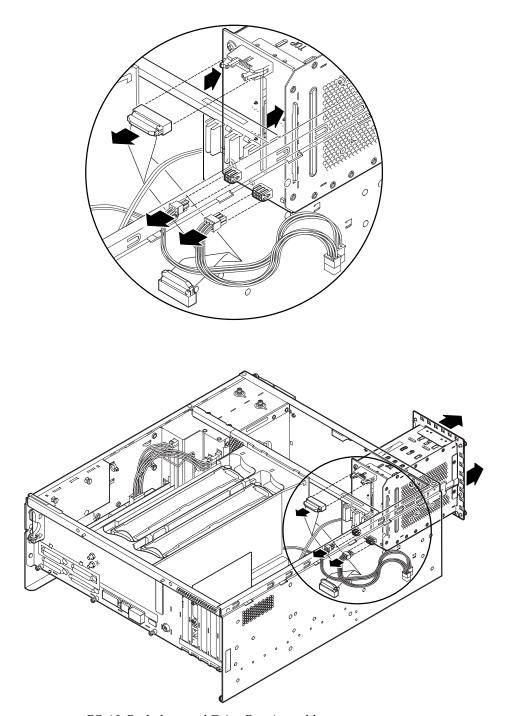

- 8.2 Fiber Channel Backplane and Drive Bay 8–6

- 8.2.1 Preparation 8–8

- 8.2.2 Removing the FC-AL Backplane and Drive Bay 8–8

- 8.2.3 Installing the FC-AL Backplane and Drive Bay 8–9

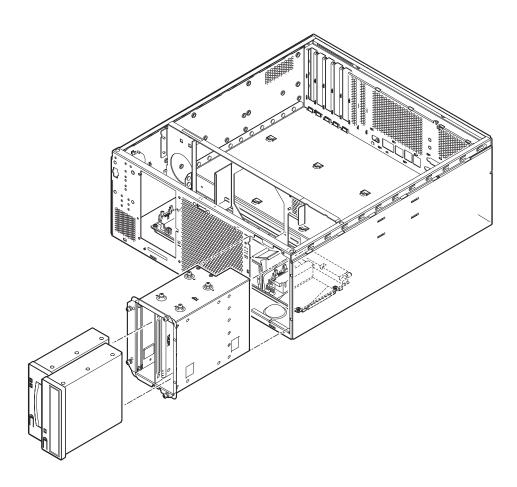

- 8.3 Removable Media Module 8–10

- 8.3.1 Preparation 8–11

- 8.3.2 Removing a Removable Media Module 8–11

### 8.3.3 Installing a Removable Media Module 8–12

### 9. Motherboard and Component Replacement 9–1

- 9.1 PCI Cards 9–2

- 9.1.1 Preparation 9–3

- 9.1.2 Removing a PCI Card 9–3

- 9.1.3 Installing a PCI Card 9–3

- 9.2 Processor Modules 9–4

- 9.2.1 Preparation 9–6

- 9.2.2 Removing a CPU Module 9-6

- 8.3.4 Installing a CPU Module 9–7

- 8.4 Memory Modules 9–8

- 8.4.1 Preparation 9–9

- 8.4.2 Removing a Memory Module 9–10

- 8.4.3 Installing a Memory Module 9–10

- 8.5 Replaceable Battery 9–11

- 8.5.1 Preparation 9–11

- 8.5.2 Removing the Battery 9–12

- 8.5.3 Installing the Battery 9–12

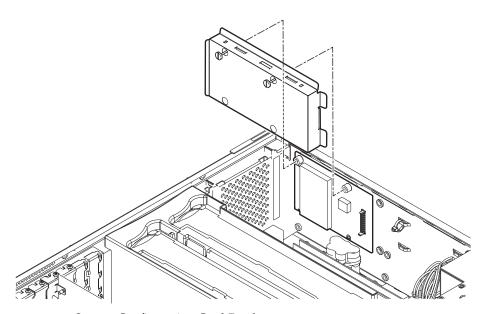

- 8.6 LOMLite2 Card 9–13

- 8.6.1 Preparation 9–14

- 8.6.2 Removing the LOMlite2 Card 9–14

- 8.6.3 Installing the LOMlite2 Card 9–14

- 8.7 System Configuration Card Reader 9–15

- 8.7.1 Preparation 9–15

- 8.7.2 Removing the SCCR 9–16

- 8.7.3 Installing the SCCR 9–16

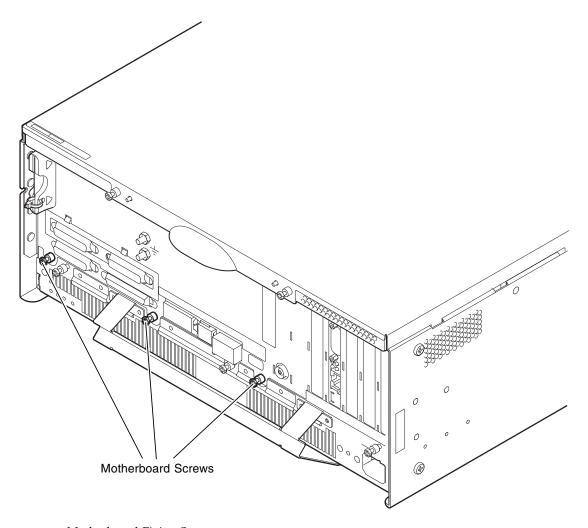

- 8.8 Motherboard 9–17

- 8.8.1 Preparation 9–17

- 8.8.2 Removing the Motherboard 9–19

- 8.8.3 Installing the Motherboard 9–22

### Part II System Reference

### 10. Functional Description 10-1

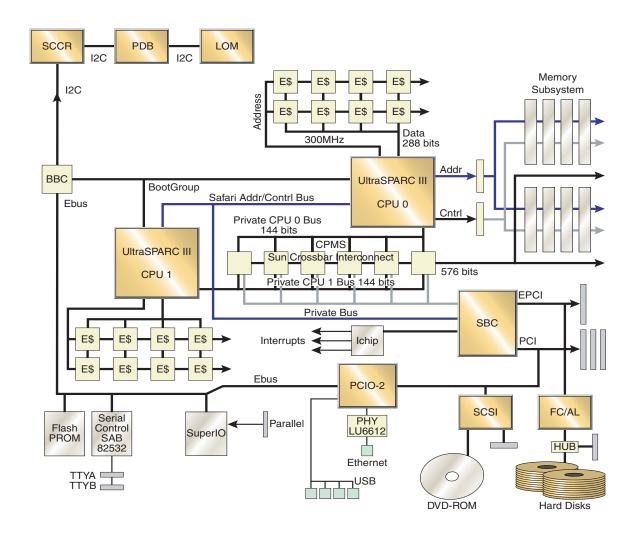

- 10.1 System 10–1

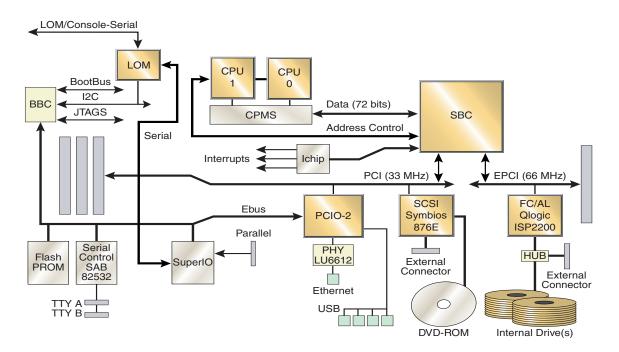

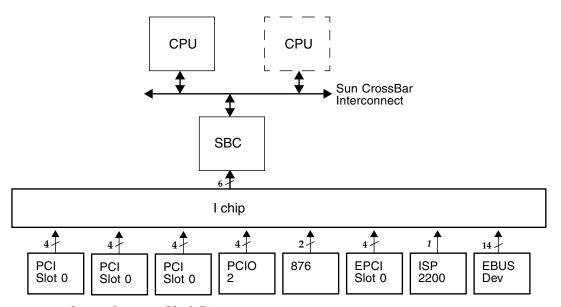

- 10.2 System Overview 10–2

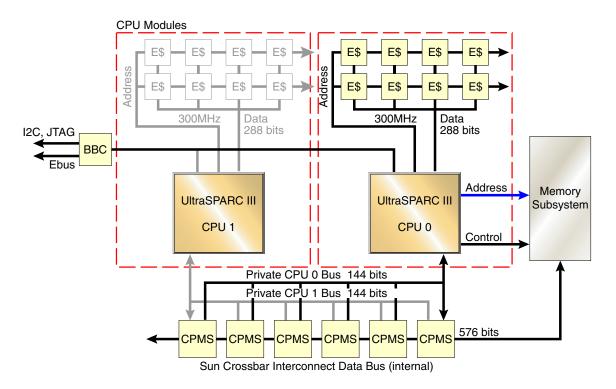

- 10.2.1 UltraSPARC-III Processor 10–3

- 10.2.2 Main Memory 10-6

- 10.2.3 I/O Subsystem 10–12

- 10.2.4 Interrupts 10–18

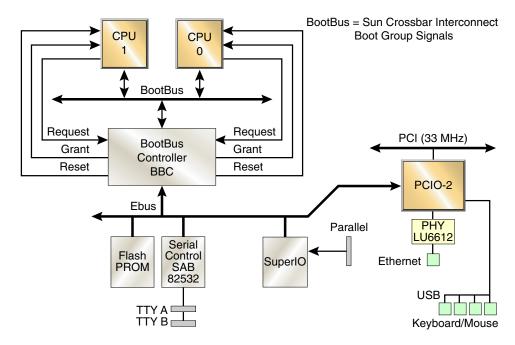

- 10.2.5 BootBus 10-19

- 10.2.6 I2C Bus 10-21

- 10.2.7 PCI Bus 10-23

- 10.2.8 Peripherals 10–25

- 10.2.9 Other Peripheral Assembly Options 10–26

- 10.2.10 USB Ports 10-27

- 10.2.11 Parallel Port 10–27

- 10.2.12 Serial Port 10–28

- 10.2.13 Ethernet 10–32

- 10.2.14 FC-AL Subsystem 10–33

- 10.2.15 SCSI 10-34

- 10.2.16 SuperI/O 10-36

- 10.3 Power Supply 10–37

- 10.3.1 AC PSU 10-37

- 10.3.2 DC PSU 10-37

- 10.3.3 Control Signals 10–38

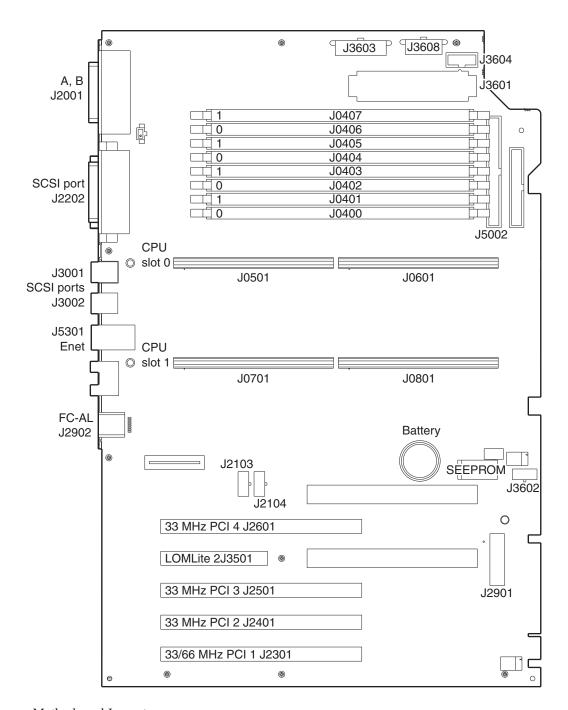

- 10.4 Motherboard 10-38

|     |       | 10.5.1 Flash PROM Jumpers 10–43              |

|-----|-------|----------------------------------------------|

| 11. | Exter | nal I/O Connectors 11-1                      |

|     | 11.1  | Parallel Connector 11–2                      |

|     | 11.2  | Serial Connectors 11–3                       |

|     | 11.3  | SCSI Connector 11–4                          |

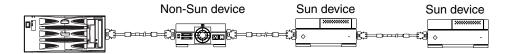

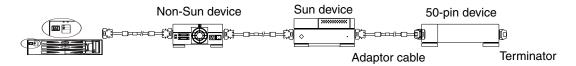

|     |       | 11.3.1 SCSI Implementation 11–6              |

|     |       | 11.3.2 SCSI Cabling and Configuration 11–6   |

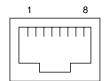

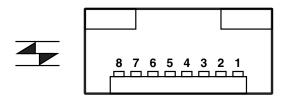

|     | 11.4  | Ethernet Connector 11–8                      |

|     | 11.5  | FC-AL Connector 11–10                        |

|     | 11.6  | USB Connectors 11–10                         |

|     | 11.7  | Alarms Ports 11–11                           |

|     | 11.8  | System Configuration Card Reader 11–12       |

| 12. | Mode  | em Setup 12–1                                |

| 14. | 12.1  | •                                            |

|     | 12.1  | Connecting a Modem to the Serial Ports 12–1  |

|     |       | 12.1.1 To Set Up the Modem 12–1              |

|     |       | 12.1.2 Serial Port Speed Change 12–2         |

|     |       | 12.1.3 Recommendations 12–3                  |

|     | 12.2  | Connecting a Modem to the LOMlite2 Port 12–3 |

|     |       | 12.2.1 Flow Control Feature 12–4             |

|     |       | 12.2.2 Login-Timeout Feature 12–5            |

10.5 Jumper Descriptions 10–42

#### Part III **Appendices**

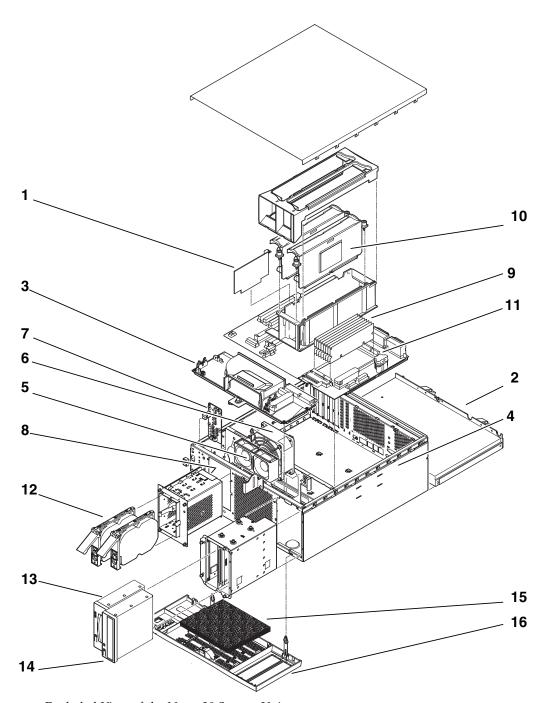

### A. Illustrated Parts List A-1

## B. Product Specification B-1

B.1 Physical Specification B–1 B.1.1 Dimensions B–1

- B.1.2 Mounting Flanges B–1

- B.2 Electrical Specification B–2

- B.2.1 Netra 20 AC System B-2

- B.2.2 Netra 20 DC System B-3

- B.3 Environmental Specification B-4

- B.3.1 Operating and Storage B-4

- B.3.2 Acoustic Noise B–5

- B.3.3 Earthquake B–5

- B.3.4 Electro-Magnetic Compatibility B–5

#### C. Tool Requirements C-1

- D. Motherboard Connectors D-1

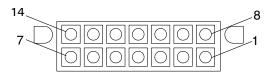

- D.1 SCCR Connector D-1

- D.2 Internal SCSI Connector D-3

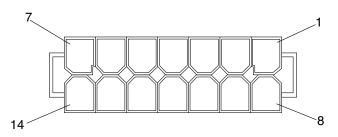

- D.3 Internal FC-AL Connector D-4

- D.4 Power Connectors D-5

- E. Example POST Diagnostic Output E-1

- F. Updating LOMlite2 Firmware F-1

- G. Connecting to the Netra 20 Server G-1

- G.1 Connecting to the LOM Serial Port G–1

- G.2 Connecting to the Serial Ports G–2

Glossary Glossary-1

Index Index-1

## Figures

| FIGURE 1-2 | Front Panel System LEDs 1–7                                             |  |  |  |

|------------|-------------------------------------------------------------------------|--|--|--|

| FIGURE 1-4 | PSU Status LEDs (Netra 20 AC System) 1-11                               |  |  |  |

| FIGURE 1-5 | PSU Status LEDs (Netra 20 DC System) 1-12                               |  |  |  |

| FIGURE 3-1 | SunVTS Menu Bar 3-5                                                     |  |  |  |

| FIGURE 4-1 | Power Supply Connector Jack Location 4-6                                |  |  |  |

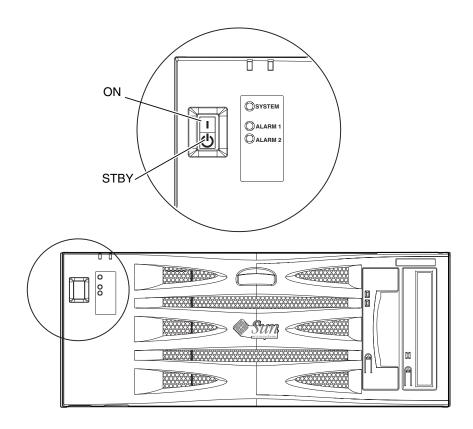

| FIGURE 5-1 | System Power On/STBY (Front Panel) 5-3                                  |  |  |  |

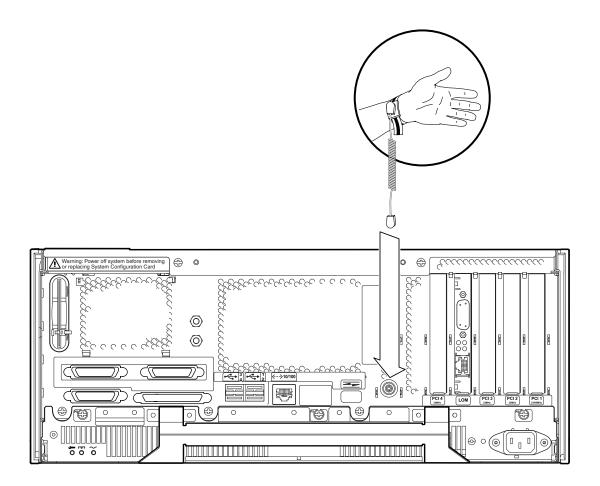

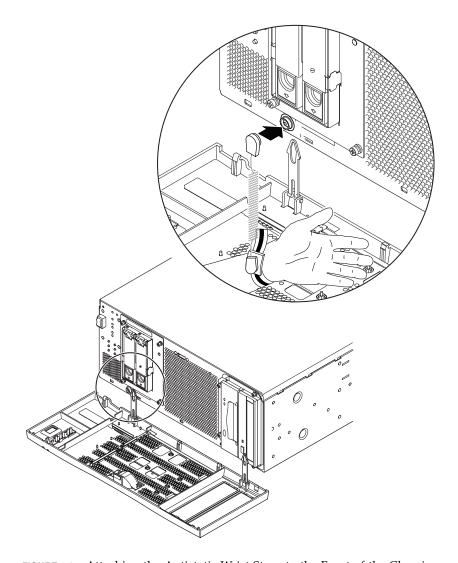

| FIGURE 5-3 | Attaching the Antistatic Wrist Strap to the Front of the Chassis $$ 5–7 |  |  |  |

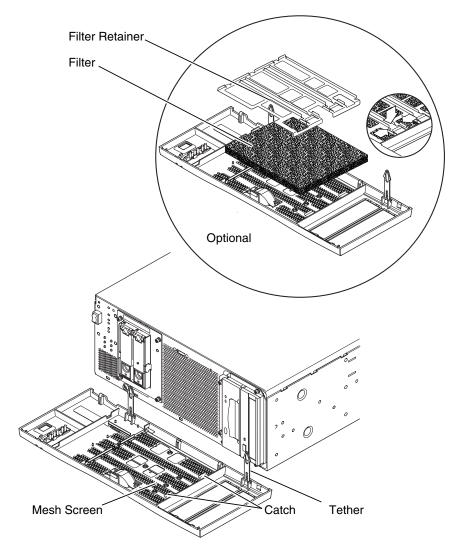

| FIGURE 5-5 | Front Fascia and Filters 5-11                                           |  |  |  |

| FIGURE 6-2 | Power Distribution Board 6–4                                            |  |  |  |

| FIGURE 6-3 | System Switch and LED Assembly 6–9                                      |  |  |  |

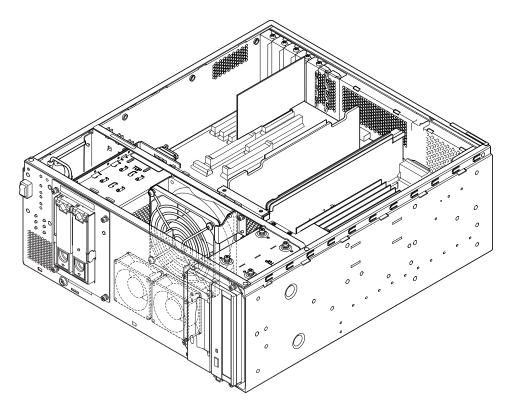

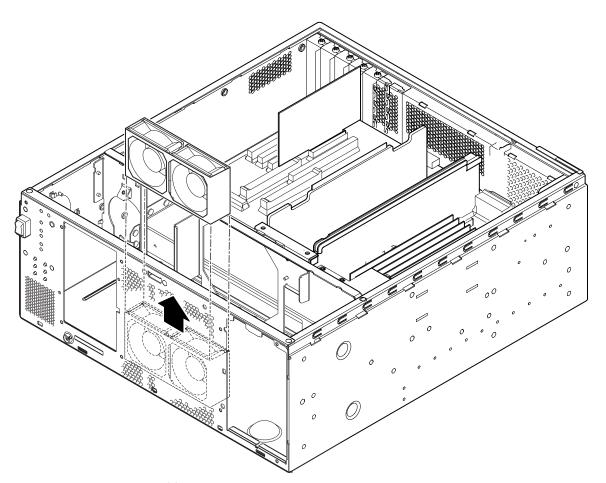

| FIGURE 7-1 | Netra 20 System Fans 7–2                                                |  |  |  |

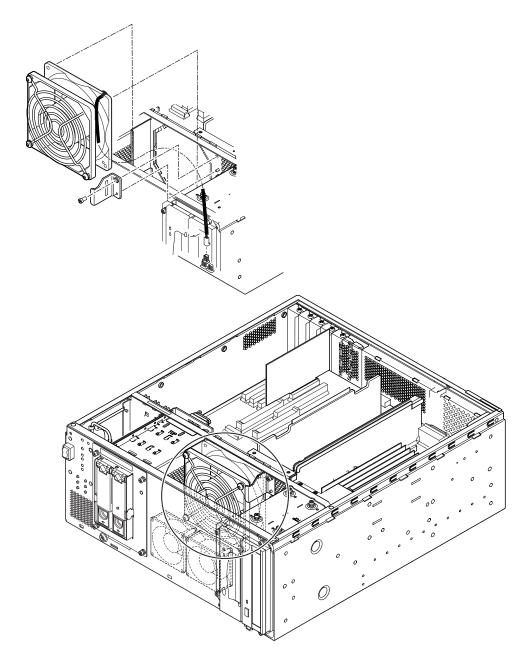

| FIGURE 7-3 | CPU Fan 7–6                                                             |  |  |  |

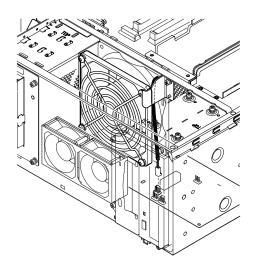

| FIGURE 7-4 | Fan Connectors 7–8                                                      |  |  |  |

| FIGURE 8-2 | FC-AL Backplane and Drive Bay Assembly 8-7                              |  |  |  |

| FIGURE 8-3 | Removable Media Modules 8-10                                            |  |  |  |

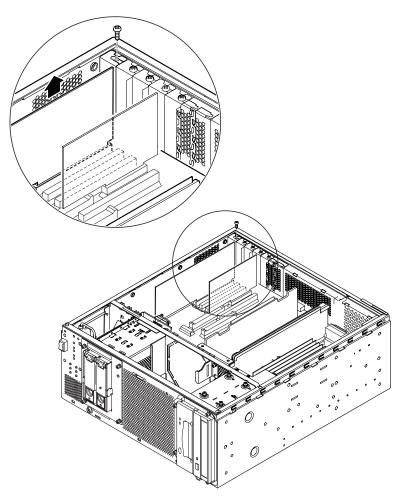

| FIGURE 9-1 | PCI Card Slots 9–2                                                      |  |  |  |

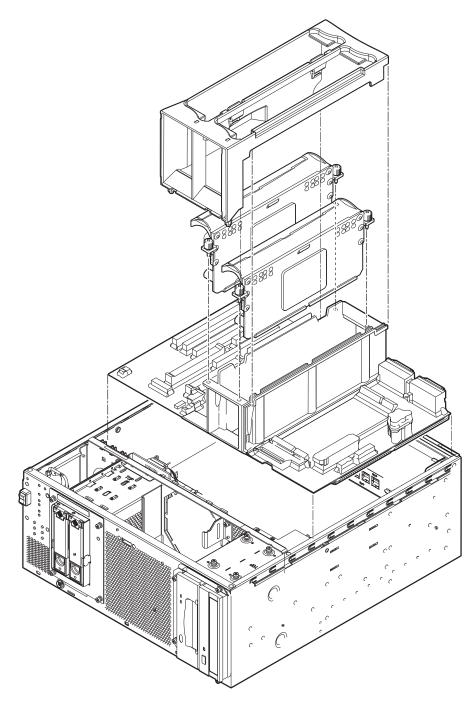

| FIGURE 9-2 | CPU Modules 9–5                                                         |  |  |  |

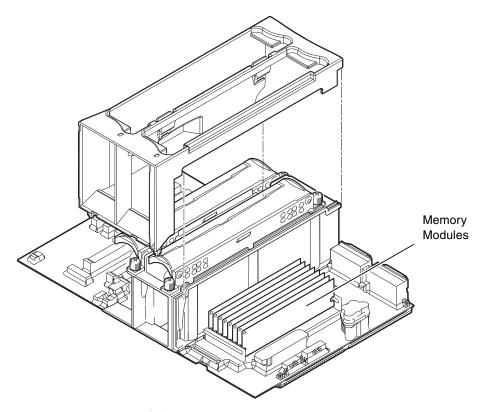

| FIGURE 8-4 | Memory Modules 9–9                                                      |  |  |  |

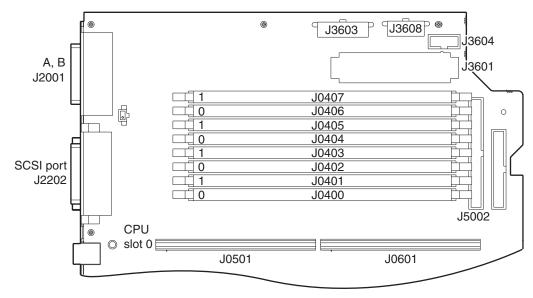

| FIGURE 8-5 | Memory Banks 9-11                                                       |  |  |  |

| EIGUDE 9.6 | Rattery Location 9_12                                                   |  |  |  |

- FIGURE 8-8 System Configuration Card Reader 9–15

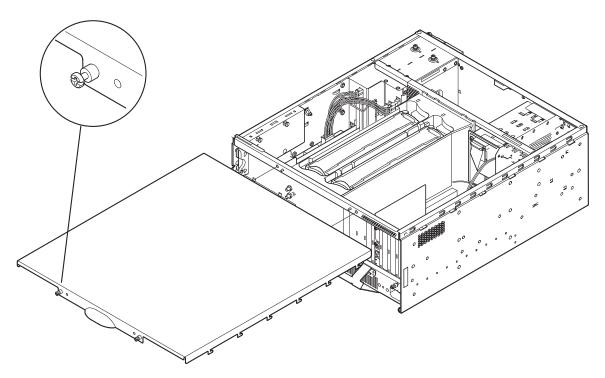

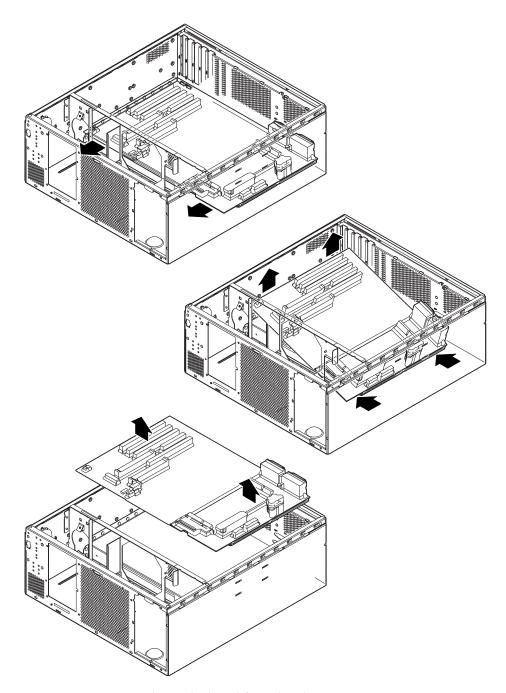

- FIGURE 8-11 Removing the Motherboard from the Chassis 9–21

- FIGURE 10-4 Memory Subsystem 10-6

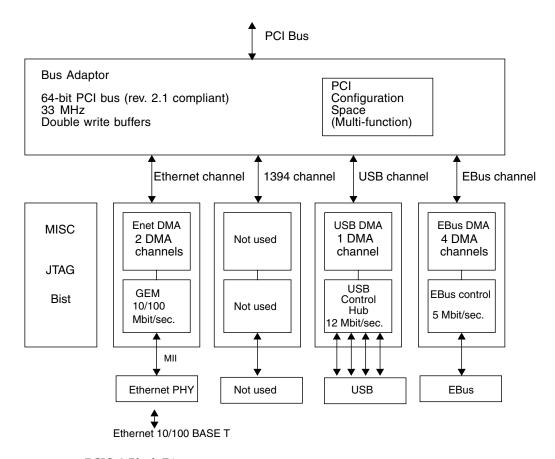

- FIGURE 10-9 Ebus 10-17

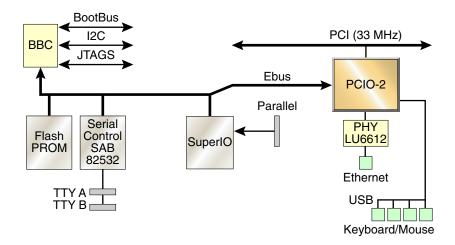

- FIGURE 10-11 Netra 20 Boot Bus 10-19

- FIGURE 10-13 USB and Parallel Port Functional Block Diagram 10-27

- FIGURE 10-14 Serial Port Functional Block Diagram 10–29

- FIGURE 10-15 LOMlite2 Serial Port Functionality 10-31

- FIGURE 10-16 FC-AL Disk subsystem 10-34

- FIGURE 10-17 Configuration for the SCSI Bus 10–35

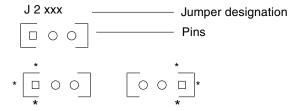

- FIGURE 10-19 Selected Jumper Settings 10–42

- FIGURE 10-20 Identifying Jumper Pins 10–42

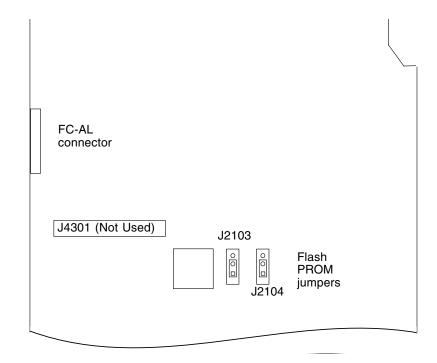

- FIGURE 10-21 Flash PROM Jumper Locations 10-43

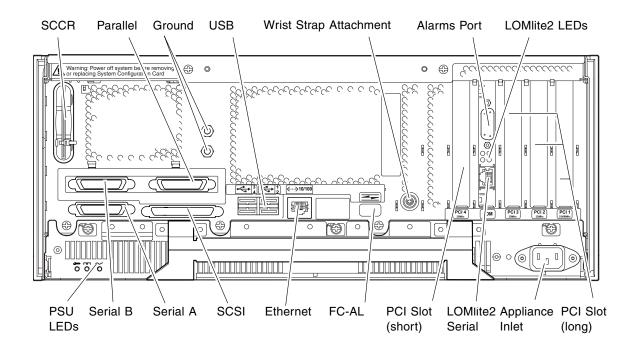

- FIGURE 11-2 DB-25 Parallel Connector 11-2

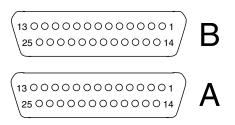

- FIGURE 11-3 DB-25 Serial Connectors 11-3

- FIGURE 11-4 68-Pin SCSI Connector 11-4

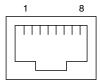

- FIGURE 11-6 RJ45 TPE Socket 11-8

- FIGURE 11-7 FC-AL Connector 11–10

- FIGURE 11-8 Twin Series A USB Connector 11–10

- FIGURE 11-9 DB-15 (Male) Alarms Service Port Connector 11–11

- FIGURE 11-10 RJ45 Lights Out Management Serial Connector 11–12

- FIGURE D-1 Smart Card Reader Connector, J3604, Pin Assignments D-1

- FIGURE D-2 Internal SCSI Connector, J5002 D-3

- FIGURE D-3 Internal FC-AL Connector, J2901 D-4

- FIGURE D-4 Power Supply Connector J3603 D-6

- FIGURE D-5 Power Supply Connector J3601 D-7

## **Tables**

| TABLE 1-1 | Front Panel System LED Functions 1–8                  |

|-----------|-------------------------------------------------------|

| TABLE 1-2 | LOMlite2 Status LED Functions 1–9                     |

| TABLE 1-3 | PSU Status LED Functions 1–11                         |

| TABLE 1-4 | PSU Status LED Functions (Netra 20) 1–12              |

| TABLE 2-1 | POST Completion Times 2–5                             |

| TABLE 3-1 | New SunVTS Commands 3–4                               |

| TABLE 3-2 | SunVTS Processor Tests 3–6                            |

| TABLE 3-3 | SunVTS Memory Tests 3–7                               |

| TABLE 3-4 | SunVTS Storage Device Tests 3-7                       |

| TABLE 3-5 | SunVTS Network Tests 3–7                              |

| TABLE 3-6 | SunVTS Communications Port Tests 3-7                  |

| TABLE 3-7 | SunVTS Custom Test 3–8                                |

| TABLE 4-1 | Internal Drives Identification 4–3                    |

| TABLE 4-2 | J3601 Voltage-Pin Assignments 4–7                     |

| TABLE 4-3 | J3603 Voltage-Pin Assignments 4-7                     |

| TABLE 4-4 | probe and test Commands 4-10                          |

| TABLE 4-5 | Selected OpenBoot PROM On-Board Diagnostic Tests 4-12 |

| TABLE 4-6 | Parent Node Names 4-15                                |

| TABLE 4-7 | Child Node Names 4-17                                 |

| TABLE 4-8 | OBDiag Configuration Variables 4–19                   |

System-Specific OBDiag Self Tests 4-20 TABLE 4-9 TABLE 4-10 obdiag Help 4-24 TABLE 10-1 Valid Memory Configurations 10–9 PCI Slot-to-PCI Bus Mapping 10-24 TABLE 10-2 Internal Hard Drive Features 10-26 TABLE 10-3 ISP2200A GPIO Bits 10-33 TABLE 10-4 AC Power Supply Output Values 10–37 TABLE 10-5 TABLE 10-6 DC Power Supply Output Values 10–37 TABLE 10-7 Power Supply Control Signal Levels 10–38 TABLE 10-8 Motherboard Component Functions 10–40 **TABLE 10-9** Flash PROM Jumper Settings 10–43 Parallel Connector Pinout 11-2 TABLE 11-1 TABLE 11-2 Serial Connector Pinout, RS423/RS232 11-3 **TABLE 11-3** 68-Pin SCSI Connector Pinout 11–4 Determining SCSI Bus Length 11–7 TABLE 11-4 TPE Connector Pinout 11–8 TABLE 11-5 **TABLE 11-6** TPE STP-5 Cable Lengths 11–9 **TABLE 11-7** FC-AL Connector Pinout 11–10 USB Connector Pinout 11–11 TABLE 11-8 **TABLE 11-9** Alarms Service Port Connector Pinout 11–11 TABLE 11-10 Lights Out Management Serial Connector Pinout 11–12 RJ45 to DB-25 Headshell Connections 12-3 TABLE 12-1 TABLE A-1 Netra 20 Field Replaceable Units A-3 TABLE A-2 Netra 20 Optional Components A-4 TABLE B-1 AC Power Supply Input Requirements B–2 **TABLE 12-2** DC Power Supply Input Requirements B-3 TABLE D-1 SCCR, J3604, Pin Assignments D–2 TABLE D-2 Internal SCSI Connector, J5002 D-3 TABLE D-3 Internal FC-AL Connector, J2901 D-5 Power Connectors D-5 TABLE D-4

| TABLE D-5 | Power Supply Connector J3603 Pin Description  | D-6 |

|-----------|-----------------------------------------------|-----|

| TABLE D-6 | Power Supply Connector J3601 Pin Description  | D-7 |

| TABLE G-1 | LOM Serial Port Adaptor Pinout G-2            |     |

| TABLE G-2 | Netra 20 Serial Port Crossover Adaptor Pinout | G–3 |

## Code Samples

| CODE EXAMPLE 2-1  | POST Test Menu 2-2                                      |

|-------------------|---------------------------------------------------------|

| CODE EXAMPLE 2-2  | POST Test Control Flags Menu 2-3                        |

| CODE EXAMPLE 2-3  | Sample POST Console Error Message 2-6                   |

| CODE EXAMPLE 2-4  | Sample POST Serial Port Error Message 2-6               |

| CODE EXAMPLE 4-1  | probe-scsi Diagnostic Output Message 4-10               |

| CODE EXAMPLE 4-3  | Test Output Message 4-11                                |

| CODE EXAMPLE 4-2  | probe-scsi-all Output Message 4-11                      |

| CODE EXAMPLE 4-4  | Watch-Clock Diagnostic Output Message 4-12              |

| CODE EXAMPLE 4-5  | watch-net Diagnostic Output Message 4-13                |

| CODE EXAMPLE 4-6  | watch-net-all Diagnostic Output Message 4-13            |

| CODE EXAMPLE 4-7  | 66 MHz PCI Bus Devices 4-15                             |

| CODE EXAMPLE 4-8  | 33 MHz PCI Bus Devices 4-15                             |

| CODE EXAMPLE 4-9  | Typical reset-all Output with default OBP Settings 4-22 |

| CODE EXAMPLE 4-10 | obdiag Menu 4-23                                        |

| CODE EXAMPLE 4-11 | SUNW, lomv@0, 0 Diagnostic Output Message 4-24          |

| CODE EXAMPLE 4-12 | SUNW, qlc@4 Diagnostic Output Message 4-25              |

| CODE EXAMPLE 4-13 | bbc@1,0 Diagnostic Output Message 4-25                  |

| CODE EXAMPLE 4-14 | ebus@5 Diagnostic Output Message 4-25                   |

| CODE EXAMPLE 4-15 | flashprom@0,0 Diagnostic Output Message 4-26            |

| CODE EXAMPLE 4-16 | gpio@1,300600 Diagnostic Output Message 4-26            |

```

i2c@1, 2e Diagnostic Output Message with TIP Line Installed 4-26

CODE EXAMPLE 4-17

CODE EXAMPLE 4-18

i2c@1,30 Diagnostic Output Message 4-27

CODE EXAMPLE 4-19

network@5,1 Diagnostic Output Message 4-27

parallel@1,300278 Diagnostic Output Message 4-27

CODE EXAMPLE 4-20

pmc@1,300700 Diagnostic Output Message 4-28

CODE EXAMPLE 4-21

rtc@1,300070 Diagnostic Output Message 4-28

CODE EXAMPLE 4-22

scsi@6 Diagnostic Output Message 4-28

CODE EXAMPLE 4-23

CODE EXAMPLE 4-24

scsi@6,1 Diagnostic Output Message 4-29

serial@1,400000 Diagnostic Output Message 4-29

CODE EXAMPLE 4-25

usb@5,3 Diagnostic Output Message 4-29

CODE EXAMPLE 4-26

CODE EXAMPLE 4-27

test-all Diagnostic Output Message 4-30

POST Output with diag-level Set to max E-1

CODE EXAMPLE E-1

CODE EXAMPLE E-2

POST Output with diag-level set to min E-9

CODE EXAMPLE F-1

Output From LOM env Command F-4

```

## **Preface**

This manual supports the Netra 20 server and comprises two parts:

- Part I, *Service*, is written for technicians, advanced computer system end-users with experience in replacing hardware and troubleshooting, system administrators, and authorized service providers (ASPs). Only suitably qualified service personnel may carry out tasks described in this manual that involve the removal of the top cover.

- Part II, *System Reference*, is written for OEM engineers, system designers and application programmers who have to perform advanced tasks concerned with the maintenance and configuration of the system.

## How This Book Is Organized

**Chapter 1** provides an overview of the key features of the Netra 20 server.

Chapter 2 describes the Power-On Self-Test (POST) diagnostics.

**Chapter 3** contains an overview of the SunVTS Validation Test Suite.

**Chapter 4** describes how to troubleshoot and correct hardware problems.

**Chapter 5** discusses the precautions you should take before working on the system, and explains how to gain access to the internal components.

**Chapter 6** describes how to remove and fit the PSU and power subassemblies.

Chapter 7 describes how to remove and fit the system fans.

**Chapter 8** describes how to remove and fit the system storage devices.

**Chapter 9** describes how to remove and fit the motherboard and the components that interface with it.

**Chapter 10** provides a functional description of the system.

**Chapter 11** provides information about the I/O connectors.

**Chapter 12** describes how to connect and set up a modem.

**Appendix A** provides an illustrated list of replaceable parts and components.

**Appendix B** provides a product specification.

**Appendix C** contains a list of tools that are needed to service the system.

**Appendix D** provides details of the internal motherboard connectors.

**Appendix E** provides an example of a typical POST diagnostic output.

**Appendix F** describes how to update LOMlite2 firmware.

**Appendix G** describes how to connect to the Netra 20 serial ports.

## Typographic Conventions

| Typeface <sup>1</sup> | Meaning                                                                                                            | Examples                                                                                                                                                                   |

|-----------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AaBbCc123             | The names of commands, files, and directories; on-screen computer output                                           | Edit your.login file. Use ls -a to list all files. % You have mail.                                                                                                        |

| AaBbCc123             | What you type, when contrasted with on-screen computer output                                                      | % <b>su</b><br>Password:                                                                                                                                                   |

| AaBbCc123             | Book titles, new words or terms, words to be emphasized. Replace command-line variables with real names or values. | Read Chapter 6 in the <i>User's Guide</i> .  These are called <i>class</i> options.  You <i>must</i> be superuser to do this.  To delete a file, type rm <i>filename</i> . |

<sup>1.</sup> The settings on your browser might differ from these settings.

## Shell and System Prompts

| Shell                                 | Prompt        |

|---------------------------------------|---------------|

| C shell                               | machine_name% |

| C shell superuser                     | machine_name# |

| Bourne shell and Korn shell           | \$            |

| Bourne shell and Korn shell superuser | #             |

| OpenBoot PROM                         | $ok^1$        |

| LOMlite2                              | lom>          |

<sup>1.</sup> In dual processor systems, the processor number, 0 or 1, is included; for example,  $\{0\}$  ok

## Related Documentation

| Application          | Title                                                           | Part Number          |

|----------------------|-----------------------------------------------------------------|----------------------|

| Installation<br>User | Netra 20 Installation and User's Guide                          | 806-7334             |

| Compliance           | Netra 20 Compliance and Safety Manual                           | 816-5279             |

| OpenBoot PROM        | OpenBoot 3.x Command Reference<br>OpenBoot PROM Quick Reference | 806-1377<br>806-2908 |

## Accessing Sun Documentation

You can view, print, or purchase a broad selection of Sun documentation, including localized versions, at:

http://www.sun.com/documentation

## Contacting Sun Technical Support

If you have technical questions about this product that are not answered in this document, go to:

http://www.sun.com/service/contacting

## Sun Welcomes Your Comments

Sun is interested in improving its documentation and welcomes your comments and suggestions. You can submit your comments by going to:

http://www.sun.com/hwdocs/feedback

Please include the title and part number of your document with your feedback:

Netra 20 Service and System Reference Manual, part number 806-7336-14

## PART | Service

## System Description

This chapter lists the main features of the Netra 20 server, and describes the function of the LEDs located on the front and rear panels.

The chapter contains the following sections:

- Section 1.1, "System Features" on page 1-1

- Section 1.2, "System Unit Components" on page 1-5

- Section 1.3, "Environmental Performance" on page 1-5

- Section 1.4, "LEDs" on page 1-6

The Netra 20 server is a single or dual processor device that uses the UltraSPARC<sup>TM</sup> III 900 MHz processor or UltraSPARC III+ 1.2 GHz processor.

- High performance processors

- High performance disk, system, memory and I/O subsystems

- High performance peripheral component interconnect (PCI) I/O

- Rack mounting options

- Front-to-back cooling

- AC and DC power supply options

- Alarms functionality for remote management

- System configuration card

- Hot swap disk drives

- Visual diagnostics

- Environmental monitoring

## 1.1 System Features

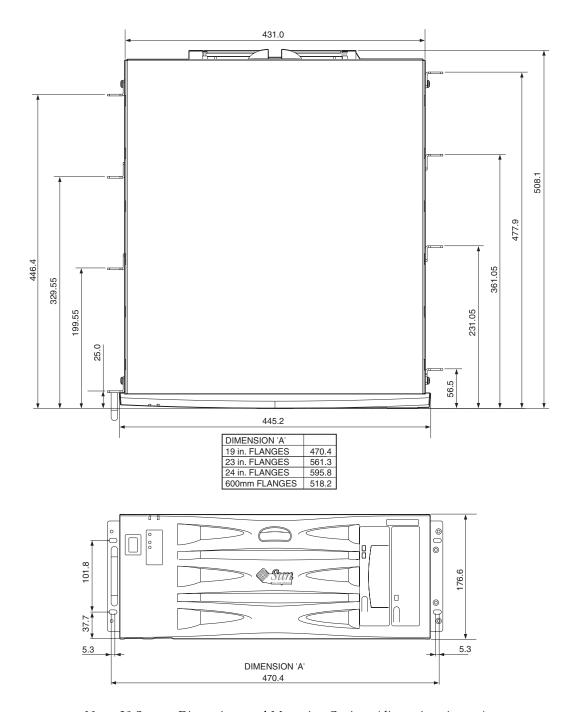

System unit components are housed in a 4RU rack-mounting enclosure designed to NEBS Level 3 standards. Overall chassis dimension (width x depth x height) are 445.2 mm x 508.1 mm x 176.6 mm (17.52 inches x 20.00 inches x 6.95 inches). Flange mounting kits are available for installing the system in 19-inch, 23-inch, 24-inch and 600- mmracks (see FIGURE 1-1). A slide adaptor kit is also available.

FIGURE 1-1 Netra 20 System Dimensions and Mounting Options (dimensions in mm)

1-2

System unit electronics are contained on a single printed circuit board (motherboard). The motherboard contains the CPU modules, memory, system control application-specific integrated circuits (ASICs) and I/O ASICs.

A fully-configured system weighs approximately 27.3kg (60lb).

## **Operating Environment**

- Solaris 8 Update 2/02 or later

- Solaris 9 Update 12/02 or later

#### Power

■ Rack mounting enclosure with one single-feed 100–240 VAC power supply unit (AC) or one twin-feed –48 VDC/–60 VDC power supply unit (DC)

### **Processors**

Support for up to two 900 MHz UltraSPARC III processors modules or up to two

1.2 GHz UltraSPARC III+ processor modules, each with 8 MByte Ecache

### Memory

Support for up to eight 256 Mbyte, 512 Mbyte or 1 Gbyte Dual Inline Memory Module (DIMMS) installed in two groups of four providing from 1 to 8 Gbytes of memory

#### Ю

- Four PCI 2.1 compliant slots:

- one long<sup>1</sup> 64/32-bit, 66/33 MHz

- two long 64/32-bit, 33 MHz

- one short $^2$  64/32-bit, 33 MHz

- One 10/100BaseT Ethernet connection

- One Fast-Wide SCSI connection

- Four USB connections (two twin Series A ports) @ 12 Mb/s

- One external FC-AL connection

- Two internal FC-AL connections for hard disks

- Two RS232/RS423 serial ports

- One parallel port

<sup>1.</sup> Up to 312 mmlong

<sup>2.</sup> Up to 174.6 mmlong

- One DB-15 LOMlite2 alarms relay port

- One RJ45 LOMlite2 alarms serial port

## System Configuration

■ I2C system configuration card reader (SCCR)

## Storage

- Up to two FC-AL 1-inch hot swap hard disks (73 Gbyte)

- External hardware RAID support through PCI

- Software RAID support Sun Logical Volume Manager (SLVM)

- Up to two removable media drives (DVD-ROM and DDS-4 DAT)

## Reliability, Availability and Serviceability

- LOMLite2 automatic system recovery

- Remote diagnosis via Solaris and LOMLite2

- Hot swap disks

- Diagnostic LEDs

- Environmental monitoring

- Field Replaceable Unit (FRU) ID support

#### Documentation

- Installation and User's Guide

- Service and System Reference Manual (this document)

- Compliance and Safety Manual

- Release Notes

## Software Support

- Lights Out Management 2.0 (LOMlite2)

- SLVM (Sun Logical Volume Manager)

- SunVTS<sup>TM</sup> 4.4 (Sun Validation Test Suite)

- SunMC (Sun Management Center)

- SNMP (Sun Netra SNMP Management Agent)

- SunCluster

- SRS/SunUP<sup>TM</sup> ready

## PCI Card Support

- SunSwift<sup>TM</sup>

- Fast Ethernet

- Quad Fast Ethernet (QFE)

- High Speed Serial Interface (HSI)

- Serial Asynchronous Interface (SAI)

- ATM-155

- Dual Differential SCSI

- Gigabit Ethernet

- FC-AL

- FC-AL and Gigabit Ethernet combination

- SSL Crypto Accelerator

## 1.2 System Unit Components

The system unit components are listed by part number in Appendix A.

**Note** – The part numbers listed in Appendix A were correct when this manual was published but they are subject to change without notice. Numerical references illustrated in FIGURE A-1 correlate to the references listed in TABLE A-1 and TABLE A-2. Refer to your authorized Sun sales representative or service provider to confirm a part number before you order a replacement part.

## 1.3 Environmental Performance

The principal environmental requirements are given in Section B.3, "Environmental Specification" on page B-4.

## 1.4 LEDs

The Netra 20 server has three sets of LEDs that show the status of the system.

## 1.4.1 System LEDs

The system LEDs are located behind the front fascia, immediately to the right of the ON/STBY switch as you face the unit, as shown in FIGURE 1-2.

Light pipes transmit the Power, System, Alarm1, Alarm2 and Fault LEDs through the fascia and are visible from the front of the system. To view the remaining LEDs, you must lower the front fascia.

FIGURE 1-2 Front Panel System LEDs

The Alarm1, Alarm2, System and Fault LEDs are mirrored on the LOMlite2 card visible from the rear of the system (see Section 1.4.2, "LOMlite2 LEDs" on page 1-9).

TABLE 1-1

Front Panel System LED Functions

| LED                                | Icon/Legend | Color | Function                                                                                                                                                                                                              |  |

|------------------------------------|-------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Power                              | <b>(1)</b>  | Green | <b>Illuminated</b> continuously while power is supplied to the system.                                                                                                                                                |  |

| System <sup>1</sup>                | SYSTEM      | Green | Off (or reset) during power up procedures and illuminated when UNIX is running and the Alarms driver is installed. This LED is reset by a hardware Watchdog timeout, or whenever the user-defined Alarm3 is asserted. |  |

| Alarm1 <sup>1</sup>                | ALARM1      | Amber | Illuminated whenever the user-defined Alarm1 is asserted                                                                                                                                                              |  |

| Alarm2 <sup>1</sup>                | ALARM2      | Amber | Illuminated whenever the user-defined Alarm2 is asserted                                                                                                                                                              |  |

| Input A OK                         | DC-A        | Green | <b>Illuminated</b> when the input voltage from feeder A is above 37V <b>Off</b> when Input A is below 35V Not used in the AC version                                                                                  |  |

| Input B OK                         | DC-B        | Green | <b>Illuminated</b> when the input voltage from feeder B is above 37V <b>Off</b> when Input B is below 35V Not used in the AC version                                                                                  |  |

| Fault <sup>1</sup>                 | 4           | Amber | Driven by the LOMlite2 module under identified system fault conditions                                                                                                                                                |  |

| Disk0 Active <sup>2</sup>          | <b>①</b>    | Green | Illuminated when Disk0 is active                                                                                                                                                                                      |  |

| Disk0 OK to<br>Remove <sup>2</sup> |             | Blue  | <b>Illuminated</b> , in response to a user request, when Disk0 can be removed safely without affecting the system operation                                                                                           |  |

| Disk0 Fault <sup>2</sup>           | 4           | Amber | Illuminated when the system has identified a fault in Disk0                                                                                                                                                           |  |

| Disk1 Active <sup>2</sup>          | <b>(1)</b>  | Green | Illuminated when Disk1 is active                                                                                                                                                                                      |  |

| Disk1 OK to<br>Remove <sup>2</sup> |             | Blue  | <b>Illuminated</b> , in response to a user request, when disk1 can be removed safely without affecting the system operation                                                                                           |  |

| Disk1 Fault <sup>2</sup>           | 4           | Amber | Illuminated when the system has identified a fault in Disk1                                                                                                                                                           |  |

<sup>1.</sup> These LEDs are duplicated on the LOMlite2 card face plate (see Section 1.4.2, "LOMlite2 LEDs" on page 1-9).

<sup>2.</sup> Lower the front fascia to view these LEDs.

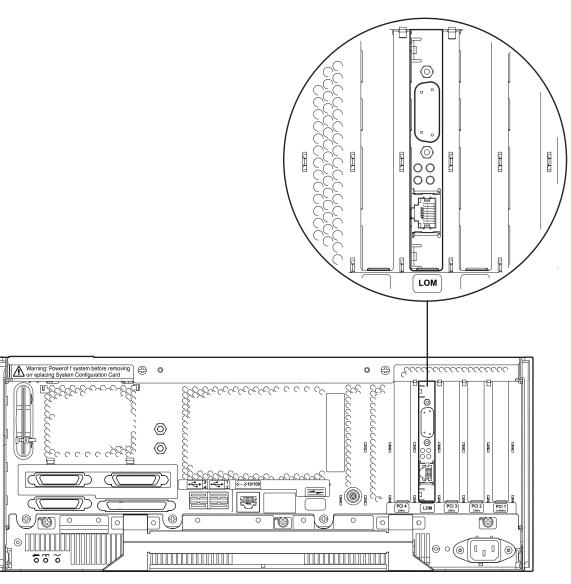

## 1.4.2 LOMlite2 LEDs

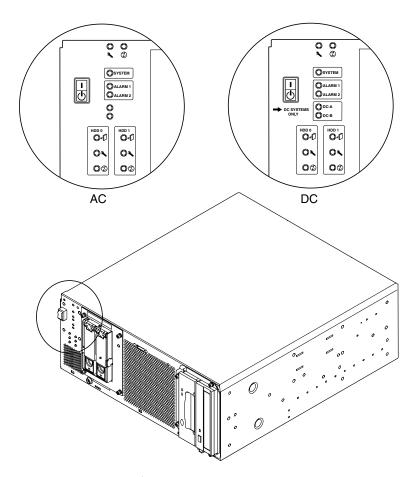

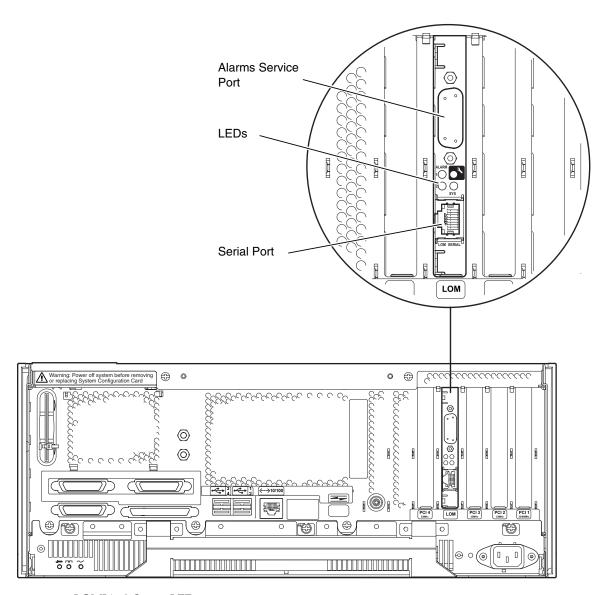

The LOMlite2 status LEDs, which mirror the alarm status and power LEDs on the front panel, are located on the rear of the system, between the LOMlite2 DB-15 alarms relay port and RJ45 serial port as shown in FIGURE 1-3.

**TABLE 1-2** LOMlite2 Status LED Functions

| LED     | Icon/Legend | Color | Function                                                                                |

|---------|-------------|-------|-----------------------------------------------------------------------------------------|

| Alarm 1 | 1           | Amber | <b>Illuminated</b> when user-defined Alarm 1 is asserted                                |

| Alarm 2 | 2           | Amber | <b>Illuminated</b> when user-defined Alarm 2 is asserted                                |

| Fault   | 4           | Amber | Driven by the LOMlite2 card and <b>illuminated</b> when a system fault condition exists |

| System  | SYS         | Green | Illuminated when Solaris is running and the LOMlite2 driver is installed                |

|         |             |       | Off while the system is powering up                                                     |

|         |             |       | Reset by watchdog timeout, assertion of user-<br>defined Alarm 3                        |

FIGURE 1-3 LOMLite2 Status LEDs

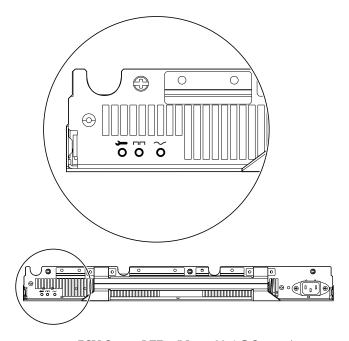

## 1.4.3 PSU LEDs

The PSU status LEDs are located at the left hand end of the PSU (see FIGURE 1-4).

## 1.4.3.1 Netra 20 AC System

TABLE 1-3

PSU Status LED Functions

| LED         | Icon   | Color | Function                                                                                                                                     |

|-------------|--------|-------|----------------------------------------------------------------------------------------------------------------------------------------------|

| AC Input OK | $\sim$ | Green | Illuminated when AC is present and above 85VAC                                                                                               |

| PSOK        |        | Green | Illuminated when output voltages are within operating range Flashes when PSU is in Standby mode                                              |

| Fail        | ~      | Amber | Illuminated when PSU is in a Fault condition Off when PSU is enabled (OK) Flashes if unit is within 10°C of thermal shutdown or has shutdown |

FIGURE 1-4 PSU Status LEDs (Netra 20 AC System)

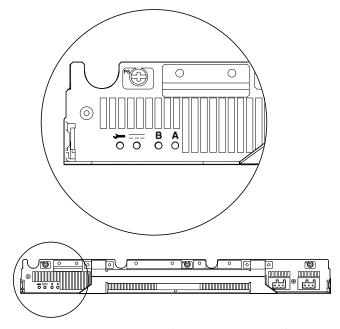

## 1.4.3.2 Netra 20 DC System

TABLE 1-4

PSU Status LED Functions (Netra 20)

| LED        | lcon | Color | Function                                                                                                                                         |

|------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Fail       | 4    | Amber | Illuminated when PSU is in a Fault condition Off when PSU is not enabled (OK) Flashes if unit is within 10°C of thermal shutdown or has shutdown |

| PSOK       |      | Green | <b>Illuminated</b> when output voltages are within operating range <b>Flashes</b> when PSU is in Standby mode                                    |

| Input B OK | В    | Green | <b>Illuminated</b> when input voltage from feeder B is above 37 V <b>Off</b> when Input B is below 35 V                                          |

| Input A OK | Α    | Green | <b>Illuminated</b> when input voltage from feeder A is above 37V <b>Off</b> when Input A is below 35V                                            |

FIGURE 1-5 PSU Status LEDs (Netra 20 DC System)

# Power-On Self Test

This chapter describes how to initiate power-on self test (POST) diagnostics.

The chapter contains the following topics:

- Section 2.1, "POST Overview" on page 2-1

- Section 2.2, "Pre-POST Preparation" on page 2-3

- Section 2.3, "Running POST" on page 2-4

- Section 2.4, "POST Diagnostic Levels" on page 2-4

# 2.1 POST Overview

POST is a firmware program that is useful in determining if a portion of the system has failed. POST verifies the core functionality of the system, including the CPU module(s), motherboard, memory, and some on-board I/O devices, and generates messages that can be useful in determining the nature of a hardware failure. POST can be run even if the system is unable to boot.

POST detects most system faults and is located in the motherboard OpenBoot<sup>TM</sup> PROM. POST can be set to run by the OpenBoot program at power up by setting two environment variables, the diag-switch? and the diag-level flag, which are stored on the System Configuration Card.

POST diagnostic and error message reports are displayed on a console.

## 2.1.1 How to Use POST

POST runs automatically when the system power is applied, and following an automatic system reset if both of the following conditions apply:

- diag-switch? is set to true (default is false)

- diag-level is set to min, max or menus (default is min)

If diag-level is set to min or max, POST performs an abbreviated or extended test, respectively (see Section 2.4, "POST Diagnostic Levels" on page 2-4).

If diag-level is set to menus, a menu of all the tests executed at power up is displayed (CODE EXAMPLE 2-1):

#### CODE EXAMPLE 2-1 POST Test Menu

```

{0}* Xcall Test

{0}Sending Cross Calls to CPU AID 1

{0}

0

Return

{0}

1

Run all Tests in this Menu

{0}

Change Test Control Flags

{0}

3

* Reset Menu

{0}

* CPU Tests

{0}

5

* Ecache Tests

{0}

* Memory Tests

{0}

7

* Schizo Tests

{0}

* RIO Tests

* Estar Test (UP only)

{0}

{0}

а

* ECC Tests

* MP Tests

{0}

{0}

* BIST

{0}

* System Frequency and CPU Ratio

{0}

е

* I2C/Fan/Temperature/Smart card

{0}

f

* Run POST

10

{0}

* Return to OBP

{0}Selection

```

Selection 2 enables you to change the test control flags (CODE EXAMPLE 2-2):

### CODE EXAMPLE 2-2 POST Test Control Flags Menu

```

{0}Selection:2

{0}

0

Return

{0}

1

Run all Tests in this Menu

{0}

Change Test Control Flags

{0}

* Toggle Trace Flag - c

{0}

* Toggle Loop-a-test flag - 1

{0}

* Toggle Loop-on-error flag - e

{0}

* Toggle Print-all-error flag - p

{0}

* Display current state of all flags

{0}

* Help on Test Flags

{0}Selection:

```

**Note** - If diag-switch = false, POST is disabled. If diag-switch = true and diag-level = max, POST runs in max mode. If diag-switch = true and diag-level = min, POST runs in min mode.

To run POST, power cycle the system.

# 2.2 Pre-POST Preparation

1. Connect a terminal to the LOM serial port on the Netra 20 server to view POST progress and error messages. See Section G.1, "Connecting to the LOM Serial Port" on page G-1.

**Note** — By default, the input and output device is the LOM serial port. To direct POST output to ttya or ttyb, set both input-device and output-device to ttya or ttyb:

2. Set the diag-switch? and diag-out-console configuration variables to true:

```

ok setver diag-switch? true

ok setver diag-out-console true

```

Alternatively, from the shell prompt:

```

# eeprom diag-switch?=true

# eeprom diag-out-console=true

```

Set the diag-level configuration variable to max or min (see Section 2.4, "POST Diagnostic Levels" on page 2-4).

```

ok setenv diag-level value

```

or

```

# eeprom diag-level=value

```

**Note** - The default value is min.

# 2.3 Running POST

To run POST:

- Initiate POST using one of the following methods:

- a. Briefly press the power ON/STBY switch to power cycle the system.

- b. At the LOM prompt, type poweroff followed by poweron.

# 2.4 POST Diagnostic Levels

Two levels of POST are available: maximum (max) level and minimum (min) level. The system initiates the selected level of POST based on the setting of diag-level, a configuration variable.

The time required to complete POST depends on the CPU configuration and the amount of installed memory. TABLE 2-1 lists the approximate time required to complete the POST for single and dual processor systems with varying memory installed, for diag-level variable settings of max and min.

**TABLE 2-1** POST Completion Times

| CPU and Memory | max setting | min setting |

|----------------|-------------|-------------|

| 2P, 4 Gbyte    | 8 minutes   | 5 minutes   |

| 2P, 1 Gbyte    | 6 minutes   | 4 minutes   |

| 1P, 2 Gbyte    | 7 minutes   | 4 minutes   |

| 1P, 1 Gbyte    | 5 minutes   | 3 minutes   |

The default value for diag-level is min.

# 2.4.1 diag-level Variable Set to max

When the diag-level variable is set to max, POST enables an extended set of diagnostic-level tests. See TABLE 2-1 for approximate completion times.

CODE EXAMPLE E-1 in Appendix E provides an example of the POST output from a system with two 1.2 GHz CPUs and 4 Gbyte of memory, and with the diag-level variable set to max.

# 2.4.2 diag-level Variable Set to min

When the diag-level variable is set to min, POST enables an abbreviated set of diagnostic-level tests. See TABLE 2-1 for approximate completion times.

CODE EXAMPLE E-2 in Appendix E provides an example of the POST output from a system with two 1.2 GHz CPUs and 4 Gbyte of memory, and with the diag-level variable set to min.

# 2.4.3 Error Messages

CODE EXAMPLE 2-3 shows a sample error message at the console:

### **CODE EXAMPLE 2-3** Sample POST Console Error Message

```

Power On Self Test Failed.

Cause: DIMM J0406 or System Board

ok

```

CODE EXAMPLE 2-4 shows a sample error message at the serial port.

### **CODE EXAMPLE 2-4** Sample POST Serial Port Error Message

```

{0} ERROR: TEST=*Memory Initial area TESTID=2

{0} H/W under test=*MAIN MEMORY

{0} Fault address 00000000.00000010

{0} Fault status 00000002.0000004f

{0} (CE) Correctable system data ECC error

{0} CPU data bit 6

{0} Memory data bit 146

{0} DIMM connector J0406

{0} Connector pin 124

{0} CPMS slice 124

```

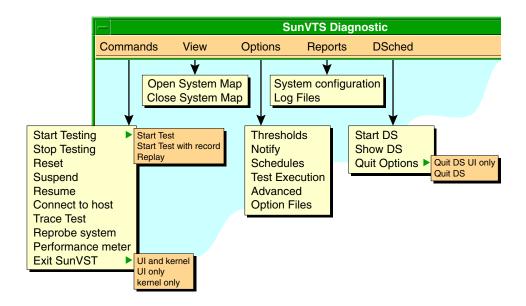

# SunVTS™

This chapter contains an overview of the Sun Validation Test Suite 4.4 (SunVTS) diagnostic tool. You can use SunVTS to validate a system when troubleshooting and during periodic maintenance.

This chapter contains the following topics:

- Section 3.1, "The Validation Test Suite" on page 3-1

- Section 3.1.1, "SunVTS Requirements" on page 3-2

- Section 3.1.2, "SunVTS References" on page 3-2

- Section 3.1.3, "Installation" on page 3-3

- Section 3.1.4, "New and Modified Features and Options" on page 3-3

- Section 3.2, "SunVTS Tests" on page 3-6

# 3.1 The Validation Test Suite

SunVTS Version 4.4 is the Sun online Validation Test Suite supplied with the Netra 20 system.

SunVTS is a comprehensive software diagnostic package that tests and validates hardware by verifying the connectivity and functionality of most hardware controllers, devices, and platforms.

SunVTS can be tailored to run on various types of systems ranging from desktops to servers and has many features that you can customize to meet the varying requirements of differing diagnostic situations.

SunVTS executes multiple diagnostic tests from a graphical user interface (GUI) or TTY interface that provide test configuration and status monitoring.

The SunVTS interface can run on one system to display the SunVTS test session of another system on the network.

SunVTS is distributed with each Solaris release. It is located on the Sun Computer Systems Supplemental CD.

# 3.1.1 SunVTS Requirements

Your system must meet the following requirements to run SunVTS:

- The SunVTS packages must be installed. The main package is SUNWvts. There are additional supporting packages that differ with the revision of the Solaris operating system that is installed. See also Section 3.1.3, "Installation" on page 3-3 and the corresponding SunVTS documentation.

- The system must be booted to the multiuser level (level 3).

- To run SunVTS with a GUI (CDE or Open Look), that GUI must be installed. Otherwise, run SunVTS with the TTY-mode interface.

## 3.1.2 SunVTS References

To find out more information about the using SunVTS, refer to the SunVTS documentation for the Solaris release that you are running.

The SunVTS documents are part of the Solaris on Sun Hardware AnswerBook<sup>TM</sup> collection. This AnswerBook collection is pre installed on the hard disk of new systems. It is also distributed on the Software Supplemental CD that is part of each Solaris Media Kit release and is also accessible at http://docs.sun.com.

The following list describes the contents of each SunVTS document:

- *SunVTS User's Guide* describes how to install, configure, and run the SunVTS diagnostic software.

- SunVTS Test Reference Manual provides details about each individual SunVTS test.

- *SunVTS Programmer's Guide* supports the development of custom tests.

## 3.1.3 Installation

The SunVTS 4.4 software comprises four installation packages:

- SUNWvts—SunVTS kernel, user interface and tests

- SUNWvtsx—SunVTS 64-bit package

- SUNWvtsol—SunVTS user interface

- SUNWvtsmn—SunVTS man pages

For details of the installation procedure, refer to the *Netra 20 Installation and User's Guide*.

# 3.1.4 New and Modified Features and Options

The following additions have been made to support the Netra 20 system:

- Tests have been included for the new components of the hardware platform.

- Remote features enable you to interface to SunVTS from a remote system.

- Multiple user interfaces can monitor and run tests concurrently.

- A test scheduler enables you to specify groups of tests to be conducted in a predefined order. Tests in a group are executed concurrently so that all tests in one group complete before the tests in another group begin.

- A new SunVTS message format displays the information re-ordered and labeled:

```

<timestamp> <hostname> "SunVTS:"[VTSID <vts msgid>]

<modulename> [.<submodulename>] [.<insttnum>].<vts_msgtype>]

[<device_pathname>:] <msg_txt>

```

08/05/01 17:19:47 vrij SunVTS: VTSID 34 disktest. VERBOSE c<br/>0t0d0: "number of blocks 3629760"

## 3.1.4.1 New and Modified Tests and Commands

The following commands have been added to this release of SunVTS.

**TABLE 3-1** New SunVTS Commands

| Command       | Function                                                                                                         |  |

|---------------|------------------------------------------------------------------------------------------------------------------|--|

| testadd       | Adds a test's resource object files to the SunVTS shared object library (contained in the SUNWvtstk package)     |  |

| testrm        | Removes a test's resource object file from the SunVTS shared object library (contained in the SUNWvtstk package) |  |

| testinfo      | Lists all the resource object files from the SunVTS shared object library (contained in the SUNWvtstk package)   |  |

| vts_cmd       | Enables direct control of SunVTS from your program or scripts on a remote machine                                |  |

| connect       | Enables a user interface to connect to a SunVTS kernel on any system on a network                                |  |

| trace         | System call tracing that assists in tracing test flows through the system interfaces                             |  |

| Record/Replay | Enables test sequences and forks to be recorded and replayed to improve failure reproducibility                  |  |

| Reprobe       | Searches and recompiles (reprobes) the system's configuration on demand                                          |  |

**Note** — To add a third party test executable binary, add the test to /opt/SUNWvts/bin/sparcv9, then modify the /opt/SUNWvts/bin/sparc9/.customtest file.

The commands are shown in the SunVTS GUI menus (FIGURE 3-1):

FIGURE 3-1 SunVTS Menu Bar

# 3.1.5 Starting SunVTS

You can start SunVTS in one of four modes, depending on whether you are executing locally or remotely, on a CDE GUI, OpenLook GUI, or in TTY mode:

■ To run SunVTS kernel and default GUI on the local system, type:

```

# cd /opt/SUNWvts/bin

# ./sunvts

```

■ To run SunVTS kernel and OpenLook GUI on the local system, type:

```

# cd /opt/SUNWvts/bin

# ./sunvts -1

```

■ To run SunVTS kernel in TTY mode on the local system, type:

```

# cd /opt/SUNWvts/bin

# ./sunvts -t

```

■ To connect and test a remote system, hostname, but display the GUI on the local host, type:

```

# cd /opt/SUNWvts/bin

# ./sunvts -h

```

**Note** – The latest SunVTS features may not be supported by the SunVTS OpenLook GUI.

# 3.2 SunVTS Tests

This section lists the tests available in SunVTS 4.4. Some tests have been modified and new tests have been added to support the Netra 20 hardware platform.

**TABLE 3-2** SunVTS Processor Tests

| Test         | Function                                                                                                                                                                                                  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cputest      | This new test checks the specific functionality of the SPARC processor data path, including:                                                                                                              |

|              | <ul><li>g0 register functionality</li><li>Compress/Uncompress/Compare command</li></ul>                                                                                                                   |

| Legacy Tests | These include:                                                                                                                                                                                            |

|              | <ul> <li>systest—tests the I/O, memory and CPU channels</li> <li>fputest—tests the floating point unit</li> <li>mptest—tests two or more processors by having them access a shared memory page</li> </ul> |

**TABLE 3-3** SunVTS Memory Tests

| Test         | Function                                                                                                                                                                                              |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Legacy Tests | These include:                                                                                                                                                                                        |

|              | <ul> <li>pmemtest—tests the physical memory by targeting parity, ECC, memory read, and addressing problems</li> <li>vmemtest—tests the virtual memory and the swap partitions of the disks</li> </ul> |

TABLE 3-4

SunVTS Storage Device Tests

| Test         | Function                                                                                                                                                                            |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| dvdtest      | This new test checks the DVD-R drive by reading the DVD.                                                                                                                            |

| qlctest      | This new test checks the ISP2200A FC-AL controller. The sub tests include:                                                                                                          |

|              | <ul> <li>Revision checks</li> <li>Internal loopback tests</li> <li>External loopback tests (require external loopback cable)</li> </ul>                                             |

| Legacy Tests | These include:                                                                                                                                                                      |

|              | <ul> <li>cdtest—tests the CD-ROM drive by reading the CD</li> <li>tapetest—tests tape devices by writing, reading and verifying synchronous and asynchronous data blocks</li> </ul> |

TABLE 3-5

SunVTS Network Tests

| Test      | Function                                                                                                                         |

|-----------|----------------------------------------------------------------------------------------------------------------------------------|

| net1btest | This new test checks the ERI and GEM Ethernet controllers by performing internal and external loopback tests (replaces gemtest). |

| nettest   | This system-to-system legacy test covers all networking devices found in the system.                                             |

TABLE 3-6

SunVTS Communications Port Tests

| Test         | Function                                                                                                   |

|--------------|------------------------------------------------------------------------------------------------------------|

| usbkbtest    | This new test covers the keyboard and mouse.                                                               |

| Legacy Tests | These include:                                                                                             |

|              | <ul><li>sptest—tests the serial sync. and async. ports</li><li>ecpptest—tests the parallel ports</li></ul> |

**TABLE 3-7** SunVTS Custom Test

| Test      | Function                                                     |

|-----------|--------------------------------------------------------------|

| cpupmtest | This new test checks the CPU power management functionality. |

**Note** – Test failures occur if you run nettest and netlbtest simultaneously.

# 3.2.1 Guide to Using SunVTS 4.4

The following guidance notes points are included to help you use SunVTS 4.4.

- The packages SUNWeswsa, SUNWsycfd, SUNWesnta and SUNWeswgn are no longer required or supplied for physical mapping support.

- The disktest probe does not premount any partitions by default. You can set the environment variable BYPASS\_FS\_PROBE to zero to force all unmounted partitions to premount.

- Premounting will not take place, even if you have enabled it, if the disktest probe detects the presence of Veritas or Solstice DiskSuite.

- If you run a media subtest on a disk partition in WriteRead mode, data corruption can occur if the partition is shared with other programs.

- An option file created when BYPASS\_FS\_PROBE was set to 0 may not load when BYPASS\_FS\_PROBE is set to 1. If required, create option files for both states of BYPASS\_FS\_PROBE

- SunVTS (Kerebos SEAM) security is now on by default. To turn security off, edit the security file /opt/SUNvts/bin/.sunvts to include a "+" in the HOST section. This will make all the listed hosts *trusted* hosts.

- Physical mapping is supported only on systems that support configd.

- Do not mix CDE and OpenLook environments.

- The files .customtest and .customtest\_OtherDevices are separate files in the 64-bit version of SunVTS. They are installed in /opt/SUNWvts/bin/spacv9, and not /opt/SUNWvts/bin as is the case for the 32-bit version.

- The environment variable VTS\_PM\_PATH is used to locate the pix map files when SunVTS is not installed in the default base directory (/opt).

- The following tests have been renamed:

- spif -> spiftest

- pmem -> pmemtest

- vmem -> vmemtest

- The following tests are not supported in 64-bit mode:

- cg14test

- isdntest

- tcxtest

- The physical map view displays only one level of the hierarchy. To view the complete hierarchy, use the logical view.

# Troubleshooting

This chapter describes how to troubleshoot possible hardware problems and suggests corrective actions.

This chapter contains the following topics:

- Section 4.1, "Power-On Failure" on page 4-2

- Section 4.2, "System LEDs" on page 4-2

- Section 4.3, "Drive Failure" on page 4-2Section 4.3, "Drive Failure" on page 4-2

- Section 4.4, "Power Supply Unit Troubleshooting" on page 4-4

- Section 4.5, "OpenBoot PROM Diagnostics" on page 4-7

- Section 4.6, "OpenBoot Emergency Procedures" on page 4-30

**Caution** – Regardless of the position of the ON/STBY switch, when an AC power cord remains connected to the system, hazardous voltage is always present within the power supply.

**Caution** – Wear an antistatic wrist strap and use an ESD-protected mat when handling components. When servicing or removing system unit components, use an antistatic wrist strap with a 10 mmpress stud connection and attach the antistatic wrist strap to the press stud at the rear or front of the chassis before removing the top access cover.

**Caution** – Owing to the weight of the unit, two persons are required to remove the unit from and replace it in the rack.

# 4.1 Power-On Failure

This section provides examples of power-on failure symptoms and suggested actions.

## Symptom

The system does not power up when you press the ON/STBY switch.

### Action

- Ensure that a PSU is installed and properly seated. Check that the three PSU fixing screws have been tightened.

- Ensure that the AC power cord is properly connected to the system and to the wall socket. Verify that the wall socket is supplying AC power to the system.

- Press the ON/STBY switch. If the system does not power on, the CPU module(s) may not be properly seated. Inspect the CPU module(s) for proper seating, and press the ON/STBY switch again.

- If the AC power wall socket is live and the CPU module(s) are properly seated, but the system does not power on, the PSU may be defective. Check the status of the PSU LEDs and see Section 4.4, "Power Supply Unit Troubleshooting" on page 4-4.

# 4.2 System LEDs

The system LEDs located on the front and rear system panels provide information about the status of the system and many of its subsystems. Refer to Section 1.4, "LEDs" on page 1-6 for a description of their function.

# 4.3 Drive Failure

This section provides hard drive, DVD-ROM and DAT drive failure symptoms and suggested actions.

## Symptom

A hard drive read, write, or parity error is reported by the operating environment or customer application.

A DVD-ROM or DAT drive read error or parity error is reported by the operating environment or customer application.

### Action

Replace the drive indicated by the failure message. The operating environment identifies the internal drives, as listed in TABLE 4-1.

**TABLE 4-1** Internal Drives Identification

| Operating Environment Address                  | Drive Physical Location and Target |

|------------------------------------------------|------------------------------------|

| c1t0d0s# <sup>1</sup> c0t0d0s# <sup>1</sup>    | Left hard drive, LiD/HA 1          |

| c1t1d0s# <sup>1</sup><br>c0t1d0s# <sup>1</sup> | Right hard drive, LiD/HA 2         |

| c0t6d0s#                                       | DVD-ROM drive, target 6 (optional) |

| c0t5d0s#                                       | DAT drive, target 5 (optional)     |

<sup>1.</sup> The controller number will be c1 if a CDROM or DAT drive is installed and c0 if no CDROM or DAT drive is installed.

**Note** – The # symbol in the operating environment address examples is a numeral between 0 and 7 that describes the slice or partition on the drive.

## Symptom

The DVD-ROM drive fails to respond to commands.

### Action

Test the drive response to the probe-scsi command as follows.

Note - To bypass POST, type setenv diag-switch? false at the ok prompt.

At the OBP ok prompt, type:

```

ok reset-all

ok probe-scsi-all

```

If the DVD-ROM drive responds correctly to probe-scsi-all, the message identified in CODE EXAMPLE 4-2 is displayed; the system SCSI controller has successfully probed the device. This is an indication that the motherboard is operating correctly. If the drive does not respond to the SCSI controller probe, replace the unresponsive drive.

# 4.4 Power Supply Unit Troubleshooting

**Caution** – During the power supply voltage measurement checks, an operational load must be on the power supply. Ensure that the power supply cables remain connected to the motherboard.

The section describes how to use a digital volt meter (DVM) to test the power supply under operational load. See the figures and tables in this section to identify the J3601 and J3603 power connectors.

1. Power off the system and remove the top access panel.

See Chapter for details.

**Caution** – Use proper ESD grounding techniques when handling components. Wear an antistatic wrist strap and use an ESD-protected mat. Store ESD-sensitive components in antistatic bags before placing them on any surface. See Section 5.5, "Antistatic Precautions" on page 5-5.

**Caution** – Hazardous voltages are present. To reduce the risk of electrical shock and danger to personal health, follow the instructions.

- 2. Check the continuity of the power cables between the PDB and motherboard.

- 3. Ensure that the PSU is correctly located in the chassis and that the fixing screws are fully tightened.

- 4. Check the PSU LEDs (see Section 1.4.3, "PSU LEDs" on page 1-11) to verify the status of the PSU.

- 5. Check that the power cable connectors are properly seated at the PDB and motherboard.

- 6. Power on the system.

- 7. Using a DVM, check the power supply output voltages.

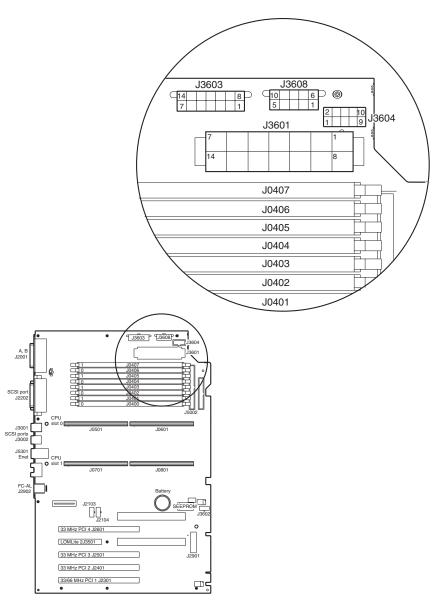

See FIGURE 4-1 for the power supply connector location on the motherboard.

**Note** – All power supply connectors being tested must remain connected to the motherboard and PDB.

- a. With the negative probe of the DVM placed on a connector ground (GND) pin, position the positive probe on each power pin.

- b. Verify voltage and signal availability as listed in the voltage-pin tables.

- 8. If any power pin signal is not present with the power supply active, and the power cables between the PDB and motherboard properly connected, replace the power supply.

FIGURE 4-1 Power Supply Connector Jack Location

TABLE 4-2

J3601 Voltage-Pin Assignments

| Pin | Voltage | Pin | Voltage |

|-----|---------|-----|---------|

| 1   | 0 V     | 8   | +5 V    |

| 2   | -12V    | 9   | n/a     |

| 3   | 0 V     | 10  | +5 V    |

| 4   | 0 V     | 11  | +3.3 V  |

| 5   | 0 V     | 12  | +12V    |

| 6   | 0 V     | 13  | +12V    |

| 7   | n/a     | 14  | +5 V    |

TABLE 4-3

J3603 Voltage-Pin Assignments

| Pin | Voltage | Pin | Voltage |  |

|-----|---------|-----|---------|--|

| 1   | +3.3 V  | 8   | 0 V     |  |

| 2   | +3.3 V  | 9   | 0 V     |  |

| 3   | +3.3 V  | 10  | 0 V     |  |

| 4   | +3.3 V  | 11  | 0 V     |  |

| 5   | +5 V    | 12  | 0 V     |  |

| 6   | +5 V    | 13  | 0 V     |  |

| 7   | +5 V    | 14  | 0 V     |  |

# 4.5 OpenBoot PROM Diagnostics

The following sections describe the OpenBoot PROM diagnostics. To execute the OpenBoot PROM on-board diagnostics, the system must be at the ok prompt.

- Section 4.5.1, "New Features" on page 4-8

- Section 4.5.2, "New and Modified Commands and Tests" on page 4-9

- Section 4.5.3, "Device Tree" on page 4-14

- Section 4.5.4, "Running the Diagnostics" on page 4-18

## 4.5.1 New Features

This section summarizes the features supported in OpenBoot 4.2 that are not covered in the *OpenBoot 3.x Command Reference Manual* (part no. 806-1377) and the *OpenBoot 3.x Quick Reference* (part no. 806-2908).

- Universal Serial Bus (USB)

- FC-AL drive support

- New device driver support for:

- PCI prober

- I2C

- USB

- NVRAM

- FC-AL

- ERI

- Safari Giga Plane Two (gptwo) support

- Autoconfiguration

- Flash PROM (2MByte) divided into quadrants

- Quadrant 0—Sun Blade<sup>TM</sup> 1000 OBP—Start address 0

- Quadrant 1—Sun Fire<sup>TM</sup> E280R OBP/Netra 20 OBP—Start address 512k

- Quadrant 2—POST (shared)—Start address 1.0M

- Quadrant 3—OBDiag (shared)—Start address 1.5M

- Flash updates replace two quadrants at a time

- Quadrant 0 and 1

- Ouadrant 2 and 3

- Support for:

- Stop-A

- Stop-A on ttya (#)

- Stop-N (emulated by lom> bootmode reset\_nvram))

- Stop-F (emulated by lom> bootmode forth)

- Stop-D (emulated by lom> bootmode diag)

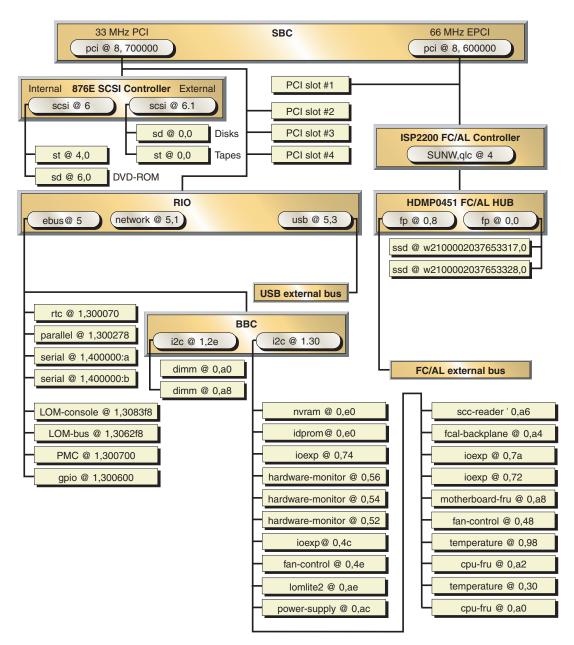

### PCI Buses

Two PCI buses are implemented that are fully independent in terms of address and data paths, channel engines, gptwo memory physical address space, I/O physical address space and configuration space. As the device space is not shared between the two PCI buses, you must access the specific PCI node to view its properties.

### Flash PROM

The flash PROM is divided into quadrants that are dedicated to Sun Blade 1000 OBP, Sun Fire E280R OBP/Netra 20 OBP, POST and OBDiag, respectively. A flash update involves two quadrants, either 0 and 1, or 2 and 3. You can download the quadrants from a standalone utility, bootable DVD-ROM, or from the network. The updates are available in binary or UNIX shell formats.

During a flash PROM update, the OBP firmware overwrites the upper half of PROM (where POST resides), keeping the original OBP unchanged. After the new OBP is tested successfully, the original OBP is overwritten with the new OBP. Finally, after the OBP is tested again, POST is reloaded into the upper half of PROM.

### OBP Prompt

On dual processor systems, the OBP prompt includes the CPU number:

{0} ok

#### Resets

When the system is first powered up, the configuration is determined using information stored in the motherboard and CPU EEPROMS (CPU speed, memory configuration, and so forth) and is saved in the BootBus Controller (BBC) SRAM. This is termed a *Configuration Reset*. Subsequent system power cycles generate a configuration reset.

A *Soft Reset* occurs on subsequent system resets, which uses the BBC's SRAM configuration information. To avoid booting with corrupted configuration information, a checksum is performed on the data. If the data is found to be corrupt, the subsequent reset reverts to a configuration reset.

## 4.5.2 New and Modified Commands and Tests

The probe and test commands have been modified to include FC-AL and USB keyboard and mouse, respectively, as shown in TABLE 4-4:

TABLE 4-4 probe and test Commands

| Command        | New Features                                                |

|----------------|-------------------------------------------------------------|

| probe-scsi     | Identifies the devices attached to the FC-AL buses          |

| probe-scsi-all | Identifies all devices attached to all SCSI and FC-AL buses |

| test-all       | Includes all tests                                          |

## 4.5.2.1 probe-scsi and probe-scsi-all

The probe-scsi diagnostic transmits an inquiry command to internal and external FC-AL and SCSI devices connected to the system on-board SCSI or FC-AL interface. If the SCSI device is connected and active, the target address, unit number, device type, and manufacturer name are displayed.

The probe-scsi-all diagnostic transmits an inquiry command to all devices connected to the system. The first identifier listed in the display is the SCSI host adapter address in the system device tree followed by the SCSI device identification data.

Initiate the probe-scsi diagnostic by typing the probe-scsi command at the ok prompt and initiate the probe-scsi-all diagnostic by typing the probe-scsi-all command at the ok prompt.

To perform a probe command, at the ok prompt, ensure that autoboot? is set to false, then perform a reset-all.

The following code examples identify the probe-scsi and the probe-scsi-all diagnostic output messages.

#### CODE EXAMPLE 4-1 probe-scsi Diagnostic Output Message

```

ok probe-scsi

LiD HA --- Port WWN --- ---- Disk description ----

1 1 210000203700ca78 SEAGATE ST39103FCSUN9.0G01479916021084

3 3 210000203708ad4d SEAGATE ST39102FCSUN9.0G09299906F45038

ok

```

### CODE EXAMPLE 4-2 probe-scsi-all Output Message

## 4.5.2.2 test alias name, device path, -all

The test diagnostic, combined with a device alias or device path, enables a device self-test program. If a device has no self-test program, the message No selftest method for device name is displayed. To enable the self-test program for a device, type the test command, followed by the device alias or device path name.

The following code example identifies the test output message. TABLE 4-5 lists test *alias name* selections, their descriptions, and their required preparation.

### **CODE EXAMPLE 4-3** Test Output Message

```

ok test net

Testing net

```

TABLE 4-5

Selected OpenBoot PROM On-Board Diagnostic Tests

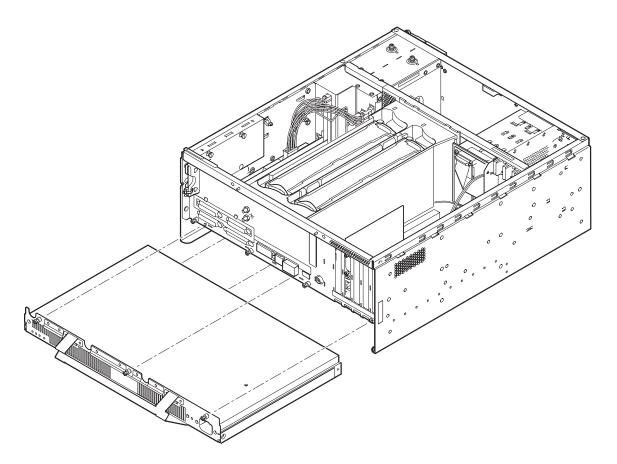

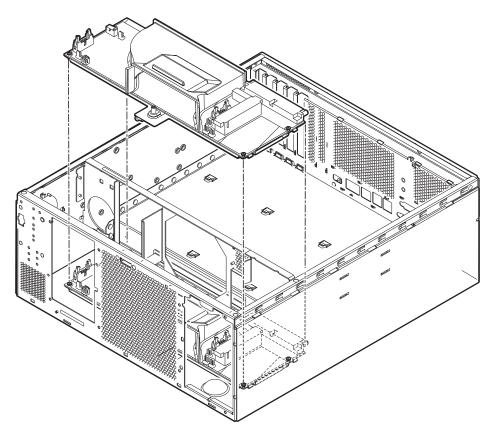

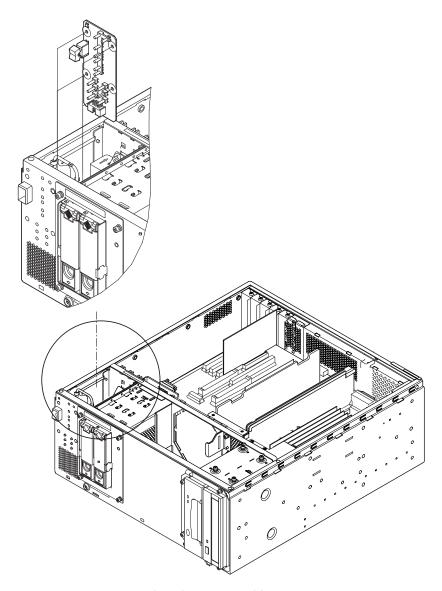

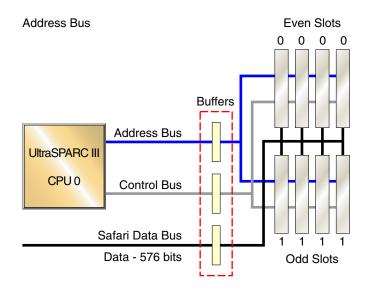

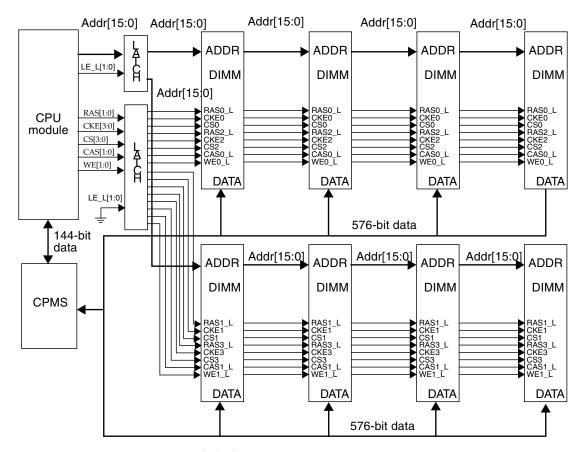

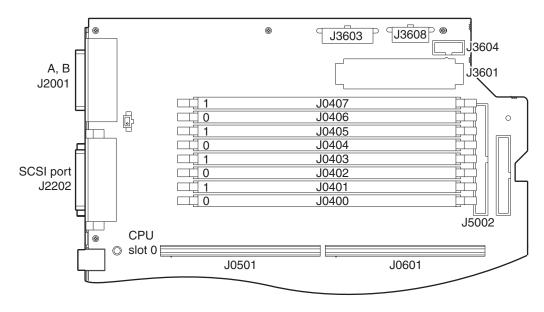

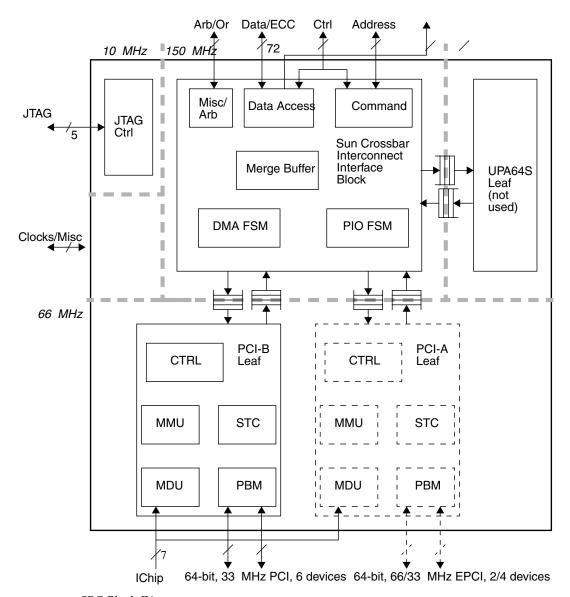

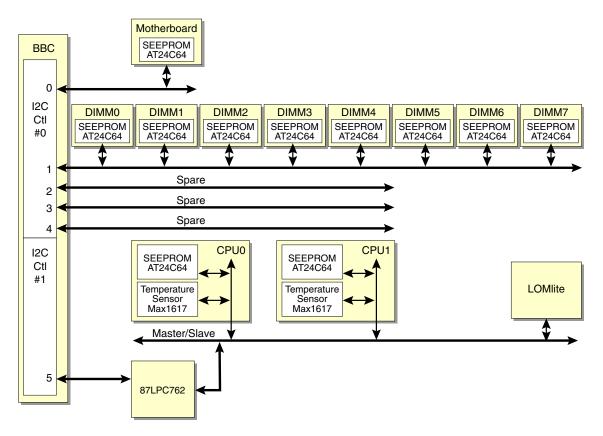

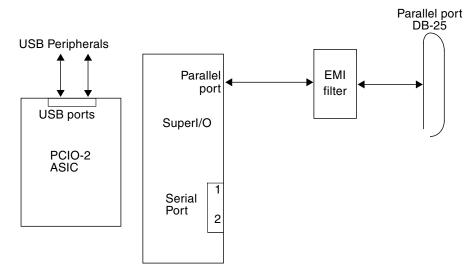

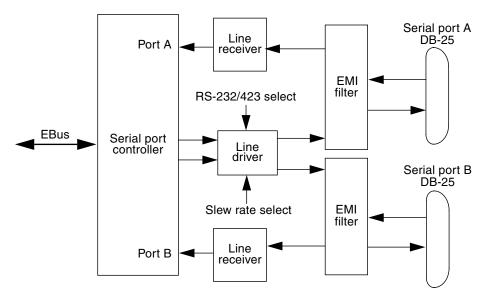

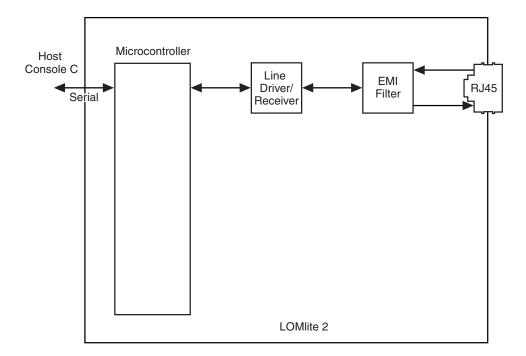

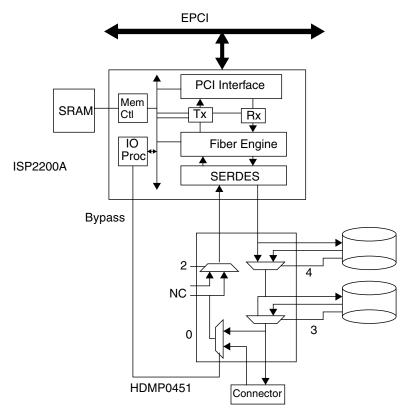

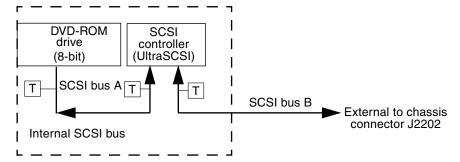

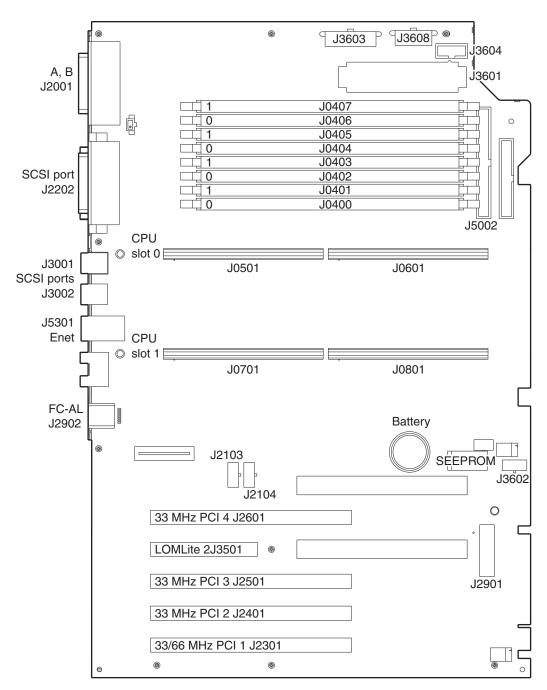

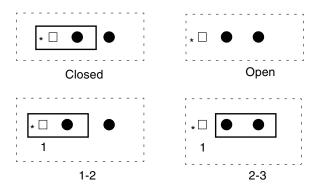

| Type of Test | Description                                                                              | Preparation                                                                                                                                                           |