# COMPAQ PCI Development Platform Reconfigurable Hardware Device for the PCI Bus

# User's Guide

Part Number: EK-PAMP1-UG. B01

September 1999

#### September 1999

The information in this publication is subject to change without notice.

COMPAQ COMPUTER CORPORATION SHALL NOT BE LIABLE FOR TECHNICAL OR EDITORIAL ERRORS OR OMISSIONS CONTAINED HEREIN, NOR FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES RESULTING FROM THE FURNISHING, PERFORMANCE, OR USE OF THIS MATERIAL. THIS INFORMATION IS PROVIDED "AS IS" AND COMPAQ COMPUTER CORPORATION DISCLAIMS ANY WARRANTIES, EXPRESS, IMPLIED, OR STATUTORY, AND EXPRESSLY DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR PARTICULAR PURPOSE, GOOD TITLE, AND AGAINST INFRINGEMENT.

This publication contains information protected by copyright. No part of this publication may be photocopied or reproduced in any form without prior written consent from Compaq Computer Corporation.

© Compaq Computer Corporation 1999. All rights reserved.

The software described in this guide is furnished under a license agreement or nondisclosure agreement. The software may be used or copied only in accordance with the terms of the agreement.

Compaq and Compaq logo are registered in the United States Patent and Trademark Office.

Windows NT is a trademark of Microsoft Corporation. Intel is a registered trademark of Intel Corporation. Xilinx is a trademark of XILINX, Inc.

# **Table of Contents**

| Preface                                               |      |

|-------------------------------------------------------|------|

| Organization                                          | vii  |

| Conventions                                           |      |

| Getting Help                                          | viii |

| Compaq Worldwide Web Server                           | viii |

| Compaq FTP Server                                     |      |

| Compaq Internet Site                                  |      |

| PAQFAX                                                |      |

| Calling the Compaq Support Line                       |      |

| Before You Call                                       | ix   |

| 1 Introduction                                        |      |

| 1.1 General                                           | 1–1  |

| 1.2 Operating System Support                          |      |

| 1.3 Platform Support                                  |      |

| 1.4 Differences between Firmware v2.0 and v1.10       | 1–1  |

| 2 System Overview                                     |      |

| 2.1 Hardware                                          | 2–1  |

| 2.1.1 PCI to User Area Interface FPGA                 |      |

| 2.1.2 SROM and EEPROM                                 |      |

| 2.1.3 User-Area FPGA                                  | 2–2  |

| 2.1.4 SRAM and DRAM                                   | 2–2  |

| 2.1.5 Clocking Circuitry: System Clock and User Clock | 2–3  |

| 2.1.6 Mezzanine Cards                                 | 2–3  |

| 2.1.7 DMA Engine                                      | 2-3  |

| 2.2 Software                                          | 2-3  |

| 2.2.1 Device Driver                                   | 2–4  |

| 2.2.2 Related Software                                |      |

| 2.3 Updates                                           | 2–4  |

| 3 Configuration and Installation                      |      |

| 3.1 Hardware Configuration                            | 2 1  |

| 3.1.1 Failsafe Jumper                                 |      |

| 3.1.1 Fansare Jumper  3.2 Hardware Installation       |      |

| 5.2 Hardware Histalianon                              | 1–را |

| 4 Software Installation                               |      |

| 4.1 Introduction                                      | 4–1  |

|   | 4.2 TRU64 UNIX Software Kit Installation     |            |     |

|---|----------------------------------------------|------------|-----|

|   | 4.2.1 Deleting Old Device Driver Revisions   |            |     |

|   | 4.2.2 Installing the Kit                     | 4-         | -2  |

|   | 4.2.3 File List                              | 4-         | -4  |

|   | 4.2.4 Rebuilding the Kernel                  | 4-         | -5  |

|   | 4.3 Windows NT Software Installation         | 4-         | -5  |

|   | 4.3.1 Installing the Software                | 4-         | -5  |

|   | 4.3.2 Deleting old NT Software Revisions     | 4-         | -5  |

|   | 4.4 Installation Verification Procedure      | 4-         | -5  |

|   | 4.4.1 PamTest                                | 4-         | -5  |

|   | 4.4.2 SRAM Test                              | 4-         | -7  |

|   |                                              |            |     |

| _ | Module Architecture                          |            |     |

| J |                                              |            |     |

|   | 5.1 Introduction                             | 5-         | -1  |

|   | 5.2 PCI Interface to User-Area Connections   | 5-         | -2  |

|   | 5.2.1 EBus                                   | 5-         | -2  |

|   | 5.2.2 Rings                                  | 5-         | -2  |

|   | 5.3 Clocks                                   |            |     |

|   | 5.4 SRAM                                     |            |     |

|   | 5.5 DRAM                                     |            |     |

|   | 5.6 Mezzanine Connectors                     |            |     |

|   |                                              |            |     |

| c | Address Man                                  |            |     |

| O | Address Map                                  |            |     |

|   | 6.1 Introduction                             | 6-         | -1  |

|   |                                              |            |     |

| _ | DMA Forder                                   |            |     |

| 1 | DMA Engine                                   |            |     |

|   | 7.1 Introduction                             | 7_         | -1  |

|   | 7.2 DMA Address Register: 0x2000             |            |     |

|   | 7.3 DMA Command Register: 0x2000+8           |            |     |

|   | 7.4 Simultaneous Initiator and Target        |            |     |

|   | 7.1 Simulation out interest and ranger       |            |     |

|   |                                              |            |     |

| 8 | Interface Modes                              |            |     |

|   | 8.1 Introduction                             | 8-         | -1  |

|   | 8.2 Static Mode                              |            |     |

|   | 8.2.1 Coding guidelines for host software    |            |     |

|   | 8.2.2 Static Mode and Clkusr.                |            |     |

|   | 8.3 Promiscuous Mode                         |            |     |

|   | 8.4 PromiscuousTransaction Mode              |            |     |

|   | 8.5 Transaction Mode                         |            |     |

|   | 8.5.1 Target Transactions                    |            |     |

|   | 8.5.2 Master Transactions                    |            |     |

|   | 8.5.2.1 MSTR/AUI.                            |            |     |

|   | 8.5.2.2 MSTR/AIU                             |            |     |

|   | 8.5.3 Requests from User-area.               |            |     |

|   | 8.5.3.1 Bus Contention and AIF Cycles        |            |     |

|   | 8.5.3.2 Request Codes                        |            |     |

|   | 8.5.3.3 Link Register in Transaction Mode    | ا—ن<br>1 ک | . Z |

|   | 8.5.4 64-bit Transaction mode                |            |     |

|   | 8.5.5 Interrupts                             |            |     |

|   |                                              |            |     |

|   | 8.5.5.1 End of DMA Interrupt                 |            |     |

|   | 8.5.5.2 User Interrupt in the Link Register  |            |     |

|   | 8.5.5.3 User Interrupt Using the Ring Bits   |            |     |

|   | 8.5.6 Hardware controlled stopping of Clkusr | Q 1        | 7   |

# 9 Security Considerations

| 9.1 Introduction                                         | 9–1      |

|----------------------------------------------------------|----------|

| 0 Software                                               |          |

| 10.1 Run-time Libraries                                  | 10–1     |

| 10.1.1 PamRT.h                                           |          |

| 10.1.1.1 PamOpen                                         |          |

| 10.1.1.2 PamClose                                        |          |

| 10.1.1.3 PamDownloadBitstream                            |          |

| 10.1.1.4 PamDownloadFile                                 |          |

| 10.1.1.5 PamSetMode                                      |          |

| 10.1.1.6 PamSetModeAndDelay                              |          |

| 10.1.1.7 PamClockOn                                      |          |

| 10.1.1.8 PamClockOff                                     |          |

| 10.1.1.9 PamClockStep                                    | 10–5     |

| 10.1.1.10 PamWriteWord                                   |          |

| 10.1.1.11 PamReadWord                                    |          |

| 10.1.1.12 PamFlush                                       |          |

| 10.1.2 PamState.h                                        | 10–7     |

| 10.1.2.1 PamLcaStateTable                                |          |

| 10.1.2.2 PamStateCLB                                     | 10–7     |

| 10.1.2.3 PamStateIOB                                     | 10–8     |

| 10.1.2.4 PamStateIsRam                                   | 10–8     |

| 10.1.2.5 PamStateLUT                                     |          |

| 10.1.3 PamFriend.h                                       | 10–10    |

| 10.1.3.1 PamFindBoard                                    | 10–10    |

| 10.1.3.2 PamReadInfo                                     | 10–10    |

| 10.1.3.3 PamRegisterLayout                               | 10–11    |

| 10.1.3.4 PamResetAll                                     | 10–11    |

| 10.1.3.5 PamDownloadLcas                                 |          |

| 10.1.3.6 PamReadBackMinLength                            | 10–12    |

| 10.1.3.7 PamReadBackBitstream                            |          |

| 10.1.3.8 PamSetClockSpeed                                | 10–13    |

| 10.1.3.9 PamClockPeriod                                  | 10–14    |

| 10.1.3.10 PamWaitClock                                   | 10–14    |

| 10.2 PAM Register Declaration                            | 10–14    |

| 1 Command Line Controls                                  |          |

| 11.1 Introduction                                        | 11_1     |

| 11.2 PamTest                                             |          |

| 11.3 Mergebit                                            |          |

| 11.4 Prom (ppam_prom for TRU64 UNIX)                     | 11_4     |

| 11.5 PamControl                                          |          |

| 11.6 Pciperf (ppam_pciperf for TRU64 UNIX)               | 11–4     |

|                                                          | 11       |

| 2 Restoring Original PCI Interface Design or Upgrading I | Firmware |

| 12.1 Introduction                                        | 12–1     |

# A Major User Buses/Pins

## **B Special Purpose/Restricted Use Pins**

### **C PAM Driver Interfaces for TRU64 UNIX**

### **D PAM Driver Interfaces for Windows NT**

## **E Register Definitions**

## **Glossary**

## **Figures**

| Figure 5-1 PCI Development Platform Module Architecture                | 5–1 |

|------------------------------------------------------------------------|-----|

| Figure 5-2 EBus Connections                                            | 5–2 |

| Figure 5-3 Ring Bus                                                    | 5–3 |

| Figure 5-4 Clocks                                                      |     |

| Figure 5-5 SRAM Banks                                                  | 5–5 |

| Figure 5-6 DRAM                                                        | 5–5 |

| Figure 5-7 Mezzanine Connectors                                        |     |

| Figure 8-1 Static Mode Link Register                                   | 8–2 |

| Figure 8-2 Bit Flow in Transaction Mode                                | 8–5 |

| Tables                                                                 |     |

| Table 2-1 PCI Development Platform Software                            | 2–3 |

| Table 8-1 Promiscuous Mode Bit Assignments                             |     |

| Table 8-2 State Codes                                                  |     |

| Table A-1 Major PCI Development Platform User Buses/Pins               |     |

| Table B-1 PCI Development Platform Special Purpose/Restricted Use Pins |     |

## **Preface**

#### Overview

The COMPAQ PCI Development Platform Reconfigurable Hardware Device for the PCI Bus User's Guide describes hot to install and configure the PCI Development Platform reconfigurable hardware module.

## **Organization**

This guide is organized as follows:

**Chapter 1** provides an introduction to the PCI Development Platform reconfigurable hardware module.

Chapter 2 provides an overview of the hardware, device driver, software, and updates.

Chapter 3 describes the hardware installation and configuration.

**Chapter 4** describes the PCI Development Platform software kit installation.

**Chapter 5** provides information on the physical design of the PCI Development Platform module.

**Chapter 6** describes the PCI Development Platform module address map.

Chapter 7 describes the PCI Development Platform module DMA engine.

**Chapter 8** provides information on the supported interface modes.

**Chapter 9** contains information on security considerations.

Chapter 10 describes the run-time library functions.

**Chapter 11** describes the command line tools for controlling the PCI Development Platform module and other utilities in the software package.

Chapter 12 provides information on restoring the original PCI interface design.

**Appendix A** contains a table listing the major user signal buses along with pin connections and their use.

**Appendix B** contains a table listing the special purpose/restricted use signals along with the pin connections present, their special use, and restrictions for user application.

**Appendix** C describes the PAM driver interfaces for TRU64 UNIX.

Appendix D describes the PAM driver interfaces for Windows NT.

**Appendix E** describes the registers in the PCI interface.

### Conventions

This document uses the following conventions:

| Convention                                                                                                              | Meaning                                                                                                         |  |  |

|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|

| Note                                                                                                                    | A note calls the reader's attention to any item of information that may be of special importance.               |  |  |

| <b>Caution</b> A caution contains information essential to avoid damage to the equipment.                               |                                                                                                                 |  |  |

| Warning                                                                                                                 | rning A warning contains information essential to the safety of personnel.                                      |  |  |

| Italic type Italic type emphasizes important information, indicates variables, and indicate complete titles of manuals. |                                                                                                                 |  |  |

| <b>Bold type</b> Bold type indicates text that is highlighted for emphasis.                                             |                                                                                                                 |  |  |

| Monospaced                                                                                                              | In text, this typeface indicates the exact name of a command, routine, partition, pathname, directory, or file. |  |  |

#### Note

The TRU64 UNIX commands used in this manual are case sensitive and must be entered as shown.

The PCI Development platform is also referred to as Pamette. This is can been seen in the source code and some of the software commands.

## **Getting Help**

You can reach Compaq automated support services 24 hours a day, every day, at no charge. The services contain the most up-to-date information about Compaq products. You can access installation instructions, troubleshooting information, and general product information from the Compaq World Wide Web server or from the Compaq FTP server.

## **Compaq Worldwide Web Server**

http://www.compaq.com/support

Navigate to a specific product, then look for support information from this list of supported resources.

# **Compaq FTP Server**

ftp.compaq.com

Navigate to the following for a complete list of available Softpaq files:

ftp.compaq.con/pub/softpaq/allfiles.html

## **Compaq Internet Site**

Send e-mail to:

Support@compaq.com

#### **PAQFAX**

To use fax-on-demand system, you must be in North America and you must have a fax machine or fax modem to receive the automated fax transmittals.

To use the fax-based information retrieval system that provides product-specific information, call 1-800-354-1518, option 1, and request a product catalog. When you receive it, call and order documents you wish to receive.

## **Calling the Compaq Support Line**

Compaq has technical support centers worldwide. Many of the centers are staffed by technicians who speak the local languages. For a list of Compaq support centers to go:

http://www.compaq.com

From the Compaq Welcome page, select your country, then select Support.

#### **Before You Call**

Before call the Compact Support Line, have the following information ready:

- Your address and telephone number

- A description of the failure

- A description of any action(s) already taken to resolve the problem (e.g., changing mode switches, rebooting the unit, etc.)

- A description of your network environment (layout, cable type, etc.)

- Network load and frame size at the time of trouble (if known)

- The device history

Customers may receive product support as follows:

- In North America, call Technical Support at 1-800-354-9000

- In Europe, the Middle East, and Africa, contact Compaq at <a href="http://www.compaq.com">http://www.compaq.com</a> or refer to the following table for the Technical Support numbers for your specific country:

| Country                             | Phone Number   | FAX Number       |

|-------------------------------------|----------------|------------------|

| Austria                             | 01-546521552   | 01-878-1682      |

| Belgium                             | 078/155.500    | (32) 070/222.080 |

| Denmark                             | 4590-4545      | 4590-4595        |

| Fom;amd                             | 0961 55 98 00  | 09-6155-9899     |

| France                              | 0803-81-38-23  | 01-41-33-44-31   |

| Germany                             | 0180-5212-111  | 0180-5212-117    |

| Italy                               | 02 48 23 00 23 | 02 48 23 00 02   |

| Netherlands                         | 0900-1681-616  | 0900-8991-116    |

| Norway                              | 22 07 20 20    | 22 07 20 21      |

| Portugal                            | 1 4128460      | 1 4120654        |

| Spain                               | 09 02 20 24 00 | 091 590 9333     |

| Sweden                              | 08-7030150     | 08 703 5222      |

| Switzerland                         | 01 838 22 22   | 01 836 44 06     |

| UK                                  | 0990-561643    | 0171-744 0068    |

| Ireland (01) 214-1407 (0)1-214-1251 |                | (0)1-214-1251    |

## Introduction

#### 1.1 General

This document describes the installation and use of the PCI Development Platform reconfigurable hardware module.

The PCI Development Platform module is a reconfigurable hardware device comprised of five Xilinx Field Programmable Gate Arrays (FPGAs). One FPGA controls the PCI bus interface while the other four are available for user configuration. The module also contains SRAM and four DRAM connectors that can be utilized at the user's discretion.

This document describes the following:

- Hardware architecture and functionality

- Installing the PCI Development Platform module

- Installing and configuring the device driver

- Configuring the user area gate arrays

- Support software

## 1.2 Operating System Support

The PCI Development Platform reconfigurable hardware module is supported on version 4.0 or higher of TRU64 UNIX or version 4.0 or higher of Windows NT. The Windows NT version is compatible with Intel and Alpha based systems, while the TRU64 UNIX version is for Alpha systems only.

## 1.3 Platform Support

The PCI Development Platform reconfigurable hardware module is supported on the TRU64 UNIX (Alpha) platform and the Windows NT (Alpha and Intel) platform with a PCI-compliant 32-bit or 64-bit bus and a free full-size PCI slot. Refer to the Software Product Information for the specific platforms that are supported.

#### 1.4 Differences between Firmware v2.0 and v1.10

For readers already familiar with firmware v1.10, the principal new features in v2.0 are:

- User configurable delay between address and first data on AUI type transactions (See 8.5)

- Ability to read and write the Rings from software (See 8.5.5.3).

- Ability to stop the user clock under hardware control from user-area (See 8.5.6).

- Ability to accept and generate 64-bit PCI transactions in Transaction mode from the userarea (See 8.5.4).

- New simplified methods to raise PCI interrupts from user-area (See 8.5.5).

- Ability to detect partial word writes in Transaction mode through an interrupt (See 8.5.5).

- Ability to detect loss of PLL lock through an interrupt (See 8.5.5)

- A new Promiscuous mode which mimics the PCI-side timing of Transaction mode (See

- More control bits are included in data transmitted to the user-area in Promiscuous mode (See 8.3).

- Ability to disable address stepping on PCI transactions initiated by PCI Development platform (See 9).

- Wait states introduced by the other party in a data transfer are now supported for all transactions, including transactions where PCI Development platform sources data (See x 8.5).

# **System Overview**

### 2.1 Hardware

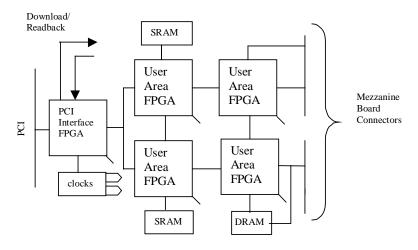

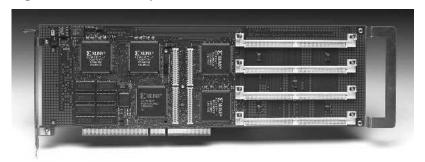

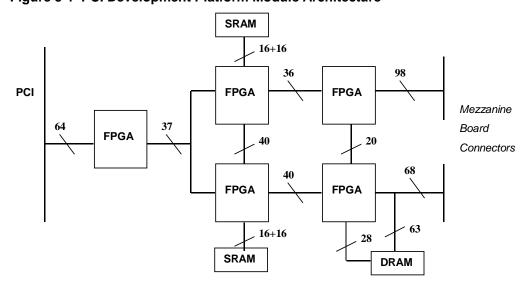

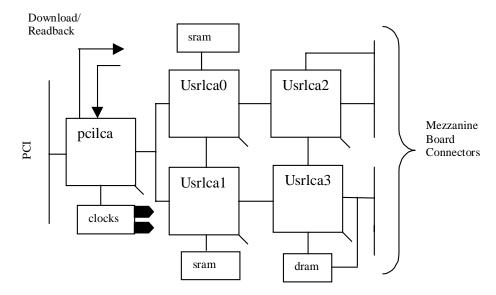

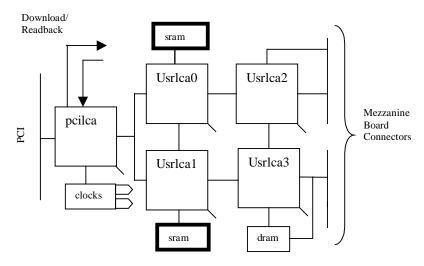

The PCI Development Platform module is a generic PCI board based on reconfigurable logic. The hardware is built around SRAM based Field Programmable Gate Arrays (FPGAs) from Xilinx Inc. These components can be infinitely reprogrammed in circuit. Programming time is measured in tens of milliseconds. The reconfigurable nature of the board makes it useful for an extremely broad class of applications. Figure 2-1 shows a PCI Development Platform module overview and Figure 2-2 shows the PCI Development Platform module.

Figure 2-1 PCI Development Platform Module Overview

Figure 2-2 PCI Development Platform Module

#### 2.1.1 PCI to User Area Interface FPGA

The board uses a Xilinx 4000 series FPGA to interface directly to a PCI bus. This FPGA is programmed to contain a proprietary Compaq PCI interface. The board may be used as a 5V, 33 MHz, 32-bit or 64-bit PCI target and initiator.

#### 2.1.2 SROM and EEPROM

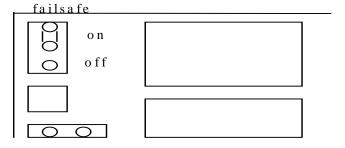

The PCI interface firmware is stored in both EEPROM and SROM. The firmware in the EEPROM is reconfigurable by the user. The PROM used at power-up is determined by the position of a failsafe jumper located in the top left corner of the board.

Although the firmware in the EEPROM is reconfigurable, any changes to this firmware may affect compatibility with the device driver and support software and will not be supported by COMPAQ.

#### 2.1.3 User-Area FPGA

Behind the PCI interface FPGA (PIF) is a 2 x 2 user matrix of PQ208 footprints which, depending on the version, are populated with Xilinx 4000 series FPGA devices. The user matrix can be programmed from the host system via the interface FPGA. Devices in the user matrix can be programmed individually or in parallel with other user matrix devices. The matrix connects to the SRAM, DRAM modules, and IEEE P1386 daughter board connectors (Common Mezzanine Card/PCI Mezzanine Card).

#### 2.1.4 SRAM and DRAM

In version one of the PCI development platform, two independent SRAM banks are provided, each is 64 k x 16-bits. These offer small fast scratch pad memory using 12ns SRAM. The version one board is identifiable by the eight SRAM part is the lower left corner. Version two has four SRAM parts in the same location.

In version two, the SRAM has been expanded to two independent SRAM banks that are each 128 k x 16-bits. The chip-select signals on version one are now used as address lines. This is possible because there is only one chip on each address and data line. The chip-enable signal is permanently enabled.

DRAM modules provide large amounts of local storage, which can be read/written in excess of 100 MB/s to provide bulk storage independent of the host memory system. The board has four angled 72-pin SIMM connectors. The data connections are shared. There are two address inputs, each going to two SIMMs. This allows the SIMMs to be operated in an interleaved manner. The data connection supports memories up to 36 bits wide. There are 12 address lines supporting up to four 64 MB modules. To meet the dimension limits of a single PCI slot, the

DRAM modules used should be 1-inch or less in depth. Deeper modules may be used provided the next slot is empty or it contains a short PCI card. Since all the logic controlling the SIMMs would be in user FPGAs, it would be possible to use any kind of 5V 72-pin SIMM.

### 2.1.5 Clocking Circuitry: System Clock and User Clock

The PCI Development Platform module has two independent clock systems, the user clock and the system clock, each of which is distributed to all of the FPGAs. The system clock is a copy of the PCI clock that has been recovered with a PLL. The system clock provides an in-phase copy of the PCI clock at the PCI frequency or double the PCI frequency.

The user clock is the output of a programmable frequency generator. The frequency range of the user clock is 400 kHz to 100 MHz with a resolution of about 0.5%. The user clock can be stopped, stepped, or double-stepped under software control. The user clock has no defined phase relation to the PCI clock.

#### 2.1.6 Mezzanine Cards

The board provides a daughter card facility conformant with the IEEE P1386 Common Mezzanine Card (CMC) standard. Short, single width, mezzanine cards are supported.

With appropriate user FPGA programming, the mezzanine card may use PCI protocols (IEEE P1386.1) that are 32-bit or 64-bit wide with 64 extra uncommitted I/Os, or a custom protocol may be developed using only the P1386 layer. Thus, the mezzanine card allows electrical adaptation for external connections through the development of simple low-cost adapter cards using a custom protocol as well as the direct connection of standard commercially available PCI Mezzanine Cards (PMC).

## 2.1.7 DMA Engine

The PCI Development Platform module contains a simple but flexible DMA engine controlled by two registers. The DMA engine only supports 32-bit aligned addresses, but does support 32bit and 64-bit data transfers. The following burst order and data widths are supported:

- Linear increment

- Intel cache-line wrap mode

- Cache-line wrap

- Linear increment (request 64-bit)

#### 2.2 Software

The following sections describe the software used with the PCI Development Platform module.

Table 2-1 lists the software used with the PCI Development Platform module.

Table 2-1 PCI Development Platform Software

| Software               | Platforms                                        | Distributed as    | Language |

|------------------------|--------------------------------------------------|-------------------|----------|

| Drivers                | TRU64 UNIX (Alpha)<br>Windows NT (Alpha & Intel) | Binary and Source | С        |

| PamRT run-time library | TRU64 UNIX (Alpha)<br>Windows NT (Alpha & Intel) | Binary and Source | C        |

| Testing software       | TRU64 UNIX (Alpha)<br>Windows NT (Alpha & Intel) | Binary and Source | C        |

| Support tools          | TRU64 UNIX (Alpha)<br>Windows NT (Alpha & Intel) | Binary and Source | С        |

#### 2.2.1 Device Driver

The PCI Development Platform drivers allow the board to be mapped to a user application's address space and provide support for allocation and translation of memory, and fielding of interrupts.

#### 2.2.2 Related Software

The accompanying software contains three major items: run-time libraries, testing software, and support tools.

The PamRT.c language run-time library allows the user to write applications to control the board and communicate with user developed circuits that have been downloaded into the board. It also supports download and read-back of user circuits, setting clocks, and other functions.

Testing software consists of PamTest, a verification test used to ensure that the board is performing some basic functions and the hardware is reliable. The PCI Development Platform module is a programmable gate array board; therefore, the functional test software focuses its' coverage on the communication between the board components. In other words, PamTest is not a design verification tool.

The Xilinx design tools create individual bit streams for each FPGA. These can be downloaded as a single entity, simplifying the downloading procedure of designs. The support tools provided by COMPAO are used to concatenate the bit streams together when downloading to the Xilinx user FPGAs and for reading bit streams from the FPGAs and the firmware from the EEPROM. The support tools also include an application that can be used to update the PIF firmware in the EEPROM.

## 2.3 Updates

For updates on the current software and firmware kits, see the World Wide Web site at locations:

http://www.research.compaq.com/SRC/pamette/

http://www.compaq.com/customsystems/platforms/realtime\_manu.html

This site also contains the answers to the most frequently asked questions and other miscellaneous information concerning the PCI Development Platform module.

# **Configuration and Installation**

## 3.1 Hardware Configuration

The PCI Development Platform module communicates with the host system across the PCI bus via the PCI compliant PCI interface FPGA (PIF). This FPGA may be reprogrammed after initial boot-up, but it is recommended that the COMPAQ supplied PCI design is loaded into this FPGA during initial boot-up. This allows for initial confirmation of communication between the PCI Development Platform module and the platform.

## 3.1.1 Failsafe Jumper

A failsafe jumper is provided to select the source of the configuration bit stream for the PCI interface FPGA. As shipped, the SROM and EEPROM are loaded with the COMPAQ PCI compliant firmware. When the failsafe jumper is located in the "on" position (see Error! **Reference source not found.**), the PCI interface FPGA is loaded with the firmware from the SROM. When the failsafe jumper is located in the "off" position (default), the PCI interface FPGA is loaded from the EEPROM. The original PCI interface firmware can always be restored by rebooting after placing the failsafe jumper in the "on" position (see Chapter 12).

Figure 3–1 Failsafe Jumper and SROM Configuration for Boot-up

#### 3.2 Hardware Installation

The PCI Development Platform module can be installed in either a 32-bit or a 64-bit PCI bus. A mezzanine card (CMC or PMC) can be connected to the PCI Development Platform module using the standoff pin and mezzanine connector. There is also space for four Dynamic RAM modules. For initial boot-up and testing, a mezzanine card and DRAM are not needed. Physical installation of the module should be performed with the host platform powered off.

# **Software Installation**

#### 4.1 Introduction

The PCI Development Platform Software Kit contains two CDs (one for Windows NT and one for TRU64 UNIX). Each disk contains a device driver, run-time library, schematics, and this user guide. The installation process for TRU64 UNIX and Windows NT is different, so they are covered separately in the following sections.

#### 4.2 TRU64 UNIX Software Kit Installation

The TRU64 UNIX PCI Development Platform Software Kit is installed by using the setld command.

| Note                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The TRU64 UNIX commands are case sensitive and must be entered as shown. The PCI Development platform is also referred to as Pamette. This is can been seen in the source code and some of the software commands. |

### 4.2.1 Deleting Old Device Driver Revisions

If there is an old version of the PCI development platform software kit on the system, it should be removed before installation or reinstallation of the new kit. The easiest way to do this is using the setld command. This command (setld -i) lists all the currently installed software subsets. The correct command and sample output are shown below:

```

# setld -i | grep -i pam

installed PAM PCI Device Driver

PRLPPAMDRV247

```

An installed software subset can be removed using the following command:

```

# setld -d {software subset name as shown above}

```

For example, to remove the PAM PCI device driver above use:

```

# setld -d PRLPPAMDRV247

```

All installed software subsets associated with the PCI development platform software kit should be deleted before installing the new software kit. The number 247 on the software subset is just an example. The number will vary depending on the previously installed version. Preparing for Kit Installation

After inserting the Tru64 UNIX Device Driver for the PCI Development Platform Reconfigurable Hardware Array CD-ROM in the system's CD-ROM device, mount it and change the working directory. For example:

```

# mount -r /dev/rz4c

# cd /mnt/PAMDRV

Note

The actual CD-ROM device and mount point may be different from above.

```

## 4.2.2 Installing the Kit

The PCI development platform software kit is installed using the standard setld command. The command for installation and corresponding output are shown below. The command (setld -1 .) should be executed from the same directory that the driver package is in.

```

# setld -l .

The subsets listed below are optional:

```

There may be more optional subsets than can be presented on a single screen. If this is the case, you can choose subsets screen by screen or all at once on the last screen. All of the choices you make will be collected for your confirmation before any subsets are installed.

- 1) C++ Logic Description Library

- 2) Miscellaneous Support Tools

- 3) PAM PCI Device Driver

- 4) PAM kit overview (html)

- 5) Pam Source Packages

- 6) Pamette Runtime Library

- 7) Pamette Sample Applications

- 8) Pamette Test Programs

```

--- MORE TO FOLLOW ---

```

Enter your choices or press RETURN to display the next screen.

```

Choices (for example, 1 2 4-6): 1-8

```

Or you may choose one of the following options:

- 8) ALL of the above

- 9) CANCEL selections and redisplay menus

- 10) EXIT without installing any subsets

Add to your choices, choose an overriding action or press RETURN to confirm previous selections.

```

Choices (for example, 1 2 4-6): 1-8

```

```

You are installing the following optional subsets:

C++ Logic Description Library

Miscellaneous Support Tools

PAM PCI Device Driver

PAM kit overview (html)

Pam Source Packages

Pamette Runtime Library

Pamette Sample Applications

Pamette Test Programs

Is this correct? (y/n): y

7 subset(s) will be installed.

Loading 1 of 8 subset(s)....

PAM PCI Device Driver

Copying from . (disk)

Verifying

Loading 2 of 8 subset(s)....

Pamette Test Programs

Copying from . (disk)

Verifying

Loading 3 of 8 subset(s)....

Pamette Sample Applications

Copying from . (disk)

Verifying

Loading 4 of 8 subset(s)....

Pamette Runtime Library

Copying from . (disk)

Verifying

Loading 5 of 8 subset(s)....

PAM kit overview (html)

Copying from . (disk)

Verifying

Loading 6 of 8 subset(s)....

Pamette Source Package

Copying from . (disk)

Verifying

Loading 7 of 8 subset(s)....

C++ Logic Description Library

Copying from . (disk)

```

```

Verifying

Loading 8 of 8 subset(s)....

Miscellaneous Support Tools

Copying from . (disk)

Verifying

8 of 8 subset(s) installed successfully.

Configuring "PAM PCI Device Driver" (PRLPPAMDRV250)

To enable this functionality, rebuild the system kernel using

doconfig with no command flags.

Configuring "Pamette Test Programs" (PRLPAMTEST222)

Configuring "Pamette Sample Applications" (PRLPAMSAMP218)

Configuring "Pamette Runtime Library" (PRLPAMRT161)

Configuring "PAM kit overview (html)" (PRLPAMDOC280)

Configuring "Pam Source Packages" (PRLPAMSRC280)

Configuring "C++ Logic Description Library" (PRLPAMDC238)

Configuring "Miscellaneous Support Tools" (PRL1UTL125)

```

#### 4.2.3 File List

After the kit is installed, the setld -i command will display all of the currently installed subsets. The following subsets are installed during the PCI development platform installation:

```

PRL1UTL125Miscellaneous Support Tools

PRLPAMDC238 C++ Logic Description

PRLPAMRT161 Pamette Runtime Library

PRLPAMSAMP218 Pamette Sample Applications

PRLPAMSRC280 Pam Source Packages

PRLPAMDOC280 PAM kit overview (html)

PRLPAMTEST222 Pamette Test Programs

PRLPPAMDRV250 Pam PCI Device Driver

```

By appending the subset name to the <code>setld -i</code> command, information on content and location of the files within the subset is revealed. The following example shows the contents of the Pam PCI Device Driver. The device driver is in the <code>PRLPPAMDRV241</code> subset. This name is appended to the <code>setld -i</code> command as follows.

```

setld -i PRLPPAMDRV250

```

The resulting file list is show below.

```

./usr/opt/PRLPPAMDRV250

./usr/opt/PRLPPAMDRV250/config.file

./usr/opt/PRLPPAMDRV250/files

./usr/opt/PRLPPAMDRV250/pci_data

./usr/opt/PRLPPAMDRV250/ppam.c

./usr/opt/PRLPPAMDRV250/stanza.static

./usr/sys/include/sys/ppamio.h

```

## 4.2.4 Rebuilding the Kernel

After the driver is installed using the setld command, the kernel has to be rebuilt and the system has to be rebooted. The kernel can only be rebuilt by root, using the following command:

```

# doconfig

```

The user is then prompted to decide what options to be included with the new kernel. This configuration is typically left up to the system administrator. After the kernel is rebuilt, it should be moved to the root directory.

```

# mv /sys/{system name}/vmunix /

```

The system name may be the computer name or a different name assigned by the system administrator. After the doconfig command has finished building the new kernel, the path to the new kernel will be shown. It is the kernel in this path that should be moved to the root directory.

### 4.3 Windows NT Software Installation

The Windows NT PCI development platform software is installed by using an installation shield.

### 4.3.1 Installing the Software

To install the PCI Development Platform software, place the CD-ROM in the CD-ROM drive. From the **start** button, go to **run** and execute D:\setup\_alpha or D:\setup\_intel (this assumes the CD-ROM drive letter is D). An installation shield will load. If a version of the Development platform software is currently installed, the user is prompted for permission to remove the old version. It is recommended that the user remove older versions of the software kit before proceeding. The license agreement is presented next. After reading the agreement, click the **next** button. The software allows different subsets to be installed. It is recommended that the PCI Development platform Driver and PamRT subsets be installed. The PamDC and Samples subsets are optional. The installation can now proceed by clicking the **next** button. Follow the directions on the screen to complete the installation of the software kit.

### 4.3.2 Deleting old NT Software Revisions

The software kit can be removed by going from start -> settings -> control panel, on the Windows NT menu bar. In the control panel window, double click the Add/Remove Programs icon. Click on the Pam Software Kits line in the lower window, then click the Add/Remove button and confirm the removal of the program.

## 4.4 Installation Verification Procedure

The following sections provide the procedure for running tests to verify proper hardware and software installation.

#### 4.4.1 PamTest

After the software is installed and the system is rebooted, the module's operating condition can be tested with the PamTest utility. The following code displays the options associated with PamTest. It is recommended that the user begin with PamTest -C 0. (Chapter 11 describes the other software utilities that can be used to control the module from the command line in Windows NT or TRU64 UNIX.) The executable for PamTest is located in the /usr/bin directory under TRU64 UNIX and Windows NT executable is located in c:\Pam\bin directory. The following statement describes the use of the PamTest. On Windows NT systems, PamTest is run from the MS-DOS prompt as shown below:

```

C:\pam\bin\PamTest -C 0

```

On TRU64 UNIX systems, the PamTest is run from the command line as shown below:

```

/usr/bin/PamTest -C 0

```

The appropriate result for TRU64 UNIX and Windows NT is shown below. If PamTest does not run and a runtime error results, please check the installation procedure.

```

-- PamTest of Jun 13 1999 15:18:11

Board : PCI Pamette V1R1

Firmware : 2.0

Serial Number: 0

Config: 4044XLA 4044XLA 4044XLA 4044XLA

Download OK

Clock

OK

Connect

OK

Readback OK

Sram

OK

Intr

OK

Ebus

OK

```

#### **Note:**

The PamTest application is currently designed for PCI buses that run at 33.3 MHz. Many PCI buses do not meet this requirement (the PCI specification only requires a PCI bus to operate at less than or equal to 33.3 MHz). This would cause the PamTest application to fail during the clock test. If PamTest reports a clock frequency less than 33.3 MHz, your module may be functioning correctly. To check the functionality of the board run the following PamTest option, which excludes the clock test.

On Windows NT systems, run the following command from the MS-DOS prompt:

```

C:\pam\bin\PamTest -C 0 -e clock

```

On TRU64 UNIX systems, the appropriate command is shown below:

```

/usr/bin/PamTest -C 0 -e clock

```

The appropriate result for TRU64 UNIX and Windows NT is shown below.

```

-- PamTest of Jun 13 1999 15:18:11

Board : PCI Pamette V1R1

Firmware : 2.0

Serial Number: 0

Config: 4044XLA 4044XLA 4044XLA 4044XLA

Download OK

Connect

OK

Readback OK

Sram

OK

Intr

OK

Ebus

OK

```

#### 4.4.2 SRAM Test

SRAM Test checks the functionality of the onboard SRAM. In testing the SRAM, the module programs the FPGAs to complete the connection between the PCI interface and the SRAM memory; therefore, this test adds coverage to the PamTest utility. The following statement describes the use of the SRAM Test. On Windows NT systems, the SRAM Test is run from the MS-DOS prompt as shown below:

C:\pam\bin\sramtest

On TRU64 UNIX systems, the SRAM Test is run from the command line as shown below:

/usr/bin/ppam\_sramtest

The SRAM test returns a passed message if the SRAM is functioning correctly:

Sramtest passed

## **Module Architecture**

#### 5.1 Introduction

To completely utilize the functional and programmable capabilities of the PCI Development Platform module, the designer must have an in-depth knowledge of the interconnections on the module, the resources within the FPGA, and the accompanying software including run-time libraries and drivers. The accompanying schematics and software code, along with the technical specifications for the FPGAs, are necessary for implementing an actual design.

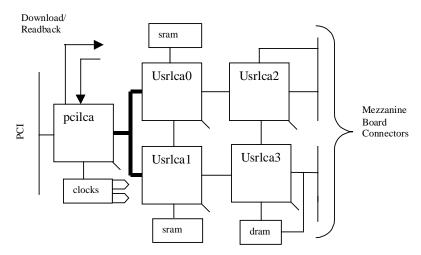

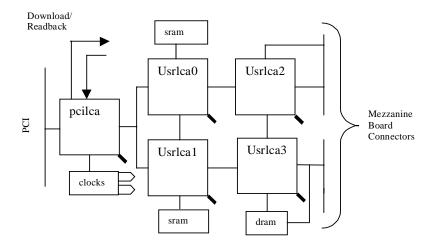

To understand the host interface of the PCI Development Platform module, one must first be familiar with the physical resources that exist for communication between the PCI interface FPGA (PIF), which has a relatively fixed configuration, and the four user-area FPGAs, which are programmed with application specific configurations. In the schematics<sup>1</sup>, the PIF is called the pcilca. The usrlca0, usrlca1, usrlca2, and usrlca3 comprise the user-area. The overall architecture of the PCI Development Platform module is shown in Figure 5-1. The available resources for the PIF user-area interface are presented in the following sections.

Figure 5-1 PCI Development Platform Module Architecture

<sup>&</sup>lt;sup>1</sup> The schematics are contained on the installation disk as a postscript file, ppschema.ps.

## 5.2 PCI Interface to User-Area Connections

The following sections describe the PCI interface to user-area connections.

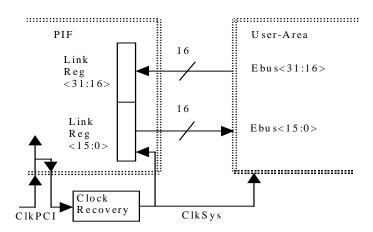

#### 5.2.1 EBus

EBus<35:0> (east bus) and CnfgP\_ld.din<sup>2</sup> constitute a 37-bit wide bus joining the pcilca, usrlca0, and usrlca1 FPGAs (see Figure 5-2). CnfgP\_ld.din also connects to the download input of the PIF and its serial ROM and is used during PIF configuration and firmware upgrades, but during normal operation it is treated as an extension of EBus<35:0>.

Figure 5-2 EBus Connections

## **5.2.2 Rings**

The Ring<1:0> is a 2-bit wide bus that connects to all five FPGAs (see Figure 5-3). The Ring pins are privileged in that they connect to pins that can directly drive FPGA global buffers. They can be used as general-purpose resources or programmed as interrupts. Refer to the interrupt section 8.5.5.3.

<sup>&</sup>lt;sup>2</sup> Refer to the schematics for reference on all physical components.

Figure 5-3 Ring Bus

### 5.3 Clocks

The PCI Development Platform module has two independent clock systems, each of which is distributed to all FPGAs (see Figure 5-4).

**Clksys** is a copy of the PCI clock that has been recovered with a Phase-Locked Loop (PLL). The clock recovery circuit is a Motorola MC88915T. In addition to producing a buffered low skew copy of the input, Clksys can, under software control, be put into a mode in which its output is double the frequency of the PCI clock. Thus Clksys provides an in-phase copy of the PCI clock at the PCI frequency or double the PCI frequency. This PLL can also produce an in-phase copy of an externally supplied clock (over the mezzanine connector). The clock source selection signal is driven from pin 5 on Usrlca3.

Clkusr is the output of an ICD2053B programmable frequency generator. This clock can be set to frequencies in the range 400 kHz to 100 MHz in steps of about 0.5%. Additionally, Clkusr clock can be stopped, stepped, or double-stepped<sup>3</sup> under software control. Clkusr has no defined phase relation to the PCI clock.

<sup>&</sup>lt;sup>3</sup> Double-stepped means from the stopped state two clicks are issued by Clkusr after which the clock returns to the stopped state.

Figure 5-4 Clocks

### **5.4 SRAM**

The Development Platform module has two separate SRAM banks (see Figure 5-5), one for Usrlca0 and the other for Usrlca1.

For version 1, each bank contains 128 Kbytes of storage. This SRAM is fast asynchronous memory capable of operating at clock speed above 80 MHz.

For version 2, each bank contains 256 Kbytes of storage. This SRAM is also fast asynchronous memory and it is capable of operating at clock speed above 80 MHz. See section 2.1.4 for an explanation of the difference between the two versions.

The SRAM can be used to hold state bits, data in intermediate stages of computation or other necessary storage. Larger amounts of data can be stored in DRAM modules, which may be placed directly on the module and is discussed in Section 5.5.

Figure 5-5 SRAM Banks

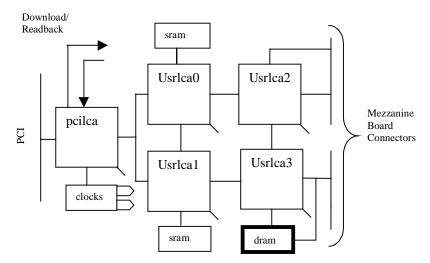

## **5.5 DRAM**

Four 72-pin SIMMs DRAM connectors are present on the Development Platform module. The DRAM is connected between the mezzanine card connectors and Usrlca3 (see Figure 5-6). There is no DRAM controller on the module; consequently, any 72-pin SIMMs can be used on the board. The appropriate control logic for the SIMMs needs to be placed in Usrlca3 or on the daughter board. The DRAM is meant for storage of bulk data, while the SRAM provides fast access to smaller amounts of data.

Figure 5-6 DRAM

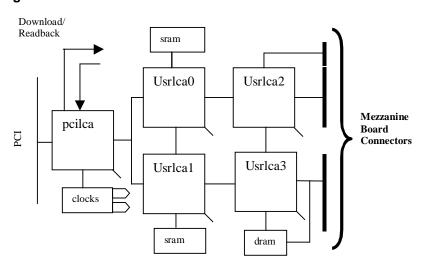

#### 5.6 Mezzanine Connectors

The Development Platform module supports short, single width, mezzanine cards conformant with the IEEE P1386 Common Mezzanine Card Standard. The module also has the capability of supporting PCI mezzanine Cards. Similar to the DRAM connectors, the control logic for the mezzanine cards has to be developed for each application. Usrlca2 and Usrlca3 connect directly to the mezzanine card.

When the mezzanine card is placed on the Development Platform module, one end of the card adjoins the PCI bracket. This allows external connectors (see Figure 5-7) and cabling to attach directly to the daughter board through an opening in the PCI bracket. The use of a custom daughter board allows the Development Platform module to adapt to a variety of applications. Daughter boards can be used for data collection and other I/O communications. Specialized functions, such as JPEG and MPEG compression, can be accomplished by fitting daughter boards with application specific chips or processors.

Figure 5-7 Mezzanine Connectors

# **Address Map**

## 6.1 Introduction

PCI Development Platform decodes its configuration space (mandatory for all PCI devices), and a single 16 MB memory space region. The pam value returned by PamOpen is a pointer to the base of the memory space region. The memory space region is subdivided as follows:

| Address range     | Contents                                   |

|-------------------|--------------------------------------------|

| 0x0 0x3f          | struct PamRegs                             |

| 0x40 0x3ff        | 15 more aliased copies of PamRegs          |

| 0x400 0x1fff      | < reserved >                               |

| 0x2000 0x200b     | DMA engine                                 |

| 0x200c 0xffff     | < reserved >                               |

| 0x10000 0x1003f   | aliased copy of PamRegs with secure access |

| 0x10040 0x103ff   | 15 more aliased copies of PamRegs          |

| 0x10400 0x11fff   | < reserved >                               |

| 0x12000 0x1200b   | aliased copy of DMA engine                 |

| 0x1200c 0x1ffff   | < reserved >                               |

| 0x20000 0x1000000 | user transaction region                    |

| Note                                                                                                      | _ |

|-----------------------------------------------------------------------------------------------------------|---|

| Most users only need to know that the first 128 KB of address space is treated differently from the rest. |   |

- struct PamRegs is defined in <PamRegs.h>, which is part of the PCI Development platform run-time software kit.

- The regions labeled *reserved* in the memory space address map are used primarily for PCI target performance testing. In these regions, writes are NOPs and reads return unpredictable data.

The reserved regions below 0x20000 which have address bit 14 set (0x4000), have the special property that they accept 64-bit transactions. (In PCI protocol terms, when transactions are addressed to these regions with the PCI signal REQ64 asserted, ACK64 is asserted in response, in all other regions ACK64 is never asserted).

User software that writes to currently reserved regions must be reviewed with each new firmware revision to ensure that new functions have not been assigned to these regions. A prudent coding practice for such code would be to refuse to run on firmware revisions higher than the current released revisions, thereby obliging the programmer to review it at each new revision. Recall that the only code that should need to access reserved regions is PCI target performance testing code.

- The address range 0x10000 ... 0x1ffff is essentially an alias for the range 0x0 ... 0xffff with the additional property that certain security sensitive bits in struct PamRegs can only be written by accesses to this range. PCI Development platform device drivers may only permit privileged users to map the range 0x10000 ... 0x1ffff. See Chapter 9 for more discussion of the security bits.

- Access to some fields in aliased copies of PamRegs may use addr<9..6> as an argument to the access. See the source code of PamRT for details.

# **DMA** Engine

#### 7.1 Introduction

The PCI Development Platform module contains a simple but flexible DMA engine controlled by two control registers starting at address 0x2000. These DMA registers are also accessible from the user-area FPGA (see Section 8.5.3). Access to the DMA engine is disabled unless the appropriate security bit is set (see Chapter 9).

## 7.2 DMA Address Register: 0x2000

Although PCI Development platform's DMA Engine can generate IO READ and IO WRITE PCI commands, it is primarily designed to work with 32-bit aligned addresses. In particular, it is not possible to load the DMA Engine with an address in which the low two bits are both one. In memory space commands the low two bits of the address register are used to encode the burst order and data width, as follows:

0x0 Linear increment.

**0x1** Intel cacheline wrap mode (now deprecated in PCI spec).

**0x2** Cacheline wrap (linear increment within cacheline).

0x3 Linear increment (request 64 bit). Address emitted on bus has low two bits cleared.

The DMA Engine only makes requests for 64 bit transactions (asserts the PCI signal REQ64) when the low two bits are 0x3, or when the DMA Engine is programmed from the user-area and the interface is in 64-bit Transaction mode. All other transactions initiated by the DMA Engine request the use of 32 bit data cycles.

The DMA address register is incremented on each data cycle. Increment order is always linear even if the specified burst order is not linear. The ability to specify non-linear burst orders (encoding 0x1 and 0x2) only exists for the purposes of testing other devices. The DMA address register counter only applies to bits 2..12, thus if a DMA causes the address to increment to the boundary of an aligned 8kB region, it wraps back to the beginning of that region.

## 7.3 DMA Command Register: 0x2000+8

DMA commands are encoded in an arcane format whose primary motivation is to simplify the PIF circuit. The fields in the DMA command register are as follows.

| Bit Range | Contents              |

|-----------|-----------------------|

| 3128      | PCI command           |

| 2716      | 0x1000 - length       |

| 1512      | delay to next request |

| 112       | 0x400 - burst length  |

| 1         | Unused                |

| 0         | Unused                |

Note that in the preceding table "0x1000 - length" means the numerical value of 0x1000 minus length. Likewise for "0x400 - burst length". For example, if the user wants a length of 8, bits 27..16 should be loaded with "0x1000 - 8" which is equal to 0xf f 8.

Length and burst lengths always count in 32-bit words. When requesting 32-bit transactions, a burst length of 1, 2 or 3 are treated as a minimum burst length due to internal pipelining restrictions. When requesting 64-bit transactions, a burst length of 2, 4 or 6 is similarly treated as a minimum burst length. Any odd burst length, odd start address or odd total length forces a transaction to 32-bit. For 32-bit DMA, the minimum burst length is one 32-bit word, for 64-bit DMA, minimum burst length is one 64-bit word.

The DMA length must be a multiple of the burst length. Failure to observe this restriction may cause the DMA Engine to overrun beyond length up to the next multiple of burst length.

The interface will start requesting DMA when bit 27 in the DMA command register is set. Bits 27..16 are a counter which will count up by one for each DWORD(4 bytes) transferred —when bit 27 returns to zero the DMA Engine stops requesting transactions. Bit 27 is automatically zeroed whenever the PROG bits controlling the configuration of usrlca0 and usrlca1 ( bits 0 and 1 in register 0x8 in struct PamRegs) are zero. This feature is designed to abort any active DMA if the user-area if deconfigured, as for example happens on last close of the PCI Development platform device under UNIX.

Software wishing to abruptly stop the DMA Engine should not simply clear the DMA command register. At the moment the host access updating the DMA command register arrives, a DMA transaction may already have been initiated that will issue in the cycles immediately following the update. If the DMA command register were indiscriminately cleared, the DMA transaction could proceed with invalid values for the PCI command and other fields in the DMA command register. Instead, software should use a read modify write sequence to clear only bit 27 and the rest of the length field.

The burst length field (11..2) is the desired burst length in data cycles. If the burst is disconnected the next request will try to complete the DMA up to the burst boundary then stop and start a new request for the next burst. The maximum burst size is attained by setting bits (11..2) to all zeroes. Hence maximum burst size is 0x400 DWORDs, or 4096 bytes.

The delay to next request (bits 15..12) specifies a delay between bursts. This lets us throttle back the rate, it also lets us optimize throughput on host bridges that introduce their own wait states.

When the remaining length is less than twice the *burst length* and *delay to next request* is set to 0 (respectively 1), the interface increases delay to next request by 2 to 2 (respectively 3). If this were not done the DMA Engine could issue an extra burst (beyond the rules stated above) because the decrement of length is delayed by a couple of cycles from the cycle when the actual data is transferred.

Typically the PCI commands used with the DMA Engine are the memory commands:

| Command Code | Meaning                     |

|--------------|-----------------------------|

| 0x6          | Memory read                 |

| 0x7          | Memory write                |

| 0xC          | Memory Read Multiple        |

| 0xE          | Memory read line            |

| 0xF          | Memory write and invalidate |

Refer to the PCI specification for more details on the precise meanings of these commands.

# 7.4 Simultaneous Initiator and Target

The DMA engine is well partitioned from the PCI target state machine in the PIF. One consequence of this is that it is perfectly possible for PCI Development Platform to be the target of cycles that it initiates. Allowing PCI Development Platform to be the target of its own cycles makes it possible to access any PIF control register from the user-area.

# **Interface Modes**

# 8.1 Introduction

Four distinct interface modes are supported in the current firmware. These are selected through the PamRT.h function PamSetMode or PamSetModeAndDelay which sets the appropriate value in the decode register at address 0x30 in PCI Development Platform memory space. The three modes are:

- Static mode is a simple low-performance interface that provides statically configured 16bit paths to and from the user-area.

- **Promiscuous mode** transmits a selection of data and control values present on the PCI bus to the user-area. The flow of data is one-way. This is similar to promiscuous mode on Ethernet adapters.

- **Transaction mode** is a high performance transaction oriented mode that supports both target and master operation. This is the preferred mode for all but the simplest designs.

- **Promiscuous Transaction mode** combines the protocol state machine of the Transaction mode with the trace collection capabilities of Promiscuous mode. It can aid in the debug of Transaction mode applications.

The four modes are described in more detail in the following sections.

#### 8.2 Static Mode

From the host side, Static Mode consists of a single 32-bit *link* register (address 0x38 in *struct PamRegs*) that can be read or written. The high 16 bits of write data are ignored. From the userarea side it consists of a 16-bit input port driven by the low 16 bits of the link register and a 16bit output port which loads the high 16 bits of the link register on each Clksys cycle. The userarea input port is EBus<15:0> and the output port is EBus<31:16>. The following figure shows the Static Mode link register flow.

Figure 8-1 Static Mode Link Register

# 8.2.1 Coding guidelines for host software

Although Static mode is conceptually the most simple interface to PCI Development platform, an appreciation of the host CPU to PCI interface, particularly on Alpha systems, is required to ensure correct operation when writing software that communicates with PCI Development platform in Static mode.

To improve performance modern microprocessors may buffer or aggregate write data destined for memory or the I/O subsystem. As a consequence the program should consider time on the PCI bus as completely elastic with respect to CPU instruction issue. Inserting a string of NOPs to implement a short delay between successive accesses to the Link register may indeed introduce a delay with respect to CPU instruction issue. However writes to the Link register that are issued on either side of the string of NOPs may be subject to differing amounts of delay in write buffers allowing the two access to appear back to back on the PCI bus. Worse still some processors may squash, merge or reorder writes. Usually such processors provide explicit serialization commands, which may be used by software in cases where order matters. The PamFlush() primitive in the PCI Development platform runtime library issues the appropriate serialization for the current host.

Serialization does not imply that a pending write is issued immediately from the processor or flushed through subsequent levels of buffering in the path to the PCI Development platform. To force writes to the PCI Development platform as quickly as possible, the programmer may follow the write by an explicit read of the Link register or some other low addressed PCI Development platform register in addition to a call to PamFlush(). For this purpose the Info register at address offset 0x0 is a good candidate.

The software programmer should also be aware that updates to the link register are subject to several cycles of pipeline delay in the PIF before they appear on EBus<0:15>. In addition the circuit loaded into the user-area may itself incur several cycles of pipeline delay between a new value appearing on EBus<0:15> and the resulting change propagating to EBus<16:31>. Therefore a write to the Link register followed immediately by a read of the Link register may yield a value in EBus<16:31> which has been computed by the user-area circuit in response to the previous value of the low sixteen bits of the Link register. This value may appear inconsistent with its current value. Several reads may be required before the value read from the high bits of Link register reflects a value computed by the user-area circuit that is based on the last value written to its low bits.

The following code fragment demonstrates the application of the above guide-lines to write two successive values to the low 16 bits of Link register and then read the resulting value that the user circuit has driven on to EBus<16:31> in response to these writes:

```

volatile int force_read;

/* update link register with new_link_val_0 */

PAMREGS(pam)->link = new_link_val_0;

PamFlush();

force_read = PAMREGS(pam)->info;

PamFlush();

/* update link register with new_link_val_1 */

PAMREGS(pam)->link = new_link_val_1;

PamFlush();

/* dummy read to allow time for propagation

through internal pipeline */

force_read = PAMREGS(pam)->link;

PamFlush();

/* get result of computation from EBus<16:31> */

return_link_val_hi = (PAMREGS(pam)->link >> 16) & 0xfff;

```

# 8.2.2 Static Mode and Clkusr

All signals on the PIF side of the EBus are clocked on Clksys. The user-area interface may be clocked on any clock of the user's choosing (in particular Clkusr), however the PIF side of the interface will continue to be clocked on Clksys. Potential metastability problems on the reception of EBus<31:16> are handled in the PIF, but if an asynchronous interface is used the user may see some bits in the input and output ports change one cycle ahead of others. One way to deal with this is to use sideband signals provided by the download path (see Section 5.2.1) as a strobe. The following code fragment illustrates this. It assumes that the user-area circuit is configured to only read from or update the EBus when a logic high (1) is present on Cntrl\_.U\_din<n> (pin 151). Circuits internal to the PIF cause the value written to bit n of the PamRegs field dwnld1 is driven onto Cntrl\_.U\_din<n>.

```

/* update link register */

PAMREGS(pam)->link = new_link_val;

PamFlush();

/* strobe all usrlca DIN (pin 151) */

PAMREGS(pam) -> dwnld1 = 0xf;

PamFlush();

/* end strobe */

PAMREGS(pam) -> dwnld1 = 0x0; PamFlush();

/* get new link register value */

new_link_result = PAMREGS(pam)->link;

```

In user-area applications that use Clksys set to double speed, some care is required to determine which cycles correspond to the first half of the PCI clock and which to the second half. See the PCI performance tests for an example (ppam\_pciperf & pciperf).

# 8.3 Promiscuous Mode

In Promiscuous Mode, EBus<31:0> is always driven by the PIF. On each cycle it contains a copy of the low 32 bits of the PCI address/data bus delayed by a few cycles. During Promiscuous Mode the clock recovery circuit is configured such that Clksys runs at twice the PCI clock speed. The data/address from the PCI bus is driven on to EBus<31:0> during the first half of the PCI clock period. On the second half of each PCI clock period, the PCI control signals for that cycle are driven on to EBus<31:0>. This mode can be used for a variety of bus monitoring applications. Table 8-1 lists the bit assignments.

Table 8-1 Promiscuous Mode Bit Assignments

| Bit range | Contents      |

|-----------|---------------|

| 31        | FRAME         |

| 30        | TRDY          |

| 29        | IRDY          |

| 28        | STOP          |

| 27        | DEVSEL        |

| 26        | GNT           |

| 25        | REQ           |

| 24        | ACK64         |

| 23        | REQ64         |

| 22        | PAR           |

| 2118      | C/BE < 3:0 >  |

| 1712      | < undefined > |

| 110       | AD < 43:32 >  |

The ability to enter Promiscuous Mode is disabled unless the appropriate security bit is set (see Chapter 9).

# 8.4 PromiscuousTransaction Mode

In PromiscuousTransaction mode EBus<31:0> is always driven by the PIF and the values transmitted are identical to regular Promiscuous mode. The difference is in regular Promiscuous mode the PIF responds to transaction as quickly as possible and attempts to burst for as many data cycles as possible to allow the other party in the PCI transaction to operate to its limits of performance. In PromiscuousTransaction mode, the PIF responds to transaction in exactly the same way as it would if it was in Transaction mode (see 8.5.). Whereas regular Promiscuous allows us to analyze the host system and other devices, the purpose of Promiscuous Transaction mode is to debug applications of PCI Development platform which use Transaction mode.

The pciperf (ppam\_pciperf on UNIX) sample application in the PCI Development platform software kit includes a command line switch to operate in PromiscuousTransaction mode.

# 8.5 Transaction Mode

In Transaction Mode, the EBus carries multi-cycle transactions that reflect activity on the PCI bus. Since Clksys is used as the clock, all activity is synchronous with the PCI.

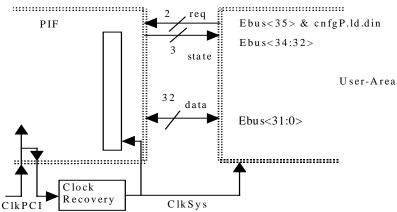

Transaction Mode has a 32-bit bi-directional address/data bus, a 3-bit state code from the PIF to the user-area, and a 2-bit request code from the user-area to the PIF. On each cycle the state code on EBus<34:32> tells the disposition of the data bus (EBus<31:0>) on the next cycle.

When the state code indicates that the data bus is idle, the user-area may read or write certain PIF internal registers using the request codes on EBus<35> and CnfqP\_ld.din. The request codes are also used for coarse-grained flow control of DMA. The following figure shows the bit flow in Transaction Mode.

Figure 8-2 Bit Flow in Transaction Mode

At all times the PIF is master of the protocol and the user-area must satisfy its requests. Flow control must be handled at higher application specific levels, for instance through user-area initiated interrupts and polling of ready bits implemented in user-area status registers. The userarea cannot introduce delays or wait states within an individual transaction.

The user-area design must respect the direction of EBus < 31:0 > dictated by the state code on EBus<34:32> on each cycle. Failure to do so could result in conflicting values being driven onto EBus<31:0>, with possible damage to the module.

The state codes are listed in Table 8-2.

Table 8-2 State Codes

| Mnemonic | Code | Meaning                                                                                     |

|----------|------|---------------------------------------------------------------------------------------------|

| AIF      | 7    | Address cycle of a write to a register in the PCI Interface (address range 0x0 0x1f f f f). |

| DW       | 6    | Data Wait: transaction is active but no progress on this cycle.                             |

| AIU      | 5    | Address cycle of transaction transferring data to user-area                                 |

| AUI      | 4    | Address cycle of transaction transferring data from user-area                               |

| DV       | 3    | Data Valid on EBus                                                                          |

| DS       | 2    | Data Skip: like DV, but byte enables were off—should increment address and ignore data      |

| MSTR     | 1    | Used to prefix transactions that were initiated by PCI Development Platform                 |

| IDLE     | 0    | No active transaction                                                                       |

The distinction between AIF and AIU or AUI is that the PIF claims the first 128 KB (0x20000 bytes) of address space so CPU reads to this region are invisible from the user-area and writes appear as a transaction headed by an AIF cycle. Any CPU read or writes beyond the first 128 KB produces an AIU or AUI cycle.

Note that the Transaction mode state codes offer no mechanism to accurately interpret a partial word write. The DS state code is used for any write data cycle that does not have all byte enables active. Software communicating with PCI Development platform in Transaction mode must ensure that writes are always whole words. Firmware v2.0 and above offers a mechanism to raise an interrupt if a partial word write occurs to addresses at or above 0x20000 in PCI Development address space (see 8.5). Even if the host never generates partial word writes, the DS state code may still appear and should be interpreted to signify a write data cycle with no byte enable active. Writes with no byte enable active interspersed in a stream of DV state codes are a natural consequence of host bridge transaction aggregation. Applications wishing to avoid or eliminate aggregation (for instance to simplify the user-area circuit state machine) may accomplish this by inserting reads between writes that could otherwise be subject to aggregation.

# 8.5.1 Target Transactions

Transactions for which PCI Development Platform is the target will most commonly be generated by CPU accesses to the PCI Development Platform address space, although they can be generated by other PCI Development Platforms or any other master capable PCI device in the system. A basic transaction as seen from the user-area consists of an address cycle (AIU, AUI, or AIF), followed by one or more data cycles (DW, DV, or DS). A transaction is usually terminated by the IDLE state code, but may be terminated by the start of a new transaction (MSTR, AIU, AUI, or AIF). The PIF will never retry transactions<sup>4</sup>, so there will always be at least one DV or DS cycle, however user-area applications should not rely on this behavior as it may change in future firmware revisions.

#### **AIU**

Transactions started by an AIU cycle present address and data to the user-area. In the cycle following AIU, the PIF drives the address onto EBus<31:0> and continues to drive EBus<31:0> with data until the end of the transaction. The number of DW, DV, and DS cycles depends on the master of the transaction, usually the hostbridge. In the simplest case a transaction consists of an AIU cycle, one or more DW cycles, a DV cycle, and then either an IDLE cycle or a new transaction. Note that there will always be at least one DW cycle because the PCI Development Platform is a medium decode device.

Host bridges may aggregate neighboring writes, and Alpha based systems can reorder writes. The PamRT function PamFlush will ensure write ordering but will not guarantee that aggregation is disabled. One way to suppress aggregation is to perform a read to some harmless PCI location, for instance address 0x0 of the PCI Development Platform memory space. DS states may occur when aggregation of a noncontiguous sequence of writes occurs. For example, from the code sequence:

```

volatile int *user_area;

user_area = ((volatile int *) pam) + (1<<17)/sizeof(int);</pre>

user_area[0] = 0xaaaaaaaa;

user_area[2] = 0xbbbbbbbb;

user_area[3] = 0xccccccc;

```

<sup>&</sup>lt;sup>4</sup> Retry is PCI terminology for a transaction that transfers zero data because the target signals to the master that it is not currently ready, and that transaction should be attempted again at a later time.

| Cycle | State | EBus<31:0>    | PIF Drives |

|-------|-------|---------------|------------|

| 0     | AIU   | < undefined > | NO         |

| 1     | DW    | 0xXX020000    | YES        |

| 2     | DW    | < undefined > | YES        |

| 3     | DV    | < undefined > | YES        |

| 4     | DS    | 0xaaaaaaaa    | YES        |

| 5     | DV    | < undefined > | YES        |

| 6     | DW    | 0xbbbbbbbb    | YES        |

| 7     | DW    | < undefined > | YES        |

| 8     | DV    | < undefined > | YES        |

| 9     | IDLE  | 0xccccccc     | YES        |

| 10    | IDLE  | < undefined > | NO         |