**Document Title:**

XMI BUS OVERVIEW HANDBOOK

Order Number:

EK-XMIOV-HB-002

This handbook is part of the XMI Adapters Handbook Documentation Set (EK-XMIAD-HB). The handbook can be ordered separately or as part of the set.

The XMI Adapters Handbook Documentation Set is a dynamic document which will be periodically updated as new XMI adapters are announced. The first release of the set includes the following handbooks:

| Order Number | Title                                  |

|--------------|----------------------------------------|

| EK-XMIOV-HB  | XMI Bus Overview Handbook              |

| EK-CIXCD-HB  | CIXCD Handbook                         |

| EK-DEMNA-HB  | DEC LANcontroller 400 (DEMNA) Handbook |

| EK-DWMBA-HB  | DWMBA Handbook                         |

This handbook and the document set are for VAX system trained Digital customer service personnel who are familiar with the XMI bus architecture.

# XMI Bus Overview Handbook

Order Number EK-XMIOV-HB-002

This document is part of the XMI Adapters Handbook Documentation Set (EK-XMIAD-HB). The document can be ordered separately or as part of the set. The XMI Bus Overview Handbook and the XMI Adapters Handbook Documentation Set are for VAX system trained Digital customer service personnel who are familiar with the XMI bus architecture.

Revision/Update Information: Revision 2.0

**Digital Equipment Corporation**

#### June, 1991

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license.

No responsibility is assumed for the use or reliability of software on equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Restricted Rights: Use, duplication, or disclosure by the U.S. Government is subject to restrictions as set forth in subparagraph (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

Copyright © Digital Equipment Corporation 1991

All Rights Reserved. Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation:

DEC UNIBUS VAX 9000

DECUS VAX VAXBI

PDP VAX 6000 XMI

This document was prepared and published by Educational Services Development and Publishing, Digital Equipment Corporation.

# **Contents**

| Abo           | ut This Manuel         |   |

|---------------|------------------------|---|

| 1             | XMI BUS OVERVIEW       |   |

| 1.1           | INTRODUCTION           | 1 |

| 1.2           | IMPLEMENTATIONS        | 1 |

| 1.3           | BUS PROTO/ OL          |   |

| 1.4           | TERMINOLOGY            |   |

| 1.5           | BUS INTEGRITY FEATURES |   |

| 1.6           | SPECIFICATIONS         |   |

| 2.1           | XMI CARD CAGE          |   |

| 2.1.1         |                        | ; |

| 2.1.2         | Node ID Numbers        |   |

| 2.1.3         | Clock/Arbiter Card     |   |

| 2.1.4         | I/O Connector Pins     |   |

| 2.2           | XME NODE               |   |

| <b>2.2</b> .1 | XMI Corner             |   |

| 2.2.2         | Self-Test LED          |   |

| 2.3           | CONFIGURATION RULES    |   |

|               |                        |   |

| 3    | XMI BUS FUNCTIONAL DESCRIPTION                 |      |

|------|------------------------------------------------|------|

| 3.1  | ADDRESSING                                     | 3–1  |

| 3.2  | BUS SIGNALS                                    | 3–5  |

| 3.3  | BUS FUNCTION CODES                             | 3-8  |

| 3.4  | BUS COMMAND CODES                              | 3–9  |

| 3.5  | DATA TRANSFER TRANSACTIONS                     | 3-10 |

| 3.6  | INTERRUPT TRANSACTIONS                         | 3–19 |

| 3.7  | ARBITRATION                                    | 3-24 |

| 3.8  | BUS INITIALIZATION                             | 3-25 |

| 3.9  | XMI NODE REQUIRED REGISTERS                    | 3–26 |

| 4    | WRITE-BACK CACHE SUPPORT AND THE XMI+ PROTOCOL |      |

| 4.1  | WRITE-BACK CACHE OVERVIEW                      | 4-1  |

| 4.1. |                                                | 4-1  |

| 4.1. |                                                | 4-1  |

| 4.1. |                                                | 4-2  |

| 4.1. | _                                              | 4-2  |

| 4.2  | MEMORY REQUIREMENTS.                           | 4–2  |

| 4.2. | •                                              | 4-2  |

| 4.2. |                                                | 4-3  |

| 4.2. |                                                | 4-3  |

| 4.2. |                                                | 45   |

| 4.3  | I/O CONTROLLER SUPPORT                         | 4-6  |

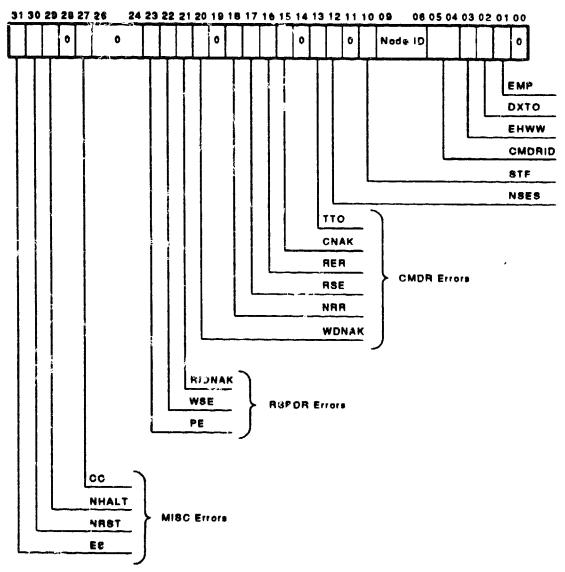

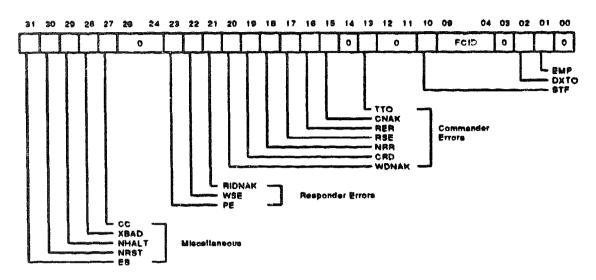

| 5    | DIAGNOSING XMI BUS RELATED ERRORS              |      |

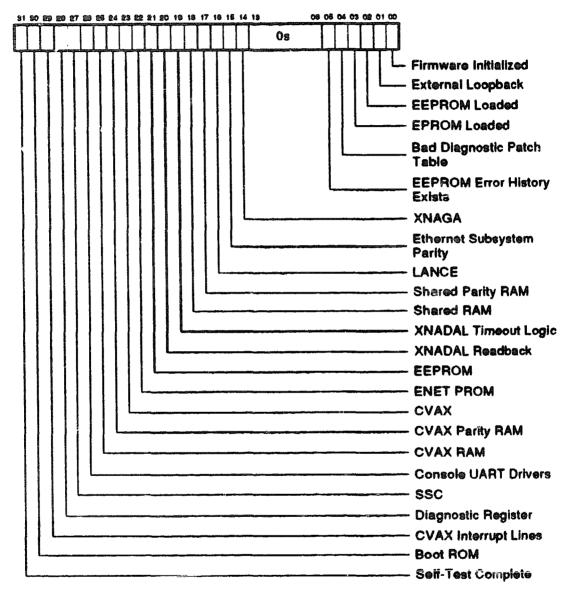

| 5.1  | NODE RBDs AND SELF-TESTS                       | 5-1  |

| 5.2  | ERROR CONDITIONS                               | 5-1  |

| 5.3  | ERROR KANDLING                                 | 5-4  |

| 5.4  | ERROR RECOVERY                                 | 55   |

| 5.5  | ERROR REPORTING                                | 56   |

|      |                                                |      |

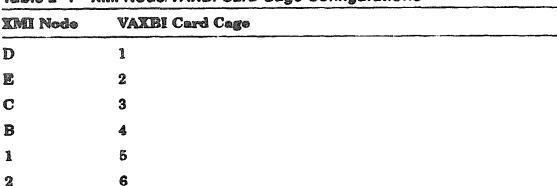

| Figu  | res                                         |      |

|-------|---------------------------------------------|------|

| 1-1   | XMI Bus as the Primary System Bus           | 1-2  |

| 1-2   | XMI Bus as an I/O Bus                       | 1-3  |

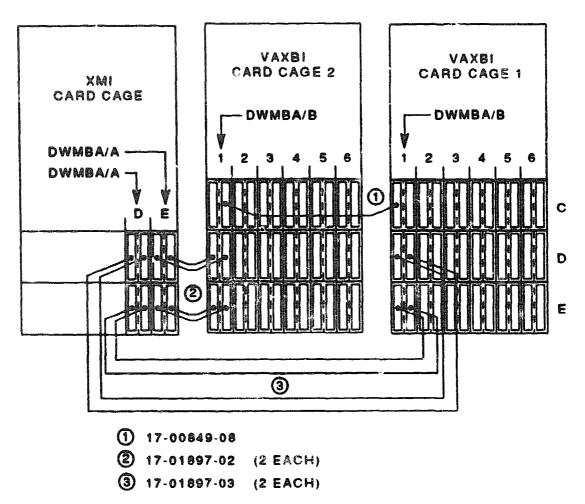

| 1-3   | XMI-Based System with VAXBI-Based I/O       | 1-4  |

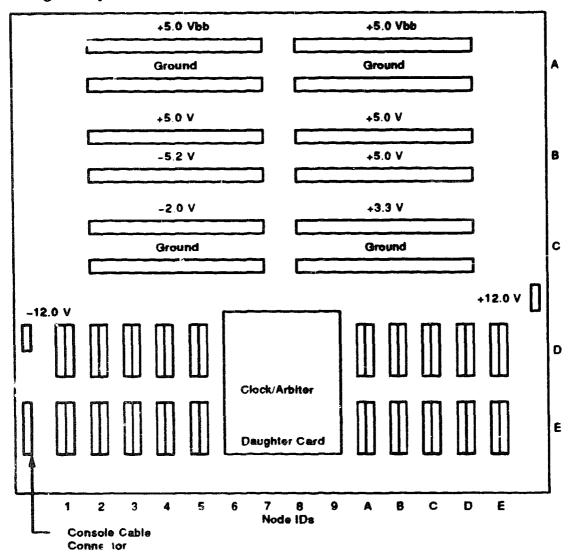

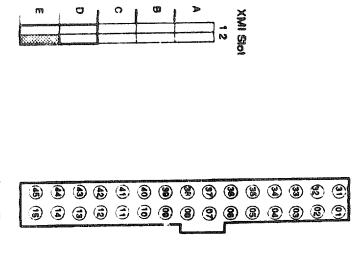

| 2-1   | XMI-1 Backplane (+5.0 Vbb Power)            | 2-2  |

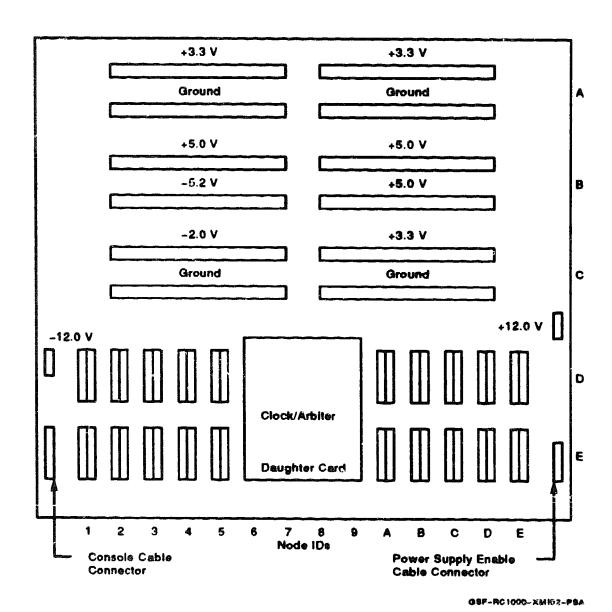

| 2-2   | XMI-2 Backplane (+3.3 Vdc Power)            | 2-3  |

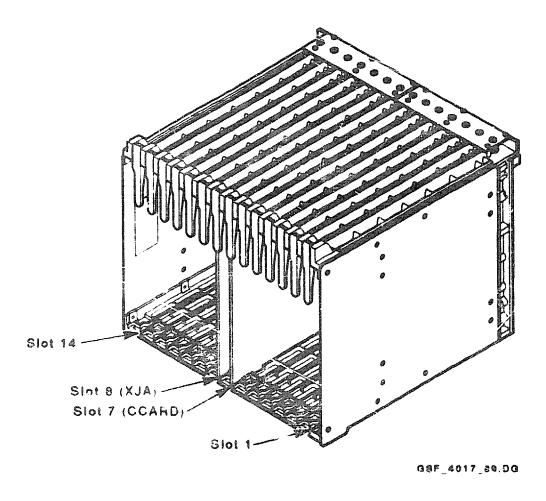

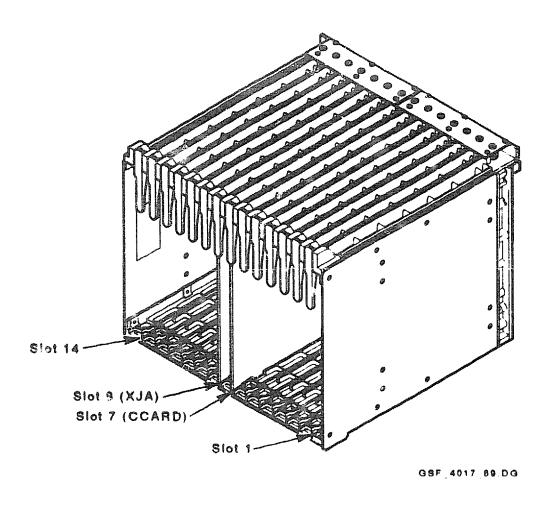

| 2–3   | XMI Card Cage, VAX 9000 System              | 2-4  |

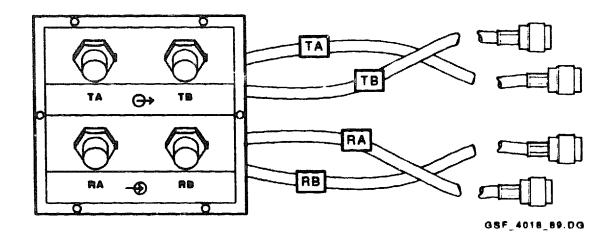

| 2-4   | I/O Connector Pins                          | 2-5  |

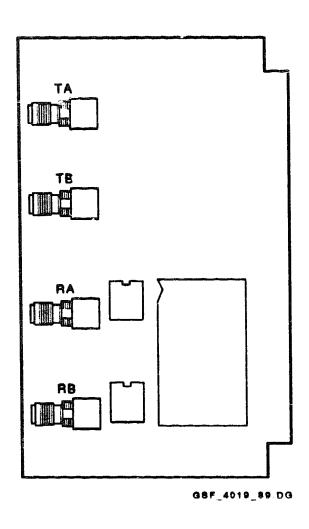

| 2–5   | XMI Corner                                  | 2-7  |

| 3-1   | XMI Address Space                           | 3-2  |

| 3–2   | I/O Space                                   | 3-3  |

| 3-3   | XMI Bus Signals for a Command/Address Cycle | 3-13 |

| 3-4   | Octaword Write Bus Cycles                   | 3-14 |

| 3-5   | Octaword Read Command/Address Cycle         | 3-15 |

| 3–6   | Octaword Read, Read Response Data Cycles    | 3-16 |

| 3–7   | Interlock Read Transaction                  | 3-17 |

| 3-8   | Unlock Write Transaction                    | 3-18 |

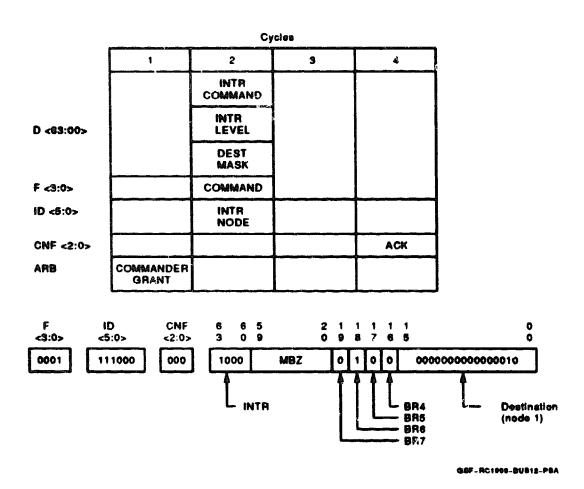

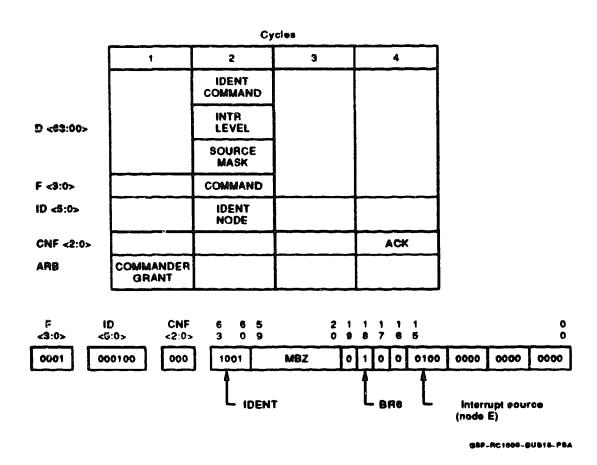

| 3-9   | INTR Transaction                            | 3-20 |

| 3–10  | IDENT Transaction                           | 3-21 |

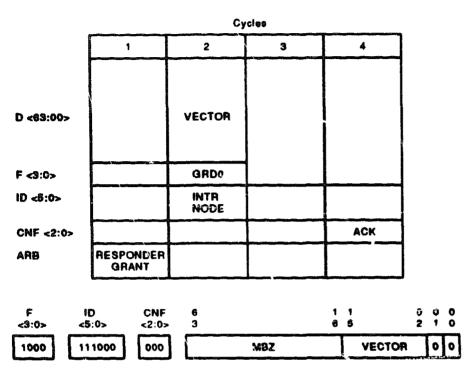

| 3-11  | IDENT Response                              | 3-22 |

| 3-12  | IVINTR Transaction                          | 3-23 |

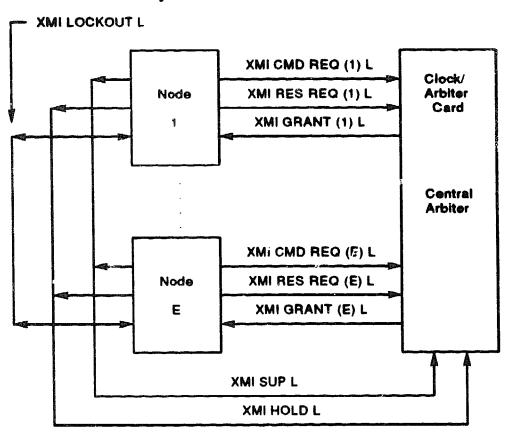

| 3-13  | Arbitration Block Diagram                   | 3-24 |

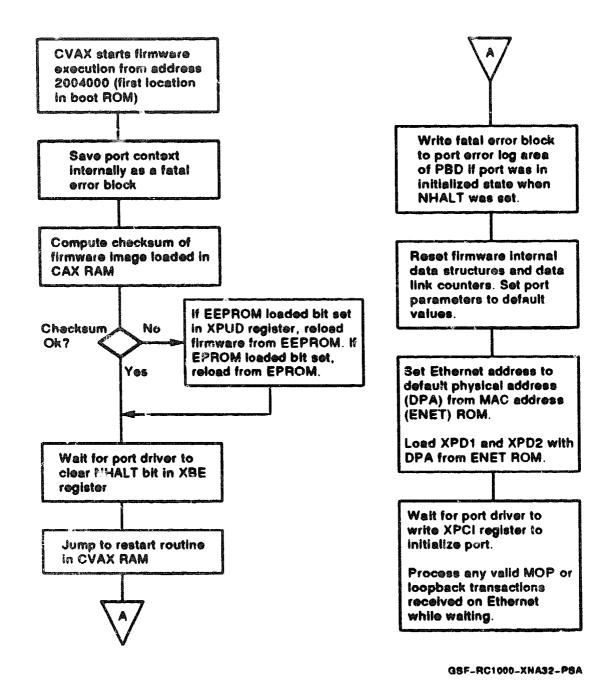

| 3-14  | Bus Initialization Flowchart                | 3-25 |

|       |                                             |      |

| Table | <b>2</b> 3                                  |      |

| 1-1   | XMI Bus Protocols                           | 16   |

| 1–2   | XMI Architecture Terms                      | 1-6  |

| 1-3   | XMI Bus Specifications                      | 1–8  |

| 1-4   | XMI Bandwidth                               | 1–€  |

| 3–1   | XMI I/O Space Regions                       | 3-2  |

| 3-2   | XMI Nodespace and I/O Space Allocations     | 3_4  |

| 3-3   | XMI Bus Signals                             | 3{   |

| 3-4   | Bus Function Codes                          | 3-6  |

| 3-5   | Bus Command Codes                           | 3_{  |

| 3-6   | Data Transfer Transactions                  |      |

#### vi Contents

| 3-7 | Interrupt Transactions                                  | 3–19 |

|-----|---------------------------------------------------------|------|

| 3-8 | Required and Recommended Registers                      | 3-26 |

| 4-1 | Memory Response Requirements to Bus Transactions        | 4-3  |

| 4-2 | Memory Actions on READs and WMASKs to Owned Blocks      | 4-4  |

| 4-3 | Write-back Cache Action in Response to Bus Transactions | 4-5  |

| 5-1 | XMI Bus Transaction Timeouts                            | 5-2  |

# **About This Manual**

#### Intended Audience

This handbook is part of a series of handbooks which comprise the XMI Adapters Handbook Documentation Set (EK-XMIAD-HB). This handbook and the handbook set are for VAX system trained Digital customer service personnel who service XMI-based systems and subsystems. Users of the handbook set should be familiar with the XMI bus architecture (either through the XMI Bus Concepts course or through practical experience) and have a minimum of level 1 hardware maintenance training on one or more VAX systems (for example, VAX 6000 or VAX 9000 systems).

### **Document Scope and Structure**

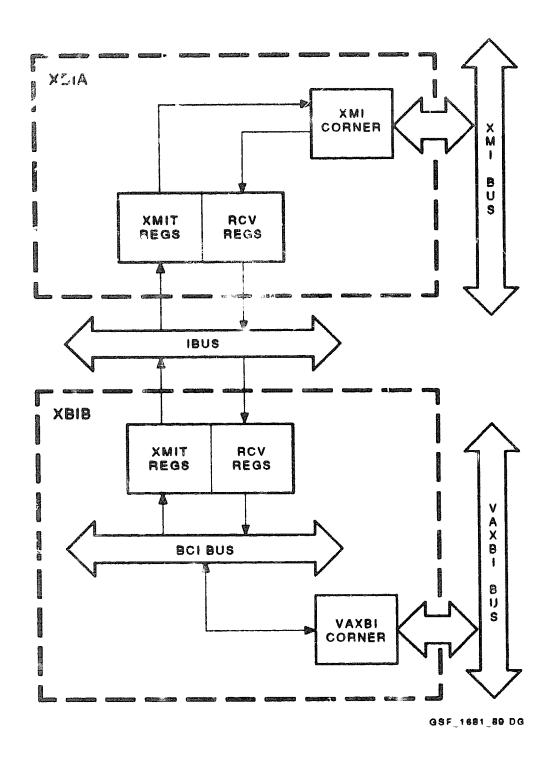

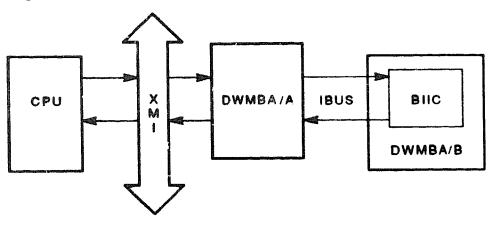

Several I/O adapters have been developed to interface the XMI bus to devices which employ different bus structures and protocols. These adapters are available as stand-alone options and may be installed on a variety of systems or subsystems.

The XMI Adapters Handbook Documentation Set provides a single, quick reference source to the type of information most frequently required to service XMI adapters. This handbook contains general information about the XMI bus and applies to all XMI adapters covered in the document set.

This handbook is divided into five chapters:

Chapter 1, XMI BUS OVERVIEW outlines the XMI bus architecture and describes XMI bus implementations, terms, and specifications.

Chapter 2, XMI BUS PHYSICAL DESCRIPTION reviews the XMI bus physical characteristic and general configuration rules.

Chapter 3, XMI BUS FUNCTIONAL DESCRIPTION presents the bus functional characteristics including bus addressing, function codes, and data transfer transactions.

Chapter 4, WRITE-BACK CACHE SUPPORT AND THE XMI+ PROTOCOL overviews the implementation of write-back cache in XMIbased systems. Chapter 5, DIAGNOSING XMI BUS RELATED ERRORS overviews the XMI bus error reporting and error handling mechanisms.

#### Conventions

addresses All addresses are given in hexadecimal (hex).

bits All bit numbers are given in decimal with the bit(s) enclosed in

angle brackets; for example <31>.

Multiple individual bits or bit fields are separated by commas with bit fields indicated by two numbers separated by a colon. For example <31:24,20,18,14:10> indicates bits 31 through 24 (inclusive), bit 20, bit 18, and bits 14 through 10 (inclusive).

CTRUX Specifies to press and hold the Ctrl key while pressing the

key; for example, CTRL/C]

[item] . . . Indicates the item is optional. The horizontal ellipsis indicates

that additional optional items can be entered.

Vertical ellipsis in examples, tables, or figures, indicates that

not all information is shown.

#### Related Documents

The XMI Adapters Handbook Documentation Set was written in conjunction with XMI adapter specific user's guides and technical descriptions. Each adapter specific handbook in the set contains a list of documents which the user can reference for more detailed information.

# 1 XMI BUS OVERVIEW

## 1.1 INTRODUCTION

The XMI bus is a limited length, synchronous, high-speed bus with centralized arbitration. The XMI is a pended bus (XMI nodes do not hold the bus waiting for a response) with multiplexed address and data lines.

Multiple transactions can be in progress at any time on the XMI, with arbitration and data transfer transactions occurring simultaneously.

## 1.2 IMPLEMENTATIONS

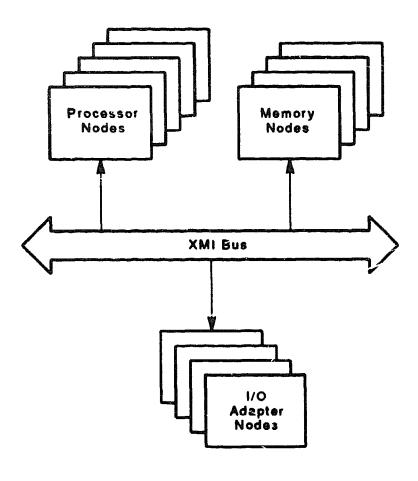

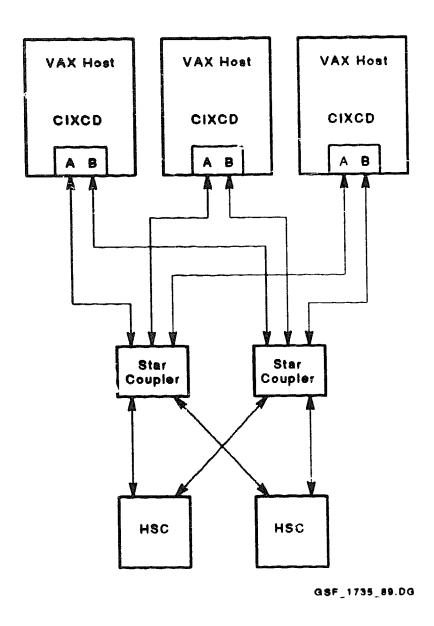

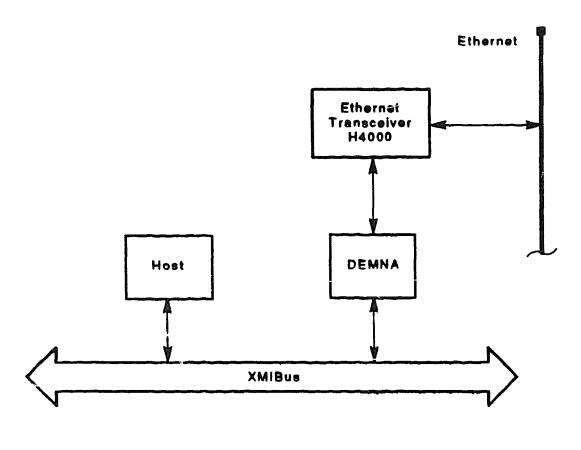

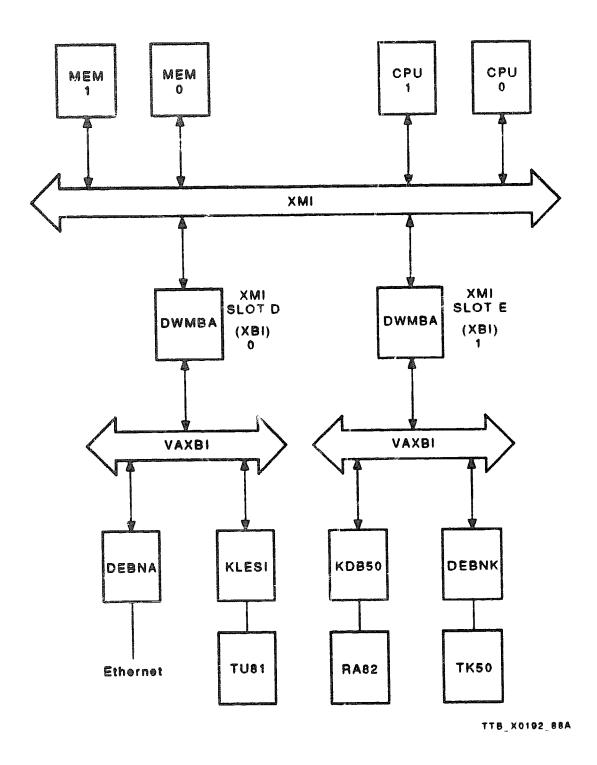

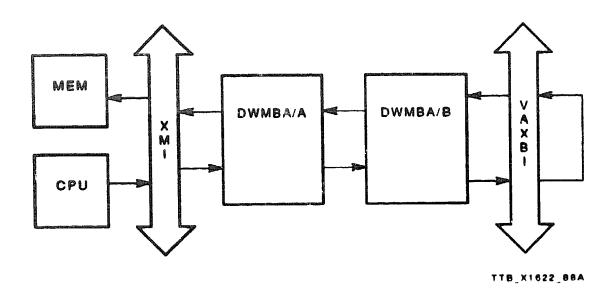

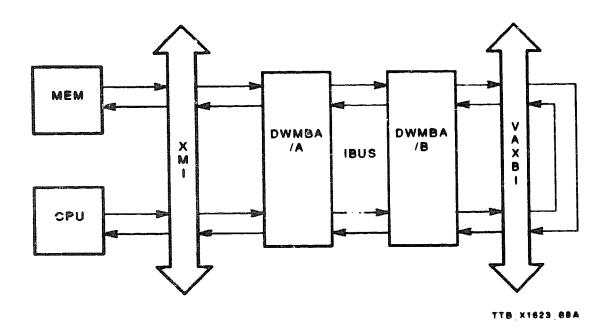

The XMI bus can be implemented as the primary system bus (for example, in most VAX 6000 systems) or as an I/O bus (for example, in VAX 9000 systems).

When used as the primary system bus, the XMI can support multiple processors, memory subsystems, and I/O adapters, in a variety of configurations, to a maximum of 14 nodes.

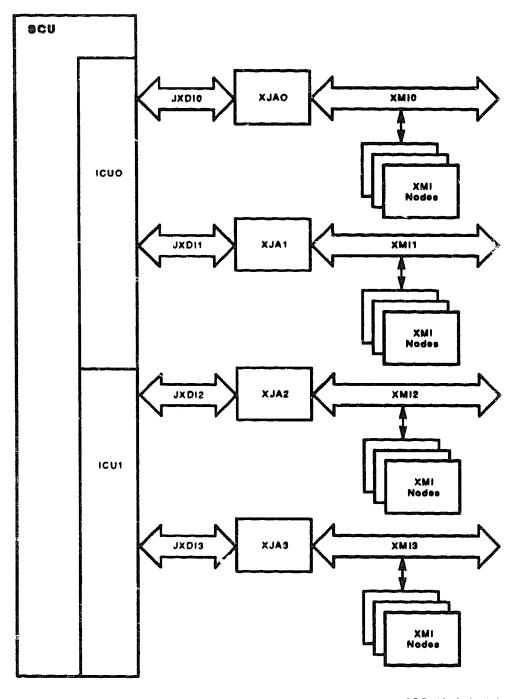

When used as an I/O bus, the XMI is interfaced to the system by way of an adapter. For example, in VAX 9000 systems, the XMI bus interfaces to the system by way of the XJA adapter, JXDI bus, and an I/O control unit.

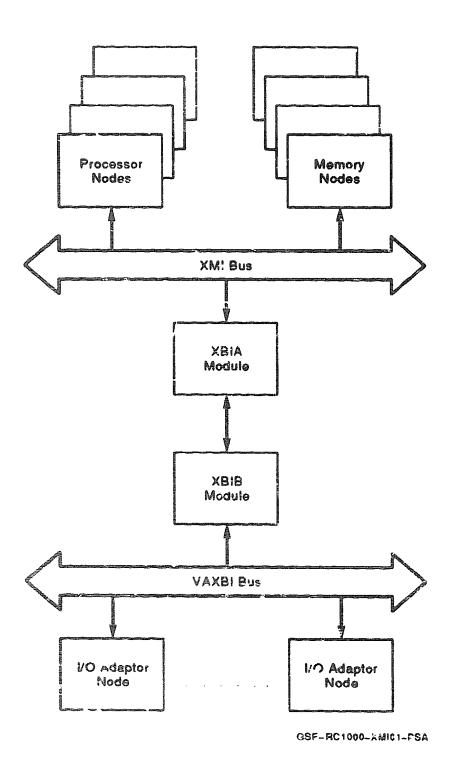

Figures 1-1, 1-2, and 1-3 show typical XMI bus implementations.

G9F\_1733\_89.DG

Figure 1-1 XMI Bus as the Primary System Bus

G8F\_4016\_89.DG

Figure 1-2 XMI Bus as an I/O Bus

Figure 1-3 XMi-Based System with VAXBI-Based I/O

# 1.3 BUS PROTOCOL

XMI bus operations are controlled by one of two protocols:

| Tehle            | 1_1 | YAMI   | Aug | <b>Protocols</b> |

|------------------|-----|--------|-----|------------------|

| S 400 B 47 B 400 |     | 24 142 |     |                  |

| Name | Description                                                               |                                                                                                    |  |  |  |

|------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|--|

| XMI  | Implements the basic set of XMI bus transactions:                         |                                                                                                    |  |  |  |

|      | Туре                                                                      | Transactions                                                                                       |  |  |  |

|      | Data Transfer                                                             | Read (READ) Interlocked read (IREAD) Write masked (WMASK) Unlock write masked (UWMASK)             |  |  |  |

|      | Interrupt                                                                 | Interrupt request (INTR) Interrupt acknowledge (IDENT) Implied vector interrupt (IVINTR)           |  |  |  |

| XMI+ | •                                                                         | II protocol. Includes three additional data transfer oport nodes which implement write-back cache: |  |  |  |

|      | Ownership read (OREAD) Disown write masked (DWMASK) Tag bad data (TBDATA) |                                                                                                    |  |  |  |

The bus protocol used on a given system depends on the type of nodes present in the XMI backplane. Systems which implement write-back cache use the XMI+ protocol.

# 1.4 TERMINOLOGY

Table 1-2 XMI Architecture Terms

| Torm                 | Definition                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Node                 | Hardware device that connects to the XMI backplane. A node can consist of one or more modules, but only one module may have an XMI corner.                                                                                                                                                                          |  |  |  |  |

| Transfer             | Smallest unit of information exchange that occurs on the XMI bus. For example, the command and data cycles of a read transaction and the command and data cycles of a write transaction are transfers.                                                                                                              |  |  |  |  |

| Transaction          | one or more transfer cycles which comprise the XMI task being performed. For example, a read transaction consists a command transfer followed some time later by a return ditransfer.                                                                                                                               |  |  |  |  |

| Commander            | Node that initiated the current transaction.                                                                                                                                                                                                                                                                        |  |  |  |  |

|                      | In a write transaction, the commander node is the source of the data to be transferred. In a read transaction, the commander is the node that requested the data.                                                                                                                                                   |  |  |  |  |

|                      | A node which initiates a transaction is considered to be the commander for the duration of the transaction. For example, on a read transaction, the commander initiates the transaction and the responder returns the data. During the return data transfer, the requesting node is still considered the commander. |  |  |  |  |

| Responder            | Node which is the target of a transaction request.                                                                                                                                                                                                                                                                  |  |  |  |  |

| Transmitter          | Node that is the source of the data on the bus.                                                                                                                                                                                                                                                                     |  |  |  |  |

|                      | For example, on a read transaction, the commander is the transmitter during the command transfer and the responder is the transmitter on the return data transfer.                                                                                                                                                  |  |  |  |  |

| Receiver             | Node that is the target of the data on the bus.                                                                                                                                                                                                                                                                     |  |  |  |  |

| Naturally<br>aligned | Data quantity whose address is an offset, from the beginning of memory, of an integral number of data elements of the same size.                                                                                                                                                                                    |  |  |  |  |

|                      | The low order address bits of naturally aligned data items are always zero. All XMI bus read and write transfers occur on naturally aligned blocks of data.                                                                                                                                                         |  |  |  |  |

| 648 | 8    |     | 200    |     |      |      |             |     |    |   |

|-----|------|-----|--------|-----|------|------|-------------|-----|----|---|

| _   |      |     |        |     |      |      |             |     |    | • |

| 78  | 2010 | 1-2 | (Com.) | XMI | Arci | nnec | <b>aure</b> | Ten | ms |   |

| Tara               | Definition                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wraperound<br>read | Octaword or hexword read operation in which read data is returned so that the originally requested quadword is returned first, independent of alignment. The remaining data in the naturally aligned block of data which contains the addressed quadword is returned in subsequent transfers. MMI has protocol requires that all octaword and hexword reads, both normal and interlocked, be wraparound reads.                    |

| Ownership          | On systems which implement the XMI+ (write-lack cache) protocol, each 32 byte block of data in memory has two associated status bits. These bits are used by memory to implement the XMI+ protocol.                                                                                                                                                                                                                               |

|                    | A node gains ownership of a block by performing an ownership read transaction (OREAD). After gaining ownership, the node is free to write to its local cache without transmitting a write to main memory. The node that owns a block must monitor the bus for attempts to read or write the block. If a WMASK reference is detected, the node must return the data to main memory using a disown write mask transaction (DWMASK). |

# **BUS INTEGRITY FEATURES**

The XMI bus contains several features that enhance the integrity and reliability of the bus.

- Parity protection for all bus information transfer lines

- ECC protection on all bus confirmation signals

- Bus protocol permits detection and correction of single-bit errors

- Defined timeout conditions to detect and diagnose faults

# 1.6 SPECIFICATIONS

## Table 1-3 XMI Bus Specifications

#### Physical

Backplane 14-slot card cage Nodes¹ Maximum of 14

Node ID: Hardwired to physical slot Bus langth Fixed, nonexpandable

Technology CMOS

#### Performance

Fius type Synchronous

Bus cycle 64 ns

Bus cycle 64 n

Address/data lines<sup>2</sup> 64

Address bits 40

Address space 1 terabyte (2<sup>40</sup> bytes)

Data transfer size 64 bits/cycle

Data transfer type<sup>2</sup> Pended

Bandwidth See Table 1-4

#### Arbitration

Type Centralized

Algorithm Modified round-robin

Cycles Concurrent with data transfers

Queues Two—commander, responder

<sup>&</sup>lt;sup>1</sup>The XMI architecture allows for up to 16 nodes, but current physical constraints limit the bus to 14 nodes.

Multiplexed address/data lines.

Pead- and interrupt-type transactions are pended (node does not hold bus while waiting for a response).

<sup>&</sup>lt;sup>4</sup>No dedicated arbitration cycles.

Table 1-4 XMI Bandwidth

| Data Size             | Read  | Write <sup>1</sup> |

|-----------------------|-------|--------------------|

| Longword <sup>2</sup> | 31.25 | 31.25              |

| Quadword              | 62.5  | 62.5               |

| Octaword              | 83.3  | 83.3               |

| Herword               | 100.0 | 100.0              |

Bandwidth values given in Mbytee/s.

<sup>&</sup>lt;sup>2</sup>The XMI architecture allows data transfers of all data sizes  $\approx$  both memory and I/O space. However, some implementations may not support transfers greater than a longword to I/O space.

# XMI BUS PHYSICAL DESCRIPTION

## 2.1 XMI CARD CAGE

The XMI card cage consists of a 14-slot backplane, connectors, card guides, and structural members. Each slot has a ZIF connector which is opened and closed by a cam actuator mechanism. This mechanism is sometimes called the card cage handle.

## 2.1.1 Backplane

There are two basic types of XMI backplanes:

- XMI-1, Figure 2-1

- XMI-2, Figure 2–2

The main differences between the two backplanes are that the XMI-2:

- Supplies more +3.3 Vdc current than does the XMI-1

- The increased current is provided to support more nodes with CMOS III logic. The additional current is supplied to each node by way of pins which are grounded on the XMI-1 backplane.

- Supplies battery backup power (if battery backup is present) for all backplane voltages

- The XMI-1 supplies battery backup only at +5.0 Vbb (see Figure 2-1). The +5.0 Vbb is separate from the +5.0 Vdc to allow backup power to memory and clocks without the need for supporting all XMI node logic.

On the XMI-2, if battery backup is present, it is available at all backplane voltages for all nodes.

Implementation of battery backup on either backplane is system specific.

• Includes two additional signals: XMI BP ID L and XMI PS EN H

These signals are both grounded on the XMI-1 backplane. See

Chapter 3 for signal descriptions.

Refer to system specific documentation for the type of backplane installed in a given system.

GSF-RC1000-BUS01-PSA

Figure 2-1 XMI-1 Backplane (+5.0 Vbb Power)

Figure 2-2 XMI-2 Backplane (+3.3 Vdc Power)

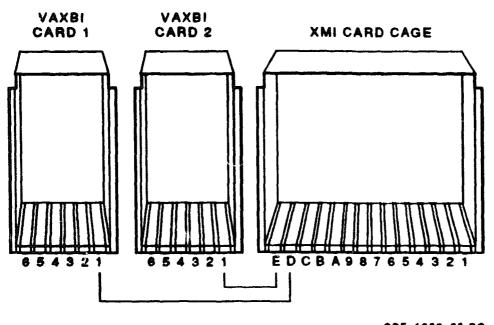

## 2.1.2 Node ID Numbers

XMI node ID numbers are hardwired on the XMI backplane. The node numbers correspond to the backplane slot numbers as shown in Figures 2–1 and 2–2.

### 2.1.3 Clock/Arbiter Card

In some implementations, the XMI system clock and bus arbiter are located on a daughter card which is attached to the XMI backplane. For example, Figures 2-1 and 2-2 show the location of the daughter card (DCARD) on VAX 6000 systems.

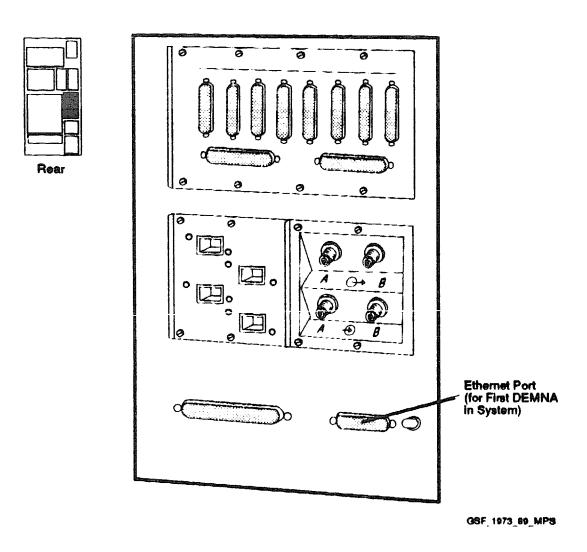

In other implementations, the clock/arbiter module is mounted in the card cage. Figure 2–3 shows the location of the clock/arbiter (CCARD) on VAX 9000 systems.

Figure 2-3 XMI Card Cage, VAX 9000 System

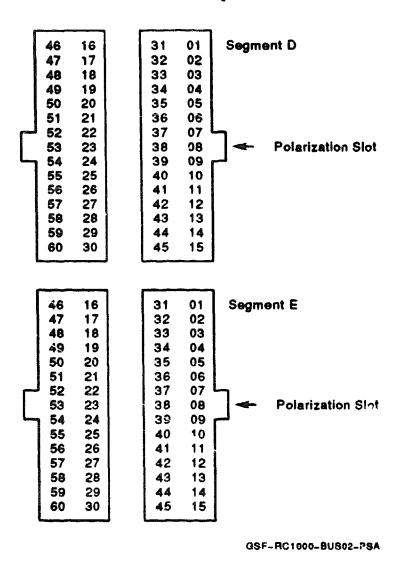

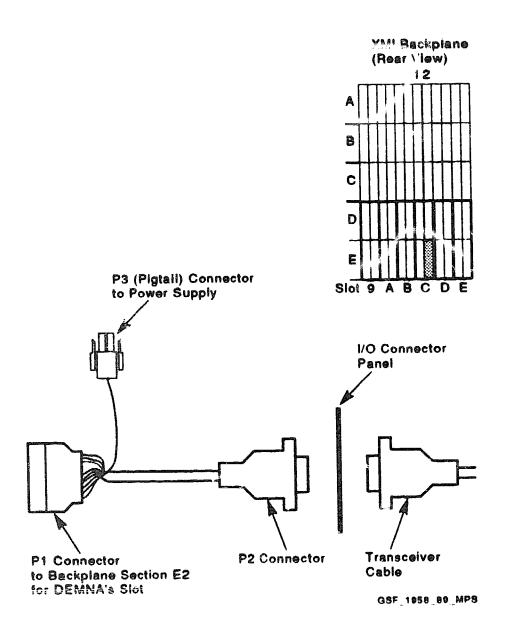

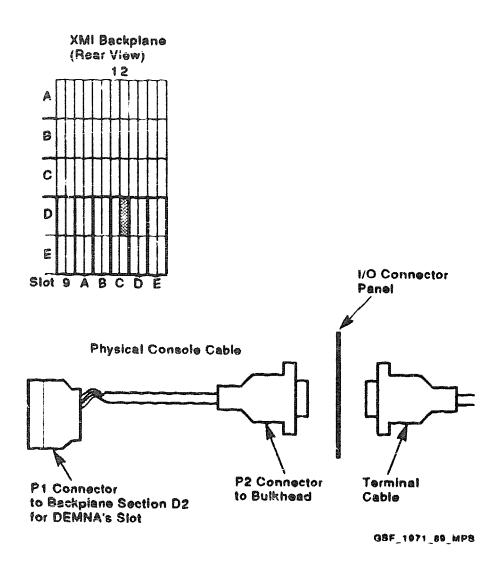

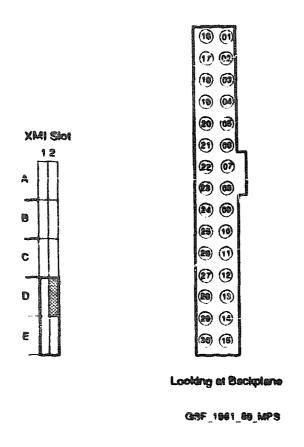

## 2.1.4 I/O Connector Pins

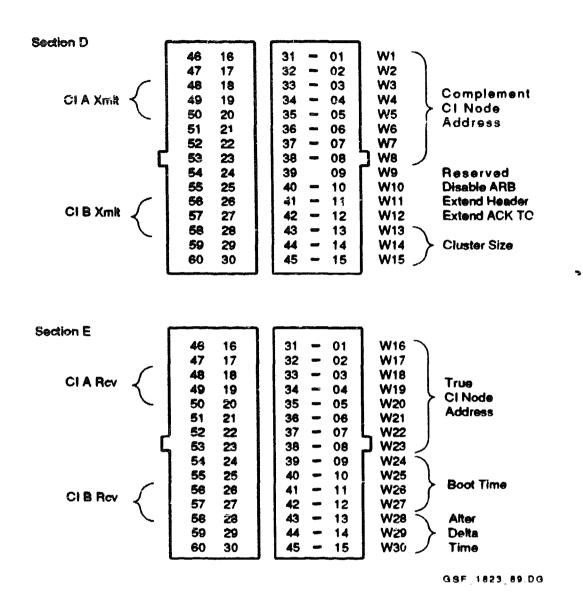

Segments D and E of each XMI backplane slot have connector pins for attaching I/O cables. Figure 2-4 shows the pin numbering layout. Refer 5 Section 2.3 for I/O node placement restrictions.

Figure 2-4 I/O Connector Pins

## 2.2 XMI NODE

An XMI node consists of one or more modules mounted in the card cage that interface to the bus via an XMI corner. If the node consists of more than one module, only one may have an XMI corner.

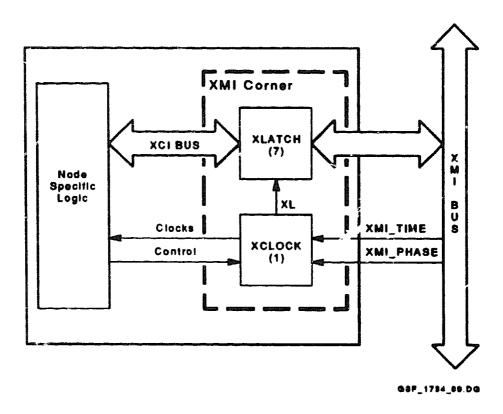

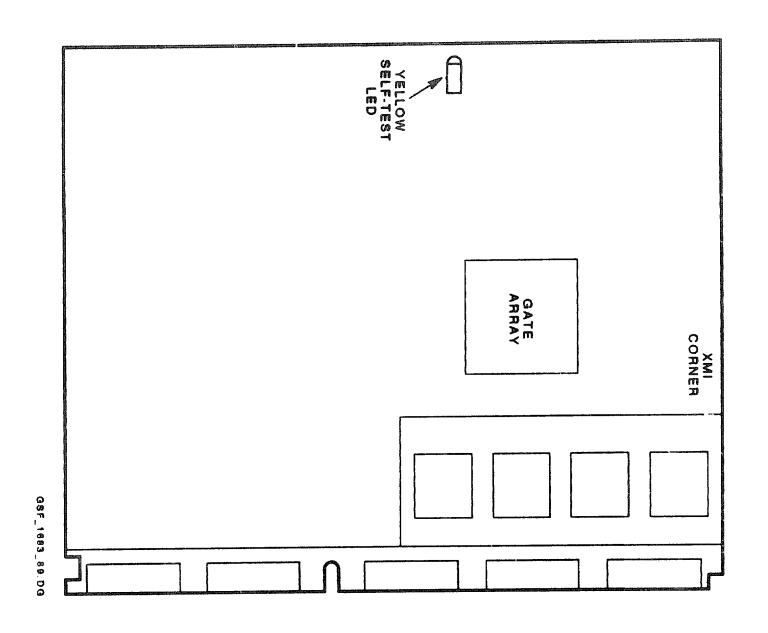

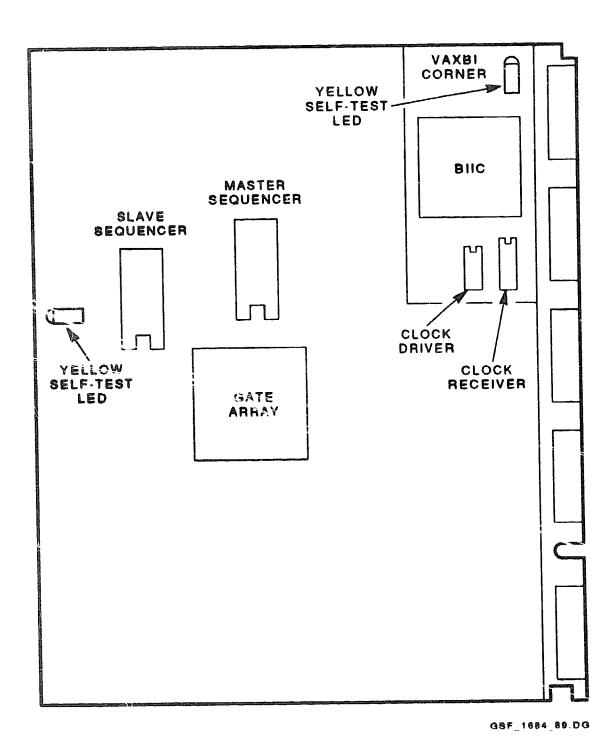

#### 2.2.1 XMI Corner

The XMI corner (Figure 2-5) contains custom logic that:

- Assures a standard electrical interface to the bus

- Buffers drive signals to the bus

- Buffers receive signals from the bus

The XMI corner occupies an area of approximately 4.45 cm  $(1.75 \text{ in}) \times 12.70 \text{ cm} (5.00 \text{ in})$  on the module and consists of eight Digital custom CMOS chips:

- Seven XLATCH chips

- One XCLOCK chip

Note that the XMI corner does not perform any node control functions. All node control functions are performed by the node-specific logic.

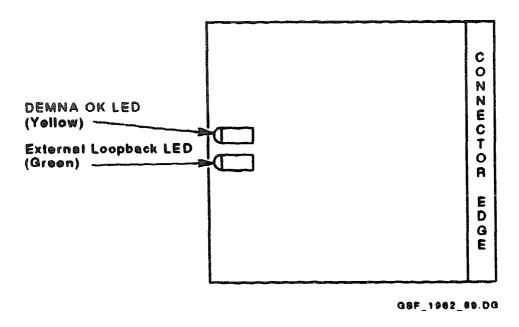

## 2.2.2 Self-Test LED

XMI nodes are required to have one yellow self-test pass (STP) LED to indicate the result of the node's self-test. This LED lights when self-test passes. The LED is located on the front edge of the module (the edge opposite the connectors) and is the only yellow LED on the module.

Figure 2-5 XMI Corner

#### **CONFIGURATION RULES** 2.3

The XMI backplane design places certain restrictions on the placement of modules in the XMI card cage.

Some implementations (for example, VAX 6000 systems) prohibit the placement of I/O nodes in slots 6 to 9 (or 5 to A, depending on the backplane type; see below) as the I/O connector pins for these slots are covered by the clock/arbiter card. In other implementations (for example, VAX 9000 systems) the clock/arbiter plugs into the card cage as any other node, allowing greater flexibility in the placement of I/O nodes.

The module placement restrictions for VAX 6000 and VAX 9000 systems are listed below. Refer to system specific documentation for details.

#### VAX 6000 Systems

- Slct 1 or E must contain a (non-memory) module

- No I/O adapter modules in slots 5 to A (XMI-1 backplane), slots 6 to 9 (XMI-2 backplane)

- CPU modules are typically installed beginning with slot 1

- Memory modules are placed in slots A to 5, then in slots B and C

- DWMBA adapters are installed in the left side of the card cage, beginning with slot E

#### VAX 9000 Systems

- Slot 1 or E must contain a (non-memory) module

- CCARD module is installed in slot 7

- XJA module is installed in slot 8

- First I/O adapter is installed in slot 1 or E

- Additional I/O adapters may be located in any other slot

## 2.4 MODULE PLACEMENT PRECAUTIONS

Some XMI modules (for example, the T2017 XRV) have components with heat sinks mounted on side 2 of the module. These components may cause mechanical or thermal interference problems with the module placed in the slot directly to their left in the card cage. Observe caution when installing or replacing a module adjacent to one with side 2 components.

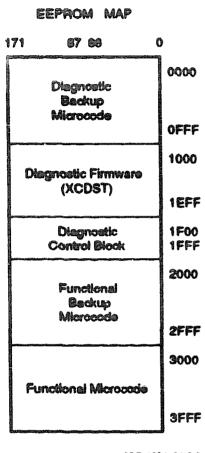

# XMI BUS FUNCTIONAL DESCRIPTION

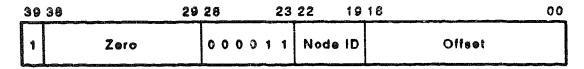

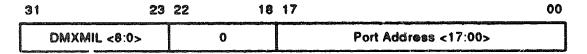

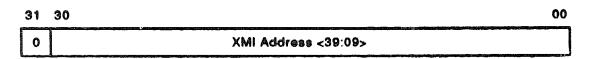

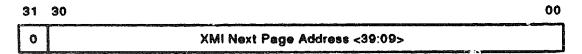

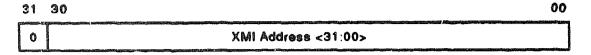

## 3.1 ADDRESSING

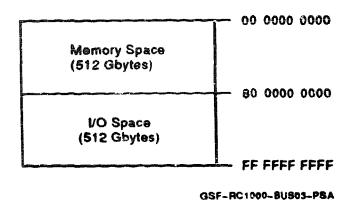

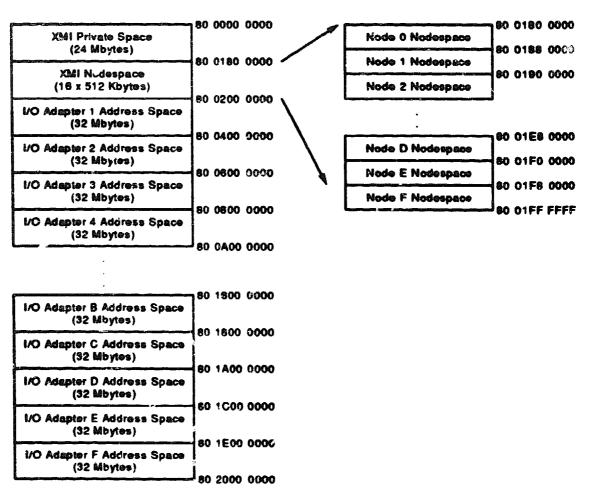

The XMI bus supports one terabyte ( $2^{40}$  bytes) of address space which individed into physical memory space and I/O space (Figure 3-1).

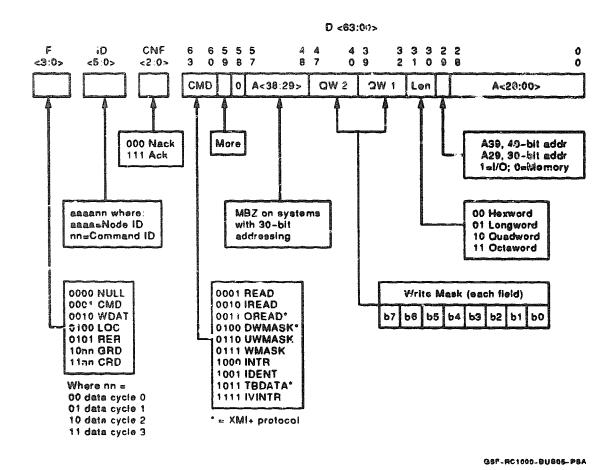

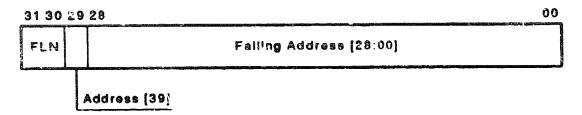

On a command/address cycle, XMI D<63:00>, which are multiplexed address/data lines, carry the forty bits of addressing, A<39:00>, as follows:

| XMI D<33:00> | Address bits |  |  |  |

|--------------|--------------|--|--|--|

| D<29>        | A<39>        |  |  |  |

| D<57∺3>      | A<38:29>     |  |  |  |

| D<28:00>     | A<28::00>    |  |  |  |

The most significant bit of the address, A<39>, selects between memory and I/O space:

A<39> = 0 memory space A<39> = 1 I/O space

#### NOTE

Some implementations of the XMI only support 30-bit addressing. These systems use internal address bit A<29>, which is output to the bus as XMI D<29>, to distinguish memory space from I/O space.

I/O space is further divided into private space, nodespace, and 15 I/O adapter address space regions. Figure 3-2 shows the I/O space divisions and Tables 3-1 and 3-2 describe the regions.

Figure 3-1 XMI Address Space

Table 3-1 XMI I/O Space Regions

| Region                       | Description                                                                                                                                                                                                                                                  |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Private space                | 24-Mbyte region reserved for operations local to the nodes. References to private space are serviced by resources local to a node, such as local device control and status registers (CSRs) and boot ROM. These references are not broadcast on the XMI bus. |

| Nodespace                    | 16, 512-Kbyte regions for node control and status<br>registers. Table 3–2 shows the address ranges.                                                                                                                                                          |

| I/O adapter<br>address space | 15, 32-Mbyte regions used for accessing XMI I/O adapters. Table 3–2 shows the address ranges. Note that node 0 does not have an I/O adapter address region.                                                                                                  |

#### XMI BUS FUNCTIONAL DESCRIPTION 3-3

08F-RC1000-BUGG4-PGA

Figure 3-2 I/O Space

Table 3-2 XMI Nodespace and I/O Space Allocations

|                | Nodespace           |                       | I/O Adapter Space    |                              |

|----------------|---------------------|-----------------------|----------------------|------------------------------|

| Node           | Begin               | End                   | Begin                | End                          |

| 01.2           | <b>80 0180 0000</b> | 80 <b>0187 FFFF</b>   | See footnote 2       |                              |

| 1              | 80 0188 0000        | 80 018F F <b>FF</b> F | 80 0200 0000         | 80 03FF FFFF                 |

| 2              | 80 0190 0000        | 80 0197 FFFF          | 80 0400 0000         | 80 05 <b>FF FFFF</b>         |

| 3              | 80 0198 0000        | 80 019F FFFF          | 80 0600 0000         | 80 07 <b>FF FFFF</b>         |

| 4              | 80 01A0 0000        | 80 01A7 FFFF          | 80 0800 0000         | 80 ooff ffff                 |

| 5              | 80 01A8 0000        | 80 01AF FFFF          | 80 0A00 0000         | 80 obff ffff                 |

| 6              | 80 01B0 0000        | 80 01B7 FFFF          | 80 OCOO 0000         | 80 odff ffff                 |

| 7              | 80 01B8 0000        | 80 01BF FFFF          | 80 0E00 0000         | 80 offf ffff                 |

| 8              | 80 01C0 0000        | 80 01C7 FFFF          | 80 1000 0000         | 80 11FF FFFF                 |

| 9              | 80 01C8 0000        | 80 01CF FFFF          | 80 1200 0000         | <b>8</b> 0 13 <b>FF FFFF</b> |

| A              | 80 01D0 0000        | 80 01D7 FFFF          | 80 1400 0000         | 80 15FF FFFF                 |

| B              | 80 01D8 0000        | 80 01DF FFFF          | 80 1600 0000         | 80 17FF FFFF                 |

| C              | 80 01E0 0000        | 80 01E7 FFFF          | 80 1800 0000         | 80 19FF FFFF                 |

| D              | 80 01E8 0000        | 80 01EF FFFF          | 80 1A00 0000         | 80 1BFF FFFF                 |

| E              | 80 01F0 0000        | 80 01F7 FFFF          | 80 1C00 0000         | 80 1DFF FFFF                 |

| F <sup>3</sup> | 80 01F8 0000        | 80 01 <b>FF FFFF</b>  | 80 1 <b>E00 0000</b> | 80 1FFF FFFF                 |

<sup>&</sup>lt;sup>1</sup>Node 0 nodespace is reserved for future expansion.

<sup>&</sup>lt;sup>2</sup>Node 0 does not have I/O adapter space; addresses in this range comprise XMI private space and XMI nodespace.

<sup>&</sup>lt;sup>3</sup>Reserved for future expansion.

## 3.2 BUS SIGNALS

Table 3-3 XMI Bus Signals

| Signal                   | Description                                                                                                                                                                      |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arbitration              |                                                                                                                                                                                  |

| XMI CMD REQn             | Commander bus request lines (n = node number)                                                                                                                                    |

| XMI RES REQn             | Responder bus request lines (n = node number)                                                                                                                                    |

| XMI GRANTn               | Bus grant lines ( $n = node number$ )                                                                                                                                            |

| KMI HOLD                 | Bus hold (multicycle transfers)                                                                                                                                                  |

| XMI SUP                  | Suppress initiation of new XMI transactions                                                                                                                                      |

| XMI LOCKOUT <sup>1</sup> | Prevent resource starvation (forces sequential access to shared resources)                                                                                                       |

| Information Transf       | er                                                                                                                                                                               |

| XMI D <63:00>            | Data cycles: read or write data<br>Command cycles: command, address, mask                                                                                                        |

| XMI F <03:00>            | Bus function (see Table 3–4)                                                                                                                                                     |

| XMI ID <05:00>           | Commander ID. Field is of the form AAAAnn where AAAA is the commander's node ID and nn is the command ID (each node can have up to 4 outstanding transactions at the same time). |

| XMI P <02:00>            | Parity of XMI D, XMI F, and XMI ID lines                                                                                                                                         |

| Response                 |                                                                                                                                                                                  |

| XMI CNF <02:00>          | Data transfer status confirmation (from receiver)                                                                                                                                |

|                          |                                                                                                                                                                                  |

<sup>&</sup>lt;sup>1</sup>Commander nodes assert XMI LOCKOUT when repeated attempts to perform hardware locks are denied, or repeated attempts to perform IDENTs or I/O space references are NOACKed. The assertion of LOCKOUT ensures fair access to resources by preventing nodes which have completed a lock, IDENT, or I/O reference from initiating another request while LOCKOUT is asserted. XMI LOCKOUT need only be generated and monitored by commander nodes that perform interlock reads, ownership reads, IDENTs, or I/O space references.

| Table | 3-3 | (Cont.) | MX ( | Bus | <b>Signals</b> |

|-------|-----|---------|------|-----|----------------|

|-------|-----|---------|------|-----|----------------|

| Signal                   | Description                                                                                       |

|--------------------------|---------------------------------------------------------------------------------------------------|

| Control                  |                                                                                                   |

| XMI AC LO                | Low ac line voltage                                                                               |

| XMI DC LO                | Impending loss of dc power                                                                        |

| XMI BAD                  | Node failure (asserted until all nodes pass self-test)                                            |

| XMI DEF [A,B]            | Defaults bus tristate lines during XMI idle cycles                                                |

| XMI ERR DEF              | Bus configuration defaulting check                                                                |

| XMI RESET                | Initialize system to power-up state                                                               |

| XMI TRIGGER <sup>2</sup> | Node detected significant event (specific to node)                                                |

| XMI TIME n               | XMI clock reference ( $n = 1$ to 15)                                                              |

| XMI PHASE n              | XMI clock phase reference ( $n = 1$ to 15)                                                        |

| XMI UPDATE EN            | Modification control for EEPROM or other writeable, non-volatile storage devices.                 |

|                          | UPDATE EN must be observed by all nodes that implement on-board, writeable, non-volatile storage. |

## Console and Front Panel<sup>3</sup>

| XMI CON XMIT    | Transmit data to console                                                                    |

|-----------------|---------------------------------------------------------------------------------------------|

| XMI CON RECV    | Receive data from console                                                                   |

| XMI CON SECURE  | Console secure (if XMI is system bus, disables CTRL/P detection)                            |

| XMT JOOT EN     | Auto-boot control (if XMI is system bus)                                                    |

| XMI RUN         | Front panel RUN LED control                                                                 |

| XMI TOY BBU PWR | Time of year clock BBU power                                                                |

| KMI TOY BBU OK  | TOY clock BBU status                                                                        |

| XMI BP ID       | Identifies the backplane type. Asserted on the XMI-1 backplane and deasserted or the XMI-2. |

<sup>&</sup>lt;sup>2</sup>This signal may be labeled as XMI FAULT on some implementations of the XMI bun.

<sup>&</sup>lt;sup>3</sup>Used only by CPU nodes

| Signal                 | Description                                                                                                                                                                                              |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Console and Fron       | t Panel <sup>2</sup>                                                                                                                                                                                     |

| XMI PS EN              | Ensures that the +3.3 Vdc power supply is not enabled if an XMI-1 style module is plugged into the XMI-2 style backplane (some pins used for +3.3 Vdc on the XMI-2 are grounded on XMI-1 style modules). |

| Miscellaneous          |                                                                                                                                                                                                          |

| XMI NODE ID<br><03:00> | Backplane wired node ID (for example, slot 1 = node 1)                                                                                                                                                   |

| XMI SPAREO             | Reserved                                                                                                                                                                                                 |

# 3.3 BUS FUNCTION CODES

Table 3-4 Bus Function Codes

| M | I F<8 | :0> |   |          |                              |

|---|-------|-----|---|----------|------------------------------|

| 8 | 2     | 1   | ð | Mnemonic | Function                     |

| 0 | 0     | 0   | 0 | NULL     | Null cycle                   |

| 0 | 0     | 0   | 1 | CMD      | Command cycle <sup>1</sup>   |

| 0 | 0     | 1   | 0 | WDAT     | Write data cycle             |

| 0 | 0     | 1   | 1 |          | Reserved (decoded as NULL)   |

| 0 | 1     | 0   | 0 | LOC      | Lock response                |

| 0 | 1     | 0   | 1 | RER      | Read error response          |

| 0 | 1     | 1   | 0 |          | Reserved (decoded as NULL)   |

| 0 | 1     | 1   | 1 |          | Reserved (decoded as NULL)   |

| 1 | 0     | 0   | 0 | GRD0     | Good read data, cycle 0      |

| 1 | 0     | 0   | 1 | GRD1     | Good read data, cycle 1      |

| 1 | 0     | 1   | 0 | GRD2     | Good read data, cycle 2      |

| 1 | 0     | 1   | 1 | GRD3     | Good read data, cycle 3      |

| 1 | 1     | 0   | 0 | CRDO     | Corrected read duta, cycle 0 |

| 1 | 1     | 0   | 1 | CRD1     | Corrected read data, cycle 1 |

| 1 | 1     | 1   | 0 | CRD2     | Corrected read data, cycle 2 |

| 1 | 1     | 1   | 1 | CRD3     | Corrected read data, cycle 3 |

<sup>&</sup>lt;sup>1</sup>See Table 3–5 for the encoding of XM! D<63:60> when XMI F<3:0> specifies a command cycle.

# 3.4 BUS COMMAND CODES

Table 3-5 Bus Command Codes

|    | D<6 | 3:80> |    |                     |                            |

|----|-----|-------|----|---------------------|----------------------------|

| 63 | 62  | 61    | 60 | Mnemonic            | Command                    |

| 0  | 0   | 0     | 0  | _                   | RESERVED (decode as NULL)  |

| 0  | 0   | 0     | 1  | READ                | Read                       |

| 0  | 0   | 1     | 0  | IREAD               | Interlock read             |

| 0  | 0   | 1     | 1  | OREAD <sup>1</sup>  | Ownership read             |

| 0  | 1   | 0     | 0  | DWMASK <sup>1</sup> | Disown write masked        |

| 0  | 1   | 0     | 1  | _                   | Reserved (decoded as null) |

| 0  | 1   | 1     | 0  | UWMASK              | Unlock write masked        |

| 0  | 1   | 1     | 1  | WMASK               | Write masked               |

| 1  | 0   | 0     | 0  | INTR                | Interrupt                  |

| 1  | 0   | 0     | 1  | IDENT               | Interrupt acknowledge      |

| 1  | 0   | 1     | 0  | _                   | RESERVED (decode as NULL)  |

| 1  | 0   | 1     | 1  | TBDATA <sup>1</sup> | Tag bad data               |

| 1  | 1   | 0     | 0  |                     | RESERVED (decode as NULL)  |

| 1  | 1   | 0     | 1  | ~                   | RESERVED (decode as NULL)  |

| 1  | 1   | 1     | 0  | ~                   | RESERVED (decode as NULL)  |

| 1  | 1   | 1     | 1  | IVINTR              | Implied vector interrupt   |

<sup>1</sup>XMI+ protocol only.

#### 3.5 DATA TRANSFER TRANSACTIONS

The XMI architecture supports data transfers of all data sizes to both memory and I/O space (some implementations may not support transfers greater than a longword to I/O space).

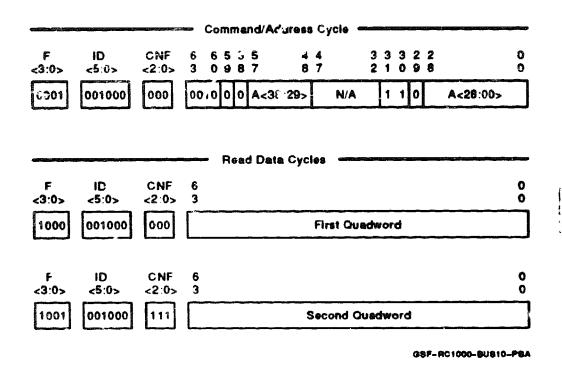

Table 3-6 overviews the data transfer transactions. Figures 3-3 to 3-8 show the command/address and data cycles of selected transactions.

Refer to Chapter 4 for memory response requirements on systems which support the XMI+ protocol.

Table 3-6 Data Transfer Transactions

| Туре                           | Description                                                                                                           |                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Read<br>(READ)                 | from the respon-<br>aligned and deli<br>transfers may be                                                              | Moves a longword, quadword, octaword, or hexword of data from the responder to the commander. Data are naturally aligned and delivered in wraparound order. Multiple transfers may be necessary to transfer all quadwords of an octaword or hexword transaction. |  |  |  |  |  |  |  |

| Interlocked<br>read<br>(IREAD) | memory determi                                                                                                        | IREADs to memory space are similar to READs except that memory determines if the transfer should continue based on the state of the block referenced:                                                                                                            |  |  |  |  |  |  |  |

|                                | Block State                                                                                                           | Memory Action                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                | Free                                                                                                                  | Locks the location from future IREADs and OREADs <sup>1</sup> and returns the requested data to the commander. The commander must issue an UWMASK to release the lock.                                                                                           |  |  |  |  |  |  |  |

|                                | Locked or Returns a LOC response to the owned requesting node and terminates the transaction; no data is transferred. |                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|                                | Most I/O nodes                                                                                                        | space are implementation dependent. treat IREADs the same as READs (and same as WMASKs).                                                                                                                                                                         |  |  |  |  |  |  |  |

|                                |                                                                                                                       | larity is implementation dependent. The orted granularity in memory space is                                                                                                                                                                                     |  |  |  |  |  |  |  |

<sup>&</sup>lt;sup>1</sup>XMI+ protocol.

| Table 3-6 (Cont.)                         | Data Transfer Transactions                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Туре                                      | Description                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Ownership<br>read<br>(OREAD) <sup>1</sup> | Moves a hexword block from memory to a caching node and flags the block as owned in memory. The owning node must issue a DWMASK to write the cached data back to memory and release ownership of the block.                                                                                                                             |  |  |  |  |  |  |

|                                           | Write-back cache nodes use OREADs to perform both writes, and reads with modify intent.                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|                                           | The XMI+ protocol supports hexword OREADs only.                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| Write masked<br>(WMASK)                   | Moves specific bytes in a longword, quadword, octaword, or hexword data block from the commander to the responder. The data block is naturally aligned and the bytes to be transferred are identified by a byte mask field.                                                                                                             |  |  |  |  |  |  |

|                                           | Write transactions are performed with one, two, or four consecutive data transfer cycles with no NULL cycles in between.                                                                                                                                                                                                                |  |  |  |  |  |  |

| Unlock<br>write masked                    | Complement of IREAD. Writes data to, and releases the lock on, a locked memory location.                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| (UWMASK)                                  | When a node issues an IREAD, it must unlock the memory structure when it is finished by issuing UWMASK with the data to be written. When memory receives the UWMASK, it unlocks the memory location and writes the data as requested. If UWMASK is directed to a currently unlocked location, memory performs a masked write operation. |  |  |  |  |  |  |

| Disown<br>write masked                    | Complement of ownership read. Writes data to an owned hexword block and returns the block to the "free" state.                                                                                                                                                                                                                          |  |  |  |  |  |  |

| (DWMASK) <sup>1</sup>                     | The XMI+ protocol requires write-back cache nodes to monitor the bus for references to owned memory blocks. If a node detects a transaction (read or write) to a block it owns, the node is required to immediately issue a DWMASK to write the cached data back to memory and release ownership of the block.                          |  |  |  |  |  |  |

|                                           | The XMI+ protocol supports quadword, octaword and hexword DWMASK transactions.                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

<sup>&</sup>lt;sup>1</sup>XM!+ protocol.

| Туре                                   | Description                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 'lag bad data<br>(TBDATA) <sup>1</sup> | Used in place of DWMASK by write-back cache nodes if cached data is corrupted. Flags the corresponding memory location as bad.                                                                                                                                                                                                                                     |

|                                        | Write-back cache nodes implement error correcting code (ECC) on cached data. If a double bit error is detected, a TBDATA is issued in place of DWMASK to flag the data as bad to future references. Tagging a location as bad allows corrupted data to be more readily associated with an actual process since the first read reference to the location will fail. |

|                                        | The XMI+ protocol supports quadword, octaword and hexword TBDATA transactions.                                                                                                                                                                                                                                                                                     |

Figure 3-3 XMI Bus Signals for a Command/Address Cycle

| _         |               |                            | 8us (              | Cycles             |     |     |

|-----------|---------------|----------------------------|--------------------|--------------------|-----|-----|

|           | 1             | 2                          | 3                  | 4                  | 5   | 6   |

|           |               | WRITE<br>MASKED<br>COMMAND |                    |                    |     |     |

|           |               | MORE                       | WDITE              | MOITE              |     |     |

| D <63:00> |               | WRITE<br>ADDRESS           | WRITE<br>DATA<br>0 | WRITE<br>DATA<br>1 |     |     |

|           |               | WRITE<br>MASK              |                    |                    |     |     |

|           |               | LENGTH                     |                    |                    |     |     |

| F <3:0>   |               | COMMAND                    | WRITE<br>DATA      | WRITE<br>DATA      |     |     |

| ID <5:0>  |               | CMDR                       |                    |                    |     |     |

| CNF <2:0> |               |                            |                    | ACK                | ACK | ACK |

| ARB       | CMDR<br>GRANT | HOLD                       | HOLD               |                    |     |     |

QSF-RC1000-BUS08-PSA

|                             | Command/Address Cycle                              |         |

|-----------------------------|----------------------------------------------------|---------|

| F ID CNF <3:0> <5:0> <2:0>  | 6 6 5 5 5 4 4 3 3 3 2 2<br>3 0 9 8 7 8 7 2 1 0 9 8 | 0       |

| 0001 001000 000             | 0111 1 0 A<38:29> All 1s 1 1 0 A<28:0>             |         |

|                             | Write Data Cycles                                  | شبواشيا |

| F ID CNF <3:0> <5:0> <2:0>  | 6<br>3                                             | û<br>O  |

| 0010 001000 000             | First Quadword                                     |         |

| F '5' CNF <3:0> <5:0> <2:0> | 6<br>3                                             | 0       |

| 0010 001000 1111            | Second Quadword                                    | ٻُ      |

GSF-RC1000-9US07-PSA

Figure 3-4 Octaword Write Bus Cycles

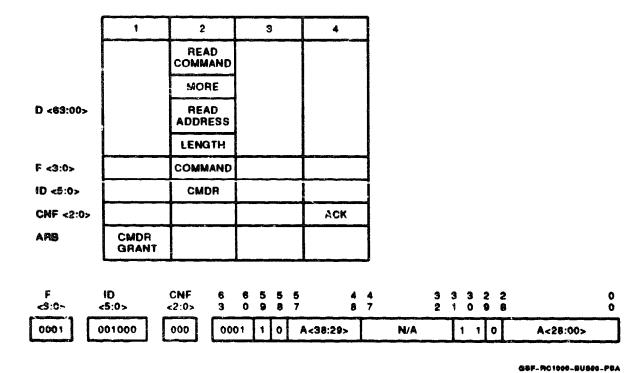

Figure 3-5 Octaword Read Command/Address Cycle

|           | n                   | n+1               | n+2             | n+3               | n+4   | ก+5 |   |  |  |  |

|-----------|---------------------|-------------------|-----------------|-------------------|-------|-----|---|--|--|--|

| D <63:00> |                     | READ<br>DATA<br>0 |                 | READ<br>DATA<br>1 |       |     |   |  |  |  |

| F <3:0>   |                     | GRD0              |                 | GRD1              |       |     |   |  |  |  |

| ID <5:0>  |                     | CMDR              |                 | CMDR              |       |     |   |  |  |  |

| CNF <2:0> |                     |                   |                 | ACK               |       | ACK |   |  |  |  |

| ARB       | RSPNDR<br>GRANT     |                   | RSPNDR<br>GRANT |                   |       |     |   |  |  |  |

| <3:0> <   | <3:0> <5:0> <2:0> 3 |                   |                 |                   |       |     |   |  |  |  |

|           |                     | NF 6:0> 3         |                 |                   |       |     | 0 |  |  |  |

| 1001      | 01000 1             | 11]               | 9               | econd Que         | dword |     |   |  |  |  |

|           |                     |                   |                 |                   |       |     |   |  |  |  |

@9F-RC1000-BUS09-PSA

Figure 3-6 Octaword Read, Read Response Data Cycles

Figure 3-7 Interlock Read Transaction

#### NOTE

Interlock reads are similar to normal reads except that the memory location is locked and MORE is not allowed. See Figures 3-5 and 3-6.

If the target address is currently locked, memory will respond with the lock response (F <3:0> = 0100) and the XMI data lines (D <63:00>) are ignored.

#### 3-18 XMI BUS FUNCTIONAL DESCRIPTION

| condensation with a |             |              | er armited by | Co | mn     | n e    | nd/    | Address     | Су       | cie —   |    | · wyskin | To the last |   | estation in |          | طرسوال |

|---------------------|-------------|--------------|---------------|----|--------|--------|--------|-------------|----------|---------|----|----------|-------------|---|-------------|----------|--------|

| ₹<br><3:0>          | ID<br><5:0> | CNF<br><2:0> | 6<br>3        | 6  | 5<br>9 | 5<br>8 | 5<br>7 | 4<br>8      | 4        |         |    | _        | 3           | _ | -           |          | 0      |

| 0001                | 001000      | 000          | 01            | 10 | 0      | 0      | A<     | 38:29>      | w        | rite Ma | k  | 1        | 0           | 0 |             | A<28:00> |        |

| F<br><3:0>          | ID<br><5:0> | CNF<br><2:0> | 6 3           | •  | W      | rit    | e D    | eta Cyc     | المدودات |         |    |          |             |   |             |          | 0      |

| 0010                | 001000      | 000          |               |    |        |        |        | <del></del> |          | Quedwo  | rd |          |             |   |             |          |        |

G8F-RC1000-BUS11-PSA

Figure 3-8 Unlock Write Transaction

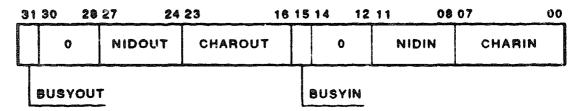

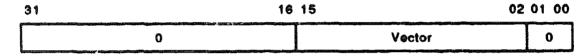

# 3.6 INTERRUPT TRANSACTIONS

Table 3\_7 Internet Transactions

| Neme                     | Mnom   | Description                                                                                                                                                                                                                    |  |  |  |  |  |  |

|--------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Interrupt<br>request     | INTR   | Issued by I/O nodes to interrupt instruction execution in a processor (or processors) at a specified IPL.                                                                                                                      |  |  |  |  |  |  |

|                          |        | Interrupt requests can be broadcast to multiple processor nodes. The first processor responding with IDENT receives the interrupt vector; all other processors clear the interrupt pending condition.                          |  |  |  |  |  |  |

| Interrupt<br>acknowledge | IDENT  | Issued by a processor in response to an INTR transaction to request an interrupt vector.                                                                                                                                       |  |  |  |  |  |  |

|                          |        | If IDENTs are issued simultaneously by two or<br>more processors, the first to gain the bus services<br>the interrupt; the other processors force a passive<br>release.                                                        |  |  |  |  |  |  |

| Implied vector interrupt | IVINTR | Issued by a node to implement a single-cycle interrupt transaction. The interrupt priority and the interrupt vector value are implied by bits encoded in the interrupt type field.                                             |  |  |  |  |  |  |

|                          |        | The IVINTR is used for interprocessor interrupts and write error interrupts. Since the interrupt priority and vector are indicated in the transaction, an IVINTR does not require a corresponding interrupt acknowledge cycle. |  |  |  |  |  |  |

Figure 3-9 INTR Transaction

Figure 3-10 IDENT Transaction

627-R61000-BUS14-PBA

Figure 3-11 IDENT Response

@9F-RC1000-BUS18-PQA

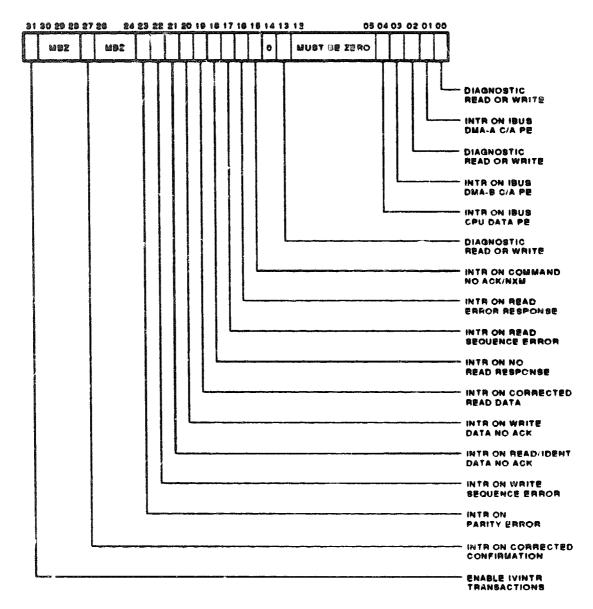

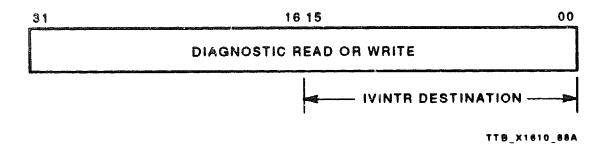

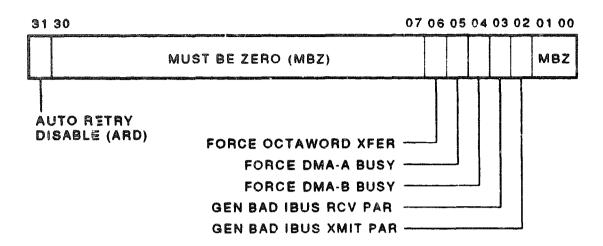

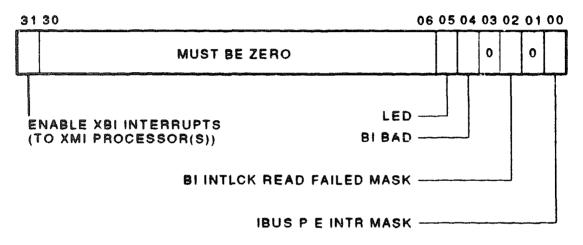

Figure 3-12 IVINTR Transaction

# 3.7 ARBITRATION

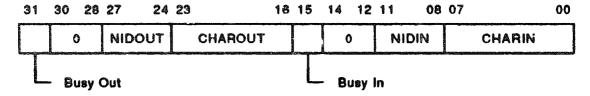

The XMI arbiter logic<sup>1</sup> has two independent arbitration queues: one for commanders and one for responders. Arbitration for each queue is performed in a round-robin manner, with responder requests receiving higher priority than commander requests.

Figure 3-13 shows the XMI arbitration logic. Note that with a set of dedicated arbitration lines, XMI bus arbitration cycles occur in parallel with data transfer cycles.

GSF\_RC1000-BUS16-PSA

Figure 3-13 Arbitration Block Diagram

<sup>&</sup>lt;sup>1</sup> DCARD on VAX 6000 systems; CCARD on VAX 9000 systems.

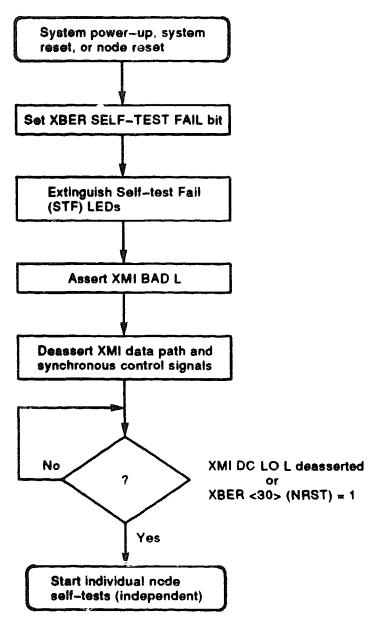

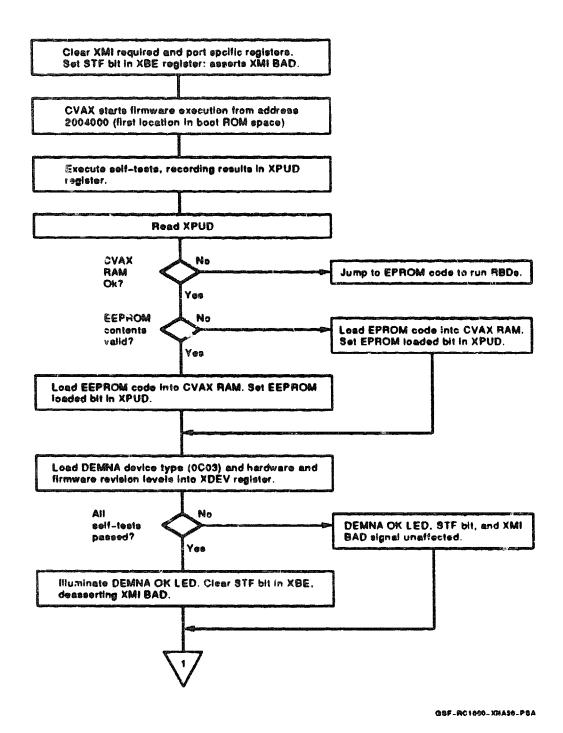

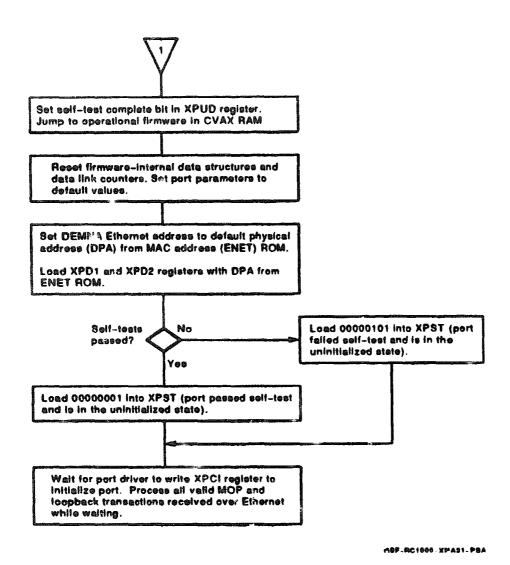

# 3.8 BUS INITIALIZATION

GSF-RC1000-BUS17-PSA

Figure 3-14 Bus Initialization Flowchart

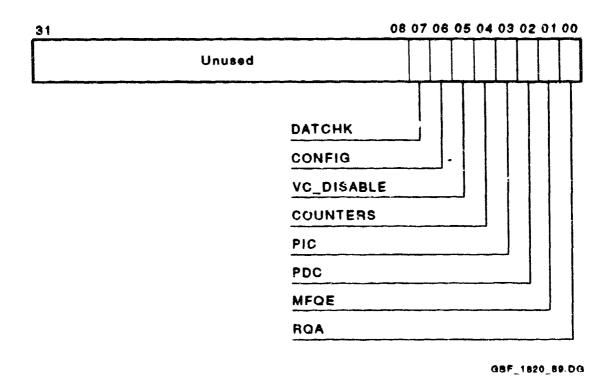

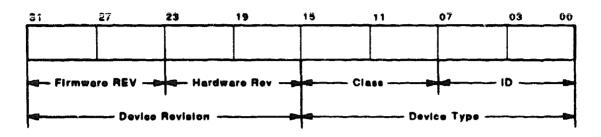

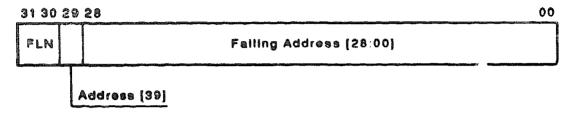

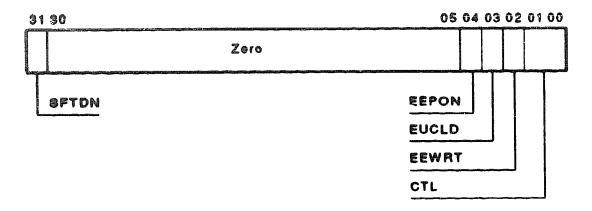

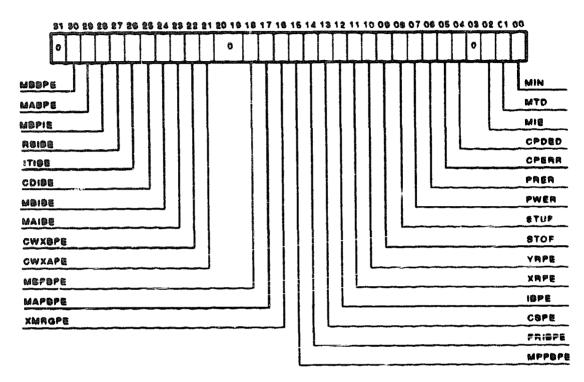

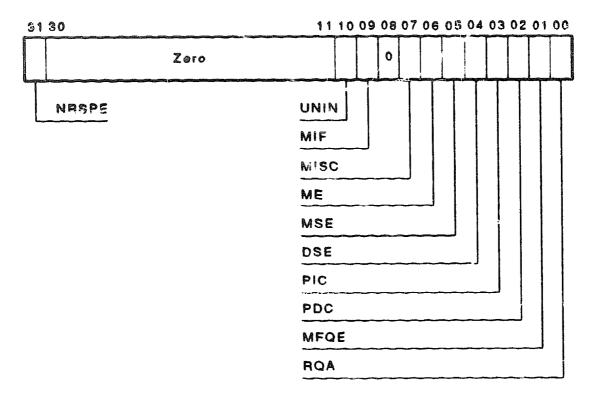

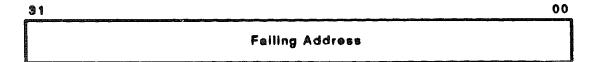

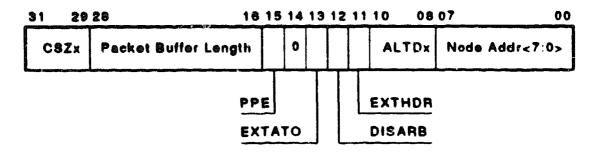

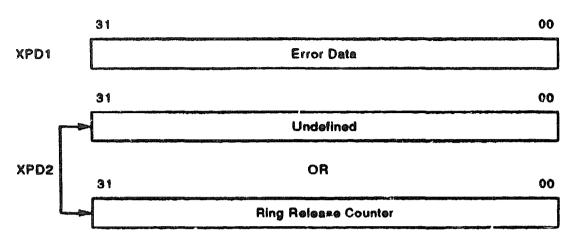

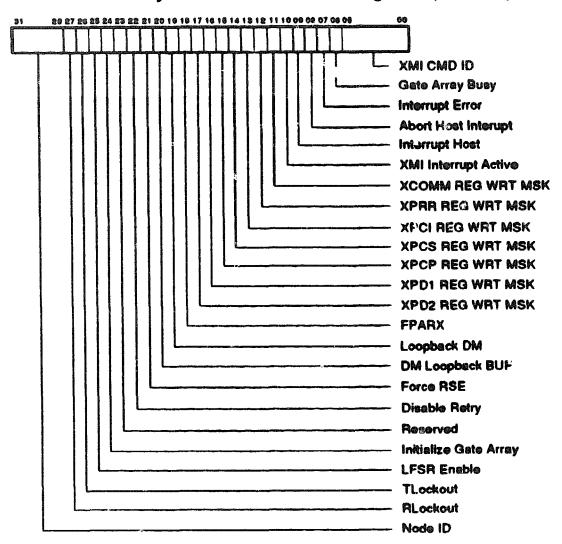

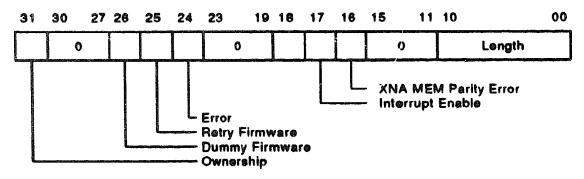

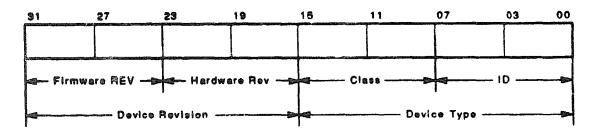

# 3.9 XMI NODE REQUIRED REGISTERS

The XMI architecture requires that each node include certain registers in specific locations in the node's nodespace:

Table 3-8 Required and Recommended Registers

| Register Name             | Mnem  | Addr <sup>1</sup> | Status                  |

|---------------------------|-------|-------------------|-------------------------|

| Device type               | XDEV  | bb+00             | Required                |

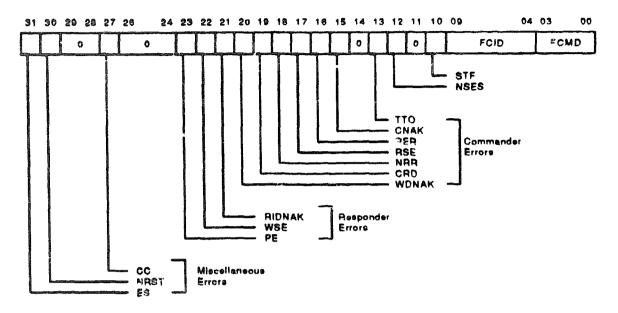

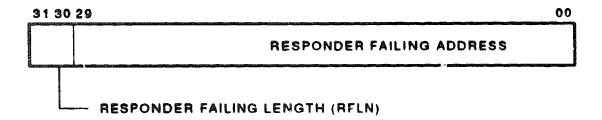

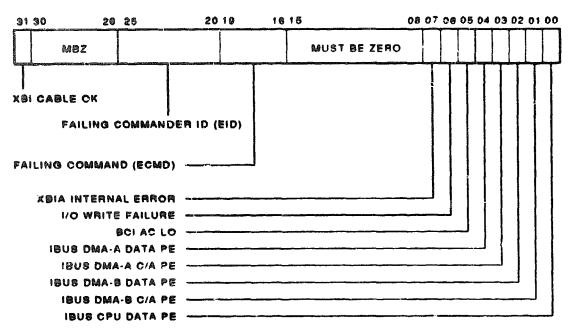

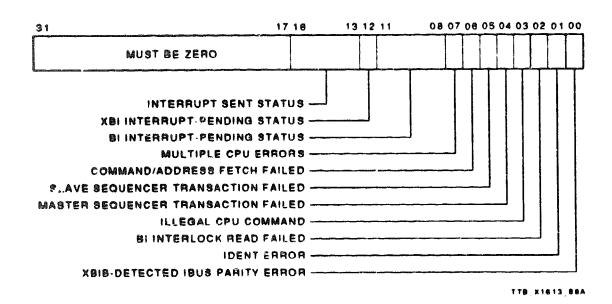

| Bus error                 | XBE   | bb+04             | Required                |

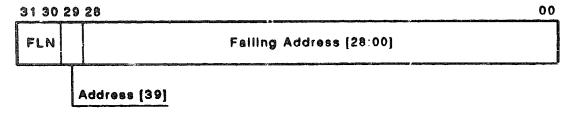

| Failing address           | XFADR | bb+08             | Required for commanders |

| Communication             | XCOMM | bb+10             | Recommended for RBD     |

| Failing address extension | XFAER | bb+2C             | Required for commanders |

<sup>&</sup>lt;sup>1</sup>Offset from base address. See Figure 3-2, and Tables 3-1 and 3-2.

Refer to the adapter specific handbooks of the XMI Adapters Handbook Documentation Set for descriptions of the XMI required and adapter specific registers.

# WRITE-BACK CACHE SUPPORT AND THE XMI+ PROTOCOL

#### 4.1 WRITE-BACK CACHE OVERVIEW

Write-back cache enhances system performance by increasing the effective bandwidth of memory write operations. With write-back cache, memory writes, in addition to reads, can be serviced locally by a caching node without the need for generating immediate main memory references. This reduces the overall number of memory writes that we ded otherwise be required.

#### NOTE

In this chapter, the term "XMI+ memory" will be used to denote memory nodes which support the XMI+ protocol.

# 4.1.1 Block Ownership

The implementation of write-back cache on systems which support the XMI+ protocol is based on the "ownership" of data in memory.

XMI+ memory maintains two state bits for each 32 byte block (hexword) of data (see Section 4.2). At any given time, any node on the bus can own any block. The XMI+ protocol ensures that only one node will own a given block at a given time.

# 4.1.2 Gaining Block Ownership

A node gains block cwnership by performing an ownership read (OREAD) transaction. During the time a node owns a block, it is free to write the block without generating main memory transactions. Once a node writes a block in its local cache, the block is considered "dirty" in that only the caching node has the updated data; main memory has the criginal data.

#### 4.1.3 Bus Monitoring

The XMI+ protocol requires write-back cache nodes to monitor the bus for references to memory blocks owned by the node.

If an IREAD or OREAD is issued to a location owned by another node, KMI+ memory will return a locked (LOC) response to the commander. When the owning node detects a reference, it must immediately issue a DWMASK to write the cached data back to memory and release the block.

See Table 4-1 for XMI+ memory responses to bus transactions and to Table 4-3 for the actions taken by the owning node.

# 4.1.4 Releasing Ownership

A node releases block ownership by issuing a disown write mask (DWMASK) or tag bad data (TBDATA) transaction. Once the node writes the data back to memory and releases the block, read references to the block by other nodes result in the updated data being returned by memory. (This assumes that no other node wrote to the block between the OREAD and DWMASK; see Section 4.2.3.)

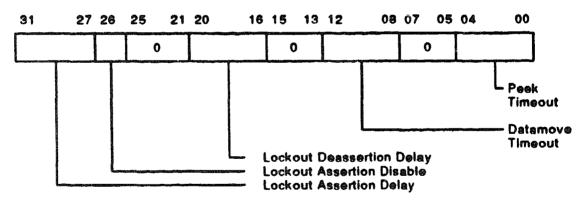

#### **4.2 MEMORY REQUIREMENTS**

The XMI+ protocol places certain constraints on memory to support write-back cache. This section overviews the major considerations.

#### 4.2.1 Block State

The XMI+ protocol requires memory to maintain two state bits for each heaword block of data. At any given time, a block in memory can be in one of four states:

| State         | Block Status                                                                                        |

|---------------|-----------------------------------------------------------------------------------------------------|

| Free          | Neither owned or locked                                                                             |

| Locked        | Interlocked as a result of an IREAD                                                                 |

| Owned         | Owned by a write-back cache node as a result of an OREAD                                            |

| Tagged<br>bad | Contains corrupted data. (A caching node wrote back corrupted data and tagged the location as bad.) |

The current block state determines memory's response to data transfer transactions. Table 4-1 lists the possible responses.

Table 4-1 Memory Response Requirements to Bus Trail sactions

|         | Block State <sup>1</sup> |                       |                    |                    |  |

|---------|--------------------------|-----------------------|--------------------|--------------------|--|

| Command | Free                     | Locked                | Owned              | Tagged Bad         |  |

| READ    | GRD                      | GRD                   | GRD                | RER                |  |

| IREAD   | GRD(L)                   | LOC                   | LOC                | RER                |  |

| OREAD   | GRD(O)                   | LOC                   | LOC                | RER                |  |

| WMASK   | Write                    | Write                 | Write              | Write              |  |

| UWMASK  | Write <sup>2</sup>       | Write(F)              | Write <sup>2</sup> | Write <sup>2</sup> |  |

| DWMASK  | Write(F)2                | $Write(F)^2$          | Write(F)           | Write <sup>2</sup> |  |

| TBDATA  | Write(B)2                | Write(B) <sup>2</sup> | Write(B)           | Write <sup>2</sup> |  |

<sup>&</sup>lt;sup>1</sup>Letter in parentheses indicates the next state if it is different from the current state: F = free, L = locked, O = owned, and B = tag bad.

# 4.2.3 Servicing READ and WMASK Transactions

Under the XMI+ protocol, owned memory locations cannot be read or written by another node until released (disowned) by the owning node. To accommodate READ and WMASK transactions to owned blocks, without the need for considering data ownership, XMI+ memory includes buffers and command queues. This allows memory to buffer writes, and defer reads, to owned locations until the data has been written back.

Table 4-2 lists the actions taken by XMI+ memory on READs and WMASKs to owned locations.

<sup>&</sup>lt;sup>2</sup>Error condition.

Table 4-2 Memory Actions on READs and WMASKs to Owned Blocks

| 18019 4-2 | 2 Memory Actions on READS and WMASKS to Owned Bloc                                                                                                                                                                                                                                                                   |  |  |  |  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Command   | Memory Actions                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| READ      | On a READ to an owned location, memory:                                                                                                                                                                                                                                                                              |  |  |  |  |

|           | 1. Stores the command, address, and ID in a deferred queue                                                                                                                                                                                                                                                           |  |  |  |  |

|           | 2. Waits for the owning node to issue DWMASK                                                                                                                                                                                                                                                                         |  |  |  |  |

|           | 3. Processes the DWMASK with any required masking as indicated by the associated write buffer (if any; see WMASK actions below)                                                                                                                                                                                      |  |  |  |  |

|           | 4. Processes all deferred reads that match the DWMASK address and returns the data with the appropriate response to the commander                                                                                                                                                                                    |  |  |  |  |

|           | The order in which reads are processed is not critical except that all deferred reads to the DWMASK address must be processed before continuing with other commands.                                                                                                                                                 |  |  |  |  |

| WMASK     | On a WMASK to an owned location, memory:                                                                                                                                                                                                                                                                             |  |  |  |  |

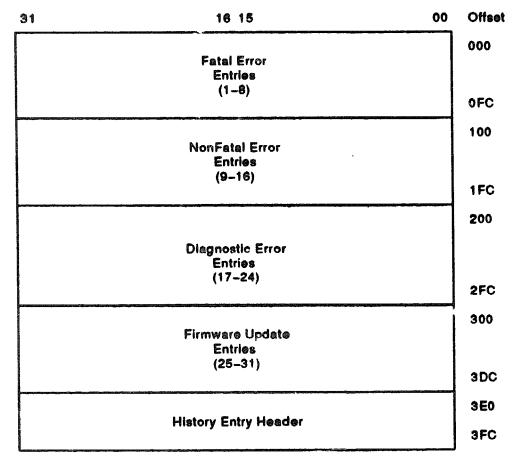

|           | 1. Immediately writes the data into the block                                                                                                                                                                                                                                                                        |  |  |  |  |