# TSV05 TAPE TRANSPORT SUBSYSTEM Installation Update Information

Order Number EK-TSV05-UP.A01

#### 1st Edition, April 1991

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license.

No responsibility is assumed for the use or reliability of software on equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Restricted Rights: Use, duplication, or disclosure by the U. S. Government is subject to restrictions as set forth in subparagraph (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

Copyright © Digital Equipment Corporation 1991

All Rights Reserved. Printed in U.S.A.

The postpaid Reader's Comment Card included in this document requests the user's critical evaluation to assist in preparing future documentation.

FCC NOTICE: The equipment described in this manual generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. Operation of this equipment in a residential area may cause interference, in which case the user at his own expense may be required to take measures to correct the interference.

The following are trademarks of Digital Equipment Corporation: TS05, and the DIGITAL logo.

This document was prepared and published by Educational Services Development and Publishing, Digital Equipment Corporation.

# **Contents**

| Ab                       | out T                                       | This Manual                                            | v    |  |  |  |

|--------------------------|---------------------------------------------|--------------------------------------------------------|------|--|--|--|

| Structure Of The Manual  |                                             |                                                        |      |  |  |  |

| No                       | tes, (                                      | Cautions, And Warnings                                 | vii  |  |  |  |

| Re                       | lated                                       | Documentation                                          | viii |  |  |  |

| 1 INSTALLING THE TSV05-S |                                             |                                                        |      |  |  |  |

|                          | 1.1                                         | Overview                                               | 1–1  |  |  |  |

|                          | 1.2                                         | Unpacking And Inspection (TSV05-S Models)              | 1–1  |  |  |  |

|                          | 1.3                                         | Tools And Working Space                                | 1–2  |  |  |  |

|                          | 1.4                                         | Removing The TS05 Tape Transport From The Carton       | 1-2  |  |  |  |

|                          | 1.5                                         | Removing The Cabinet From The Skid                     | 1–5  |  |  |  |

|                          | 1.6 Unpacking The TSV05-Sx Installation Kit |                                                        |      |  |  |  |

|                          | 1.7                                         | Unpacking The Cable Kit (CK-TS05-15 or CK-TS05-16)     | 1-10 |  |  |  |

|                          | 1.8                                         | Unpacking The Other Small Cartons                      | 1-10 |  |  |  |

| 2                        | INS                                         | STALLING THE TSV05-A/B/Z                               |      |  |  |  |

|                          | 2.1                                         | Unpacking And Inspection (TSV05-A/B/Z Models)          | 2-1  |  |  |  |

|                          | 2.2                                         | Tools And Working Space                                | 2-1  |  |  |  |

|                          | 2.3                                         | Unpacking The Cabinet                                  | 2-1  |  |  |  |

|                          | 2.4                                         | Deskidding The Cabinet                                 | 2-5  |  |  |  |

|                          | 2.5                                         | Unpacking TSV05-A, TSV05-B or TSV05-Z Installation Kit | 2-7  |  |  |  |

|                          | 2.6                                         | Unpacking The Cable Kits                               | 2-12 |  |  |  |

|                          | 2.7                                         | Unpacking The Smaller Cartons                          | 2-13 |  |  |  |

| Figures |                                                |      |

|---------|------------------------------------------------|------|

| 1-1     | Cabinet Carton Remoral                         | 1–3  |

| 1-2     | Unpacking Sequence                             | 1–4  |

| 1-3     | Raising Leveling Feet                          | 1–5  |

| 1-4     | Deskidding The Cabinet                         | 1–6  |

| 1-5     | Opening Cabinet Door                           | 1-7  |

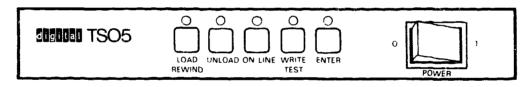

| 16      | M7530-PA Module                                | 1~9  |

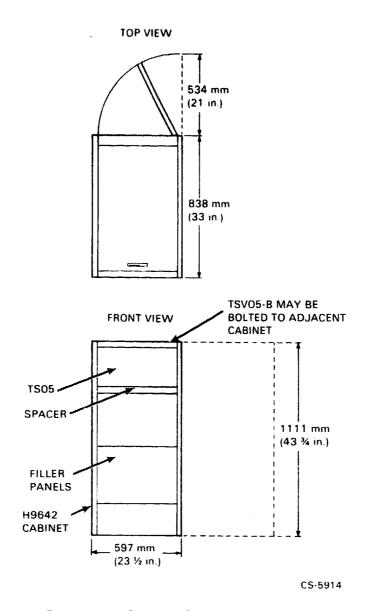

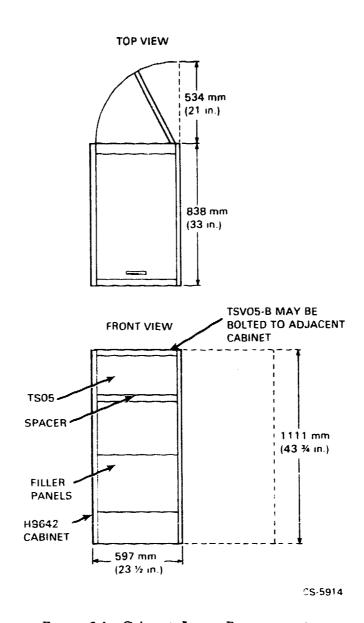

| 2–1     | Cabinet Carton Removal                         | 2–3  |

| 2-2     | Unpacking Sequence                             | 2-4  |

| 2–3     | Raising Leveling Feet                          | 2–5  |

| 2-4     | Deskidding The Cabinet                         | 2~6  |

| 2–5     | Opening Cabinet Door                           | 2–7  |

| 2–6     | M7196 Switch And Jumper Identification         | 2-9  |

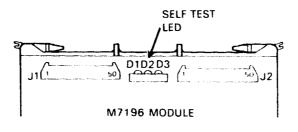

| 2–7     | M7196 Module                                   | 2-10 |

| 2–8     | Transport Switch And Terminator Identification | 2–11 |

| Tables  |                                                |      |

| 1       | Notes, Cautions, & Warnings                    | vii  |

| 1-1     | CK Kits                                        | 1-10 |

| 1–2     | Parts List Breakdown                           | 1-10 |

| 2-1     | CK Kits                                        | 2-12 |

| 2–2     | Parts List Breakdown                           | 2-12 |

|         |                                                |      |

# **About This Manual**

The information in this manual is directed toward the DIGITAL Customer Services Engineer and is intended to address the installers need for information on the TSV05 Tape Drive. The unpacking instructions in this manual supersede previous unpacking instructions after the implimentation of Engineering Change Orders H9542-F-MK111 and TS05-B-MK108.)

# Structure Of The Manual

Chapter 1 provides information on the unpacking and inspection procedures for the TSV05-S cabinet models (-SE). The unpacking procedures for the TSV05-Sx rack-mount kit and cable kit applies equally to the TSV05 rack models (-SA).

Chapter 2 provides information on the unpacking and inspection procedures for the TSV05-A, TSV05-B, and the TSV05-Z variations.

# **Notes, Cautions, And Warnings**

The following conventions are observed in this manual:

#### Table 1 Notes, Cautions, & Warnings

| NOTE    | Highlights important information or explanations.                                            |

|---------|----------------------------------------------------------------------------------------------|

| CAUTION | Highlights areas that could cause damage to the equipment or corrupt the data on the system. |

| WARNING | Calls attention to areas that could injure personnel.                                        |

# **Related Documentation**

- 1. TSV05 Tape Transport Installation Manual (EK-TSV05-IN).

- 2. TSV05 Tape Subsystem Installation/Owner's Manual (EK-TSV05-IO).

- 3. TSV05 Tape Transport Subsystem User's Guide (EK-TSV05-UG).

- 4. TSV05 Pocket Service Guide (EK-TSV05-PS).

- 5. TSVJ5 Tape Transport Subsystem Technical Manual (EK-TSV05-TM).

#### **INSTALLING THE TSV05-S**

#### 1.1 Overview

This document has been written to define the new packaging which will be implemented after the following Engineering Change Orders (ECO's) have been processed:

- H9542-F-MK111

- TS05-B-MK108

The unpacking instructions in this manual supersede the unpacking instructions defined in Chapters 2 and 3 of the TSV05 Tape Transport Subsystem Technical Manual (EK-TSV05-TM) and Chapter 2 of the TSV05 Tape Subsystem Installation/Owner's Manual (EK-TSV05-IO).

#### 1.2 Unpacking And Inspection (TSV05-S Models)

The unpacking instructions defined in this section supersede the unpacking instructions defined in Section 2.2 of TSV05 Tape Transport Subsystem Technical Manual (EK-TSV05-TM) and Chapter 2 of the TSV05 Tape Subsystem Installation/Owner's Manual (EK-TSV05-IO).

The following paragraphs describe the unpacking and inspection procedures for the TSV05-S cabinet models (-SE). The unpacking procedures for the TSV05-Sx rack-mount kit and cable kit applies equally to the TSV05 rack models (-SA).

#### CAUTION

The TSV05-Sx installation kit contains a module subject to electrostatic discharge (ESD). Put on ESD protective equipment prior to unpacking the installation kit. Failure to do so can result in equipment damage.

Only qualified service personnel should remove or install modules.

The TSV05-SE cabinet models are shipped as one skid-mounted carton and one or more smaller cartons. The carton on the skid contains the TS05 tape transport cabinet. The smaller carton(s) contains the TSV05-Sx installation kit (M7530-PA), one of two cable kits [CK-TS05-15 (eight foot cables) or CK-TS05-16 (16 foot cables)], and a soft box kit containing documentation, a cleaning kit and a reel of magnetic tape. These smaller items may be shipped in one carton or two, depending on shipping requirements.

Check the shipping documents to ensure that the correct model has been shipped. If anything is missing, damaged, or incorrect, contact the dealer from whom the equipment was ordered.

#### 1.3 Tools And Working Space

The following tools are required:

- 1. Scissors

- 2. 3/8 inch wrench

- 3. 11/16 inch wrench

- 4. 3/4 inch wrench

- 5. 5/32 inch hex key

- 6. Anti-static kit (p/n 29-26246-00)

Also, a space of approximately 3 meters (10 feet) square is required for moving the cabinet off of the shipping skid.

#### 1.4 Removing The TS05 Tape Transport From The Carton

Use the following procedure to remove the TS05 Tape Transport from its carton.

#### **WARNING**

Once the leveling feet are raised, the cabinet is free to roll on its casters. The cabinet is top-heavy and must be handled with care.

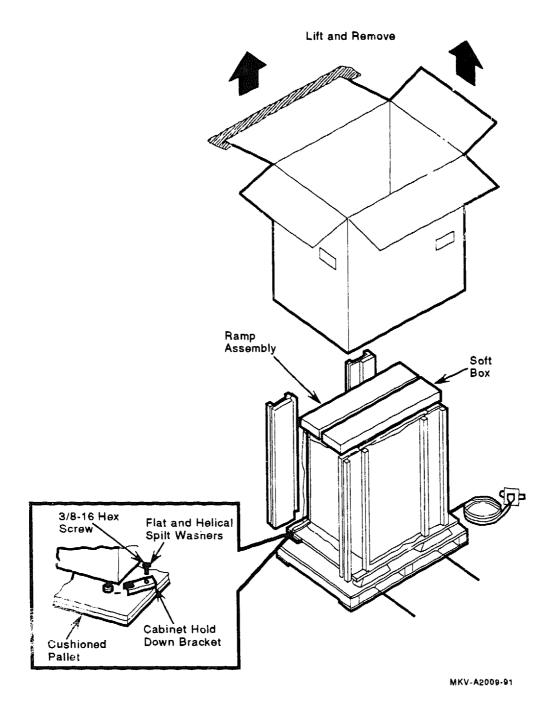

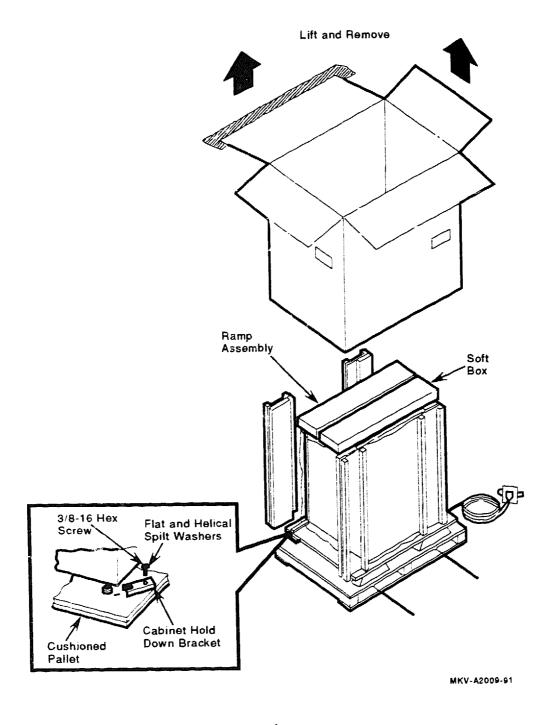

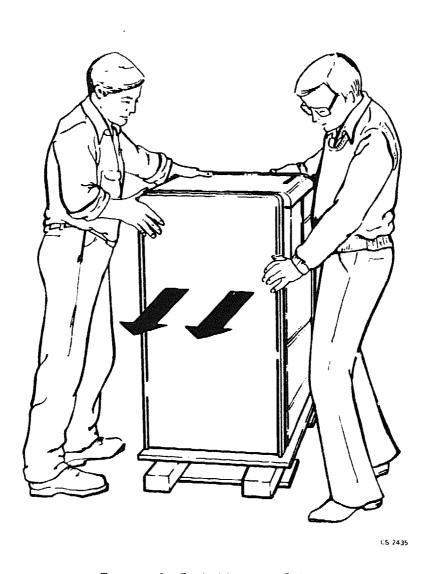

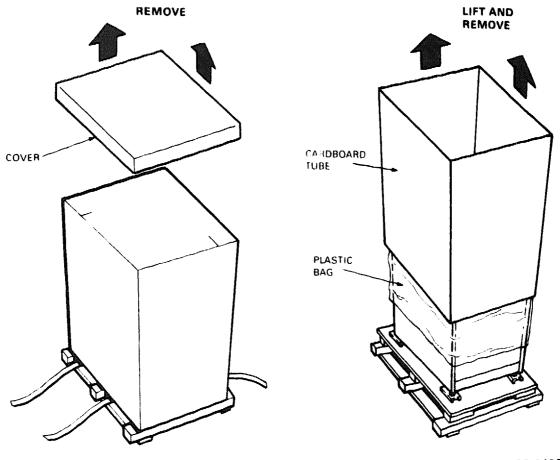

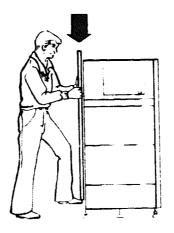

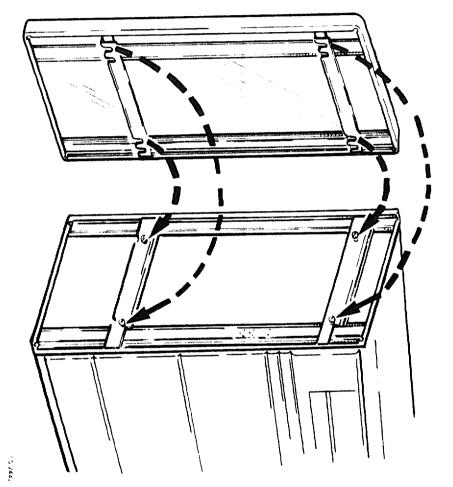

- 1. Use scissors to cut the nylon straps and remove the cardboard box (Figure 1-1). Remove the plastic bag.

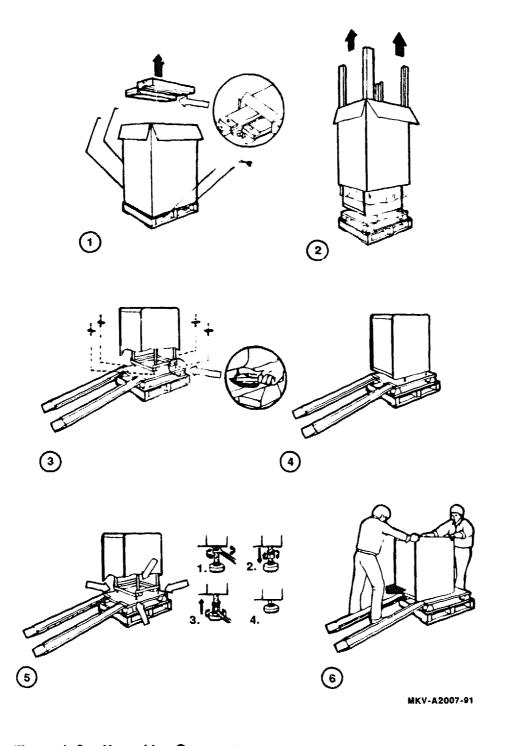

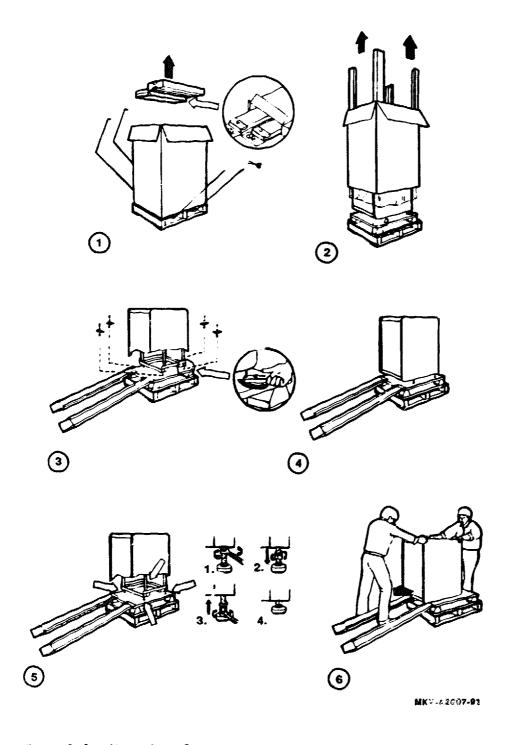

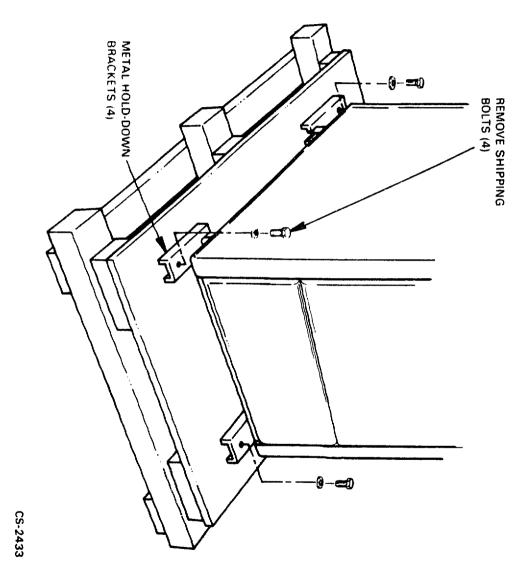

- 2. Using a 3/8 inch wrench, remove the four shipping bolts that hold the cabinet to the skid. Figure 1-2 shows the sequence in which to unpack the unit.

- 3. Remove the metal hold-down brackets.

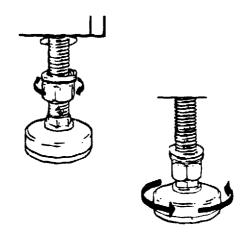

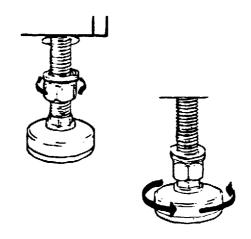

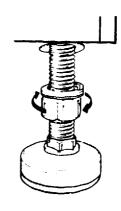

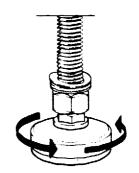

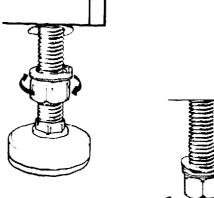

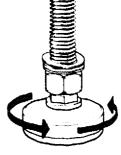

- 4. Using a 11/16 inch wrench, loosen the leveling feet looking nuts (Figure 1-3).

- 5. Using a 3/8 inch wrench, screw the leveling feet up into the cabinet base all the way.

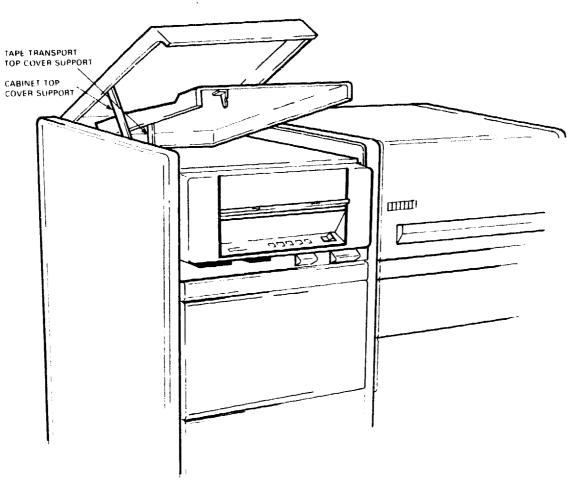

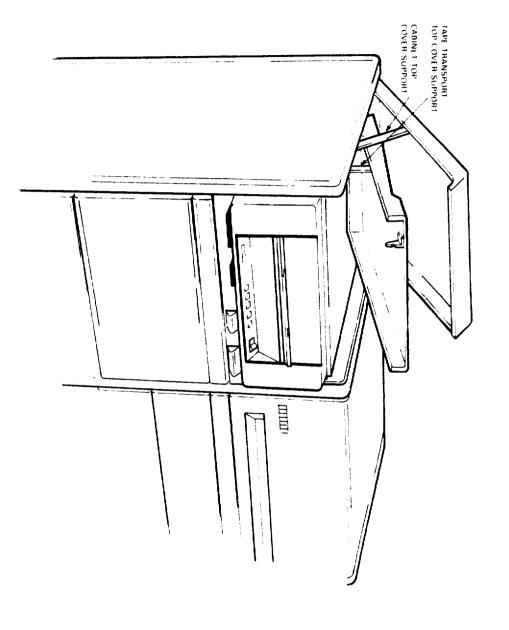

Figure 1-1 Cabinet Carton Removal

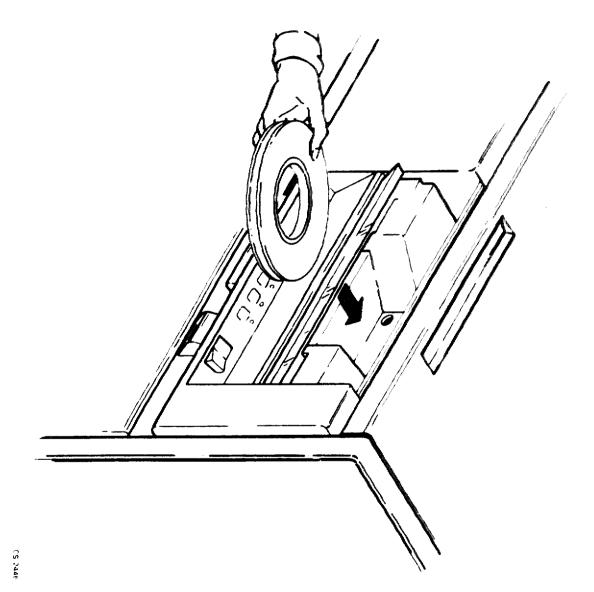

Figure 1–2 Unpacking Sequence

- 1. Turn Nut Down to Bottom.

- 2. Screw Foot into Cabinet Far Enough to Permit Cabinet to be Rolled on its Casters.

MKV-A2000-91

Figure 1-3 Raising Leveling Feet

#### 1.5 Removing The Cabinet From The Skid

Use the following procedure to remove the cabinet from the skid.

#### **WARNING**

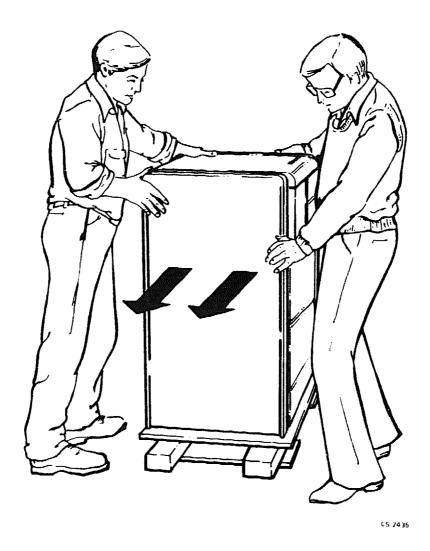

Use sufficient manpower to move the cabinet off of the skid.

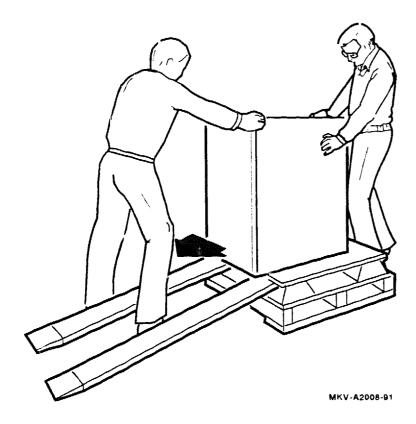

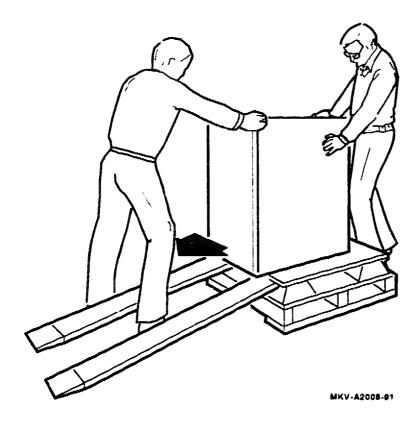

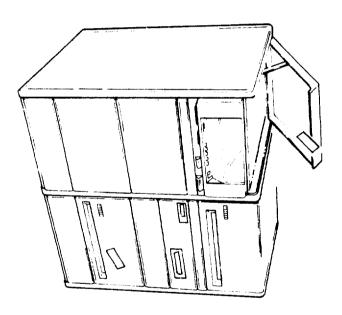

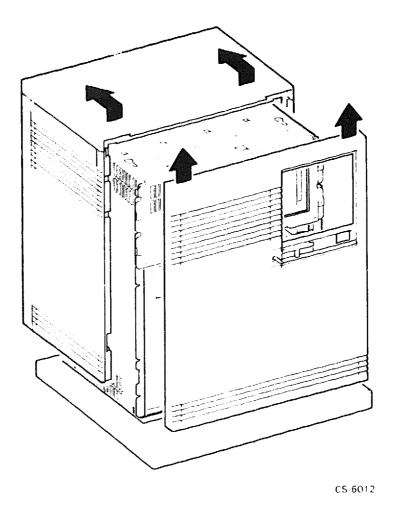

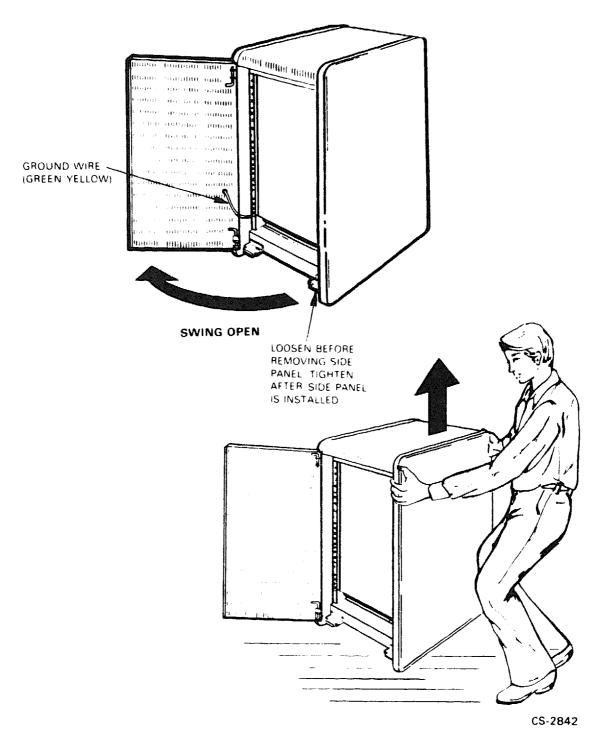

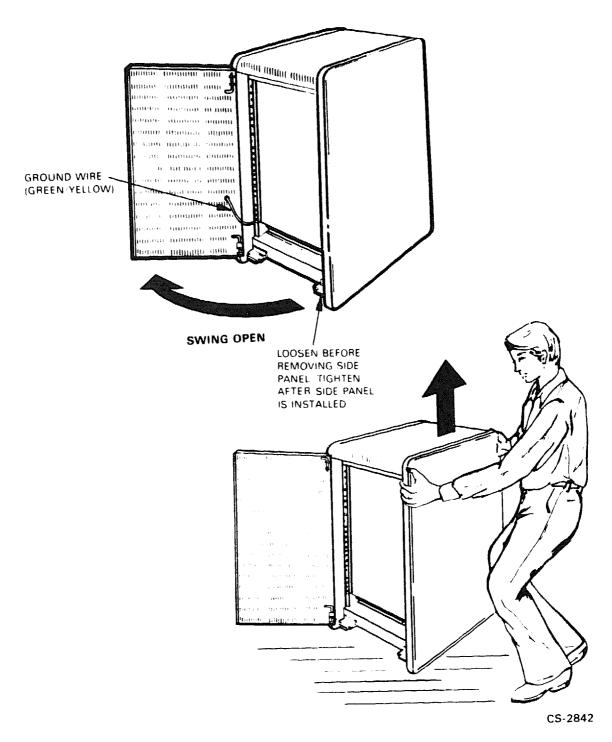

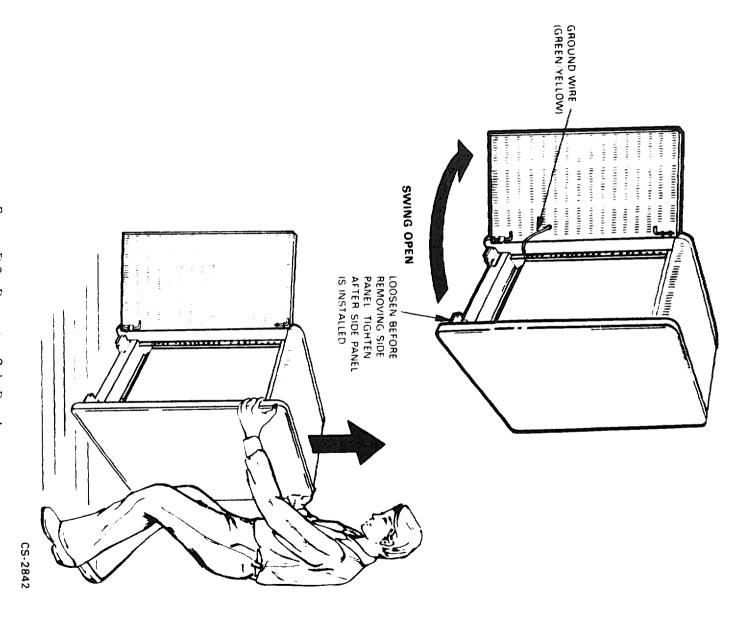

- 1. Grasp cabinet by the right top and the left top (Figure 1-4).

- 2. Install both ramps onto the pallet deck.

- 3. Roll the cabinet off of the skid and down ramps, taking care to prevent it from toppling over.

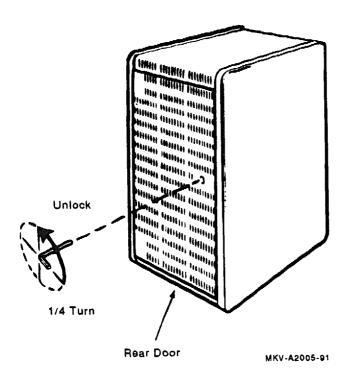

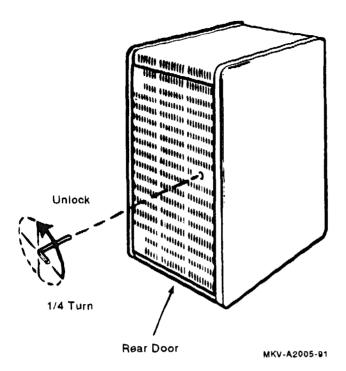

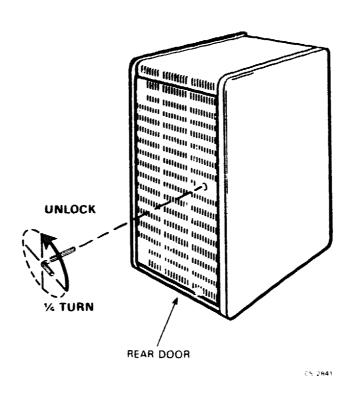

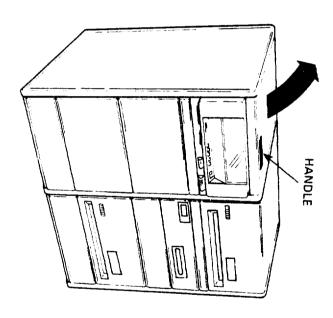

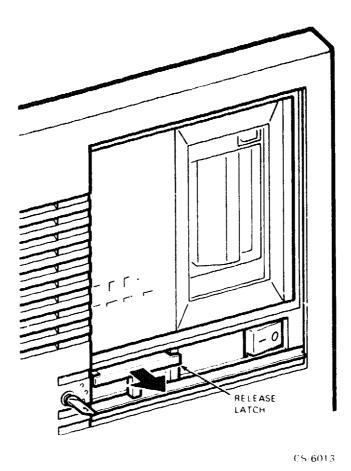

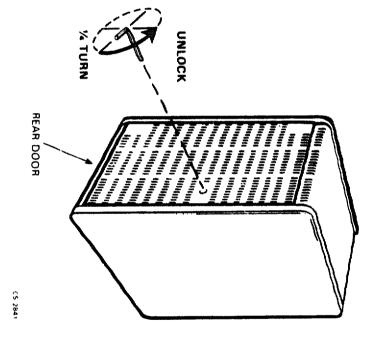

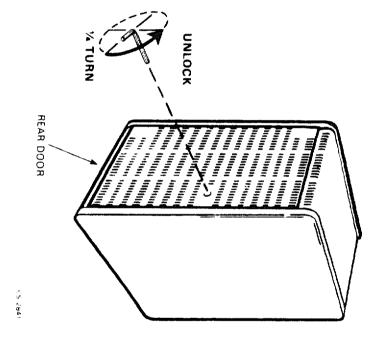

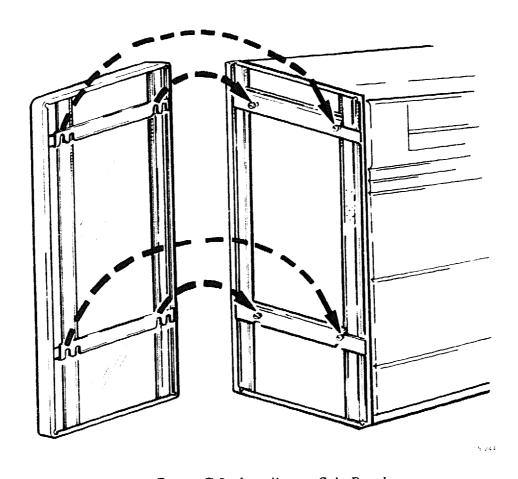

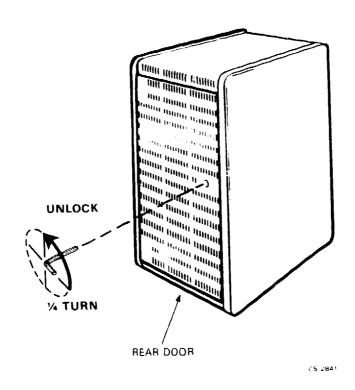

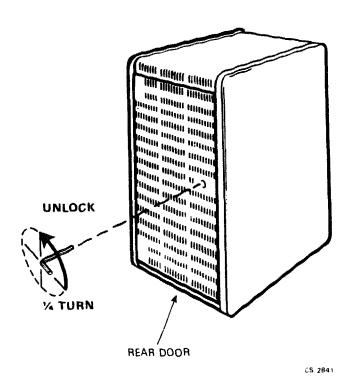

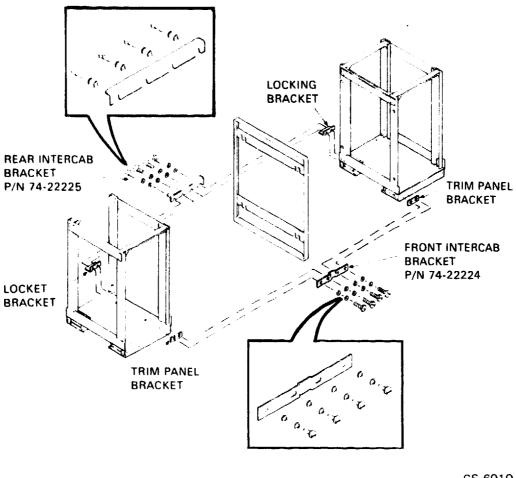

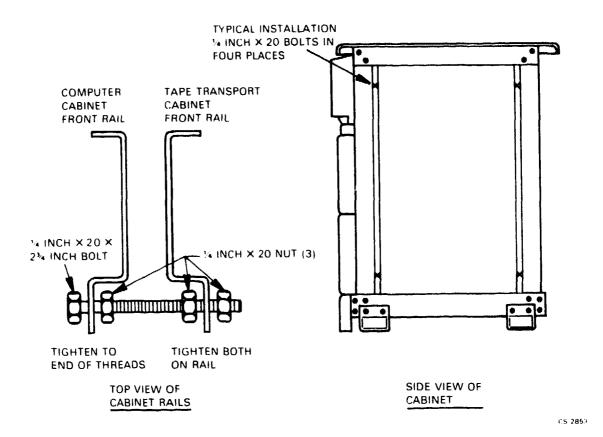

- 4. Open the rear door using a 5/32 inch hex key (Figure 1-5) and verify that the envelope taped to the bottom of the cabinet contains:

- a. Remote Cable (p/n 70-08288-8F)

- b. Intercabinet Hardware (p/n 74-22224/74-22225)

- c. Four 1/4-20 x 2.75 inch bolts

- d. Twelve 1/4-20 self-retaining nuts

Figure 1-4 Deskidding The Cabinet

Figure 1-5 Opening Cabinet Door

# 1.6 Unpacking The TSV05-Sx Installation Kit

#### CAUTION

The TSV05-Sx installation kit contains a module subject to electrostatic discharge (ESD). Put on ESD protective equipment (see note 1) prior to unpacking the installation kit. Failure to do so can result in equipment damage.

#### NOTE

Do not dispose of the packing material until the module has been successfully installed and is operational.

- 1. Before opening the shipping container, look for external damage to the shipping container such as dents, holes, or crushed corners.

- 2. Put on your anti-static wrist strap.

- 3. Ground the wrist strap and the anti-static mat to a local ground. Use the anti-static mat for placement of the module.

- 4. Open the shipping container.

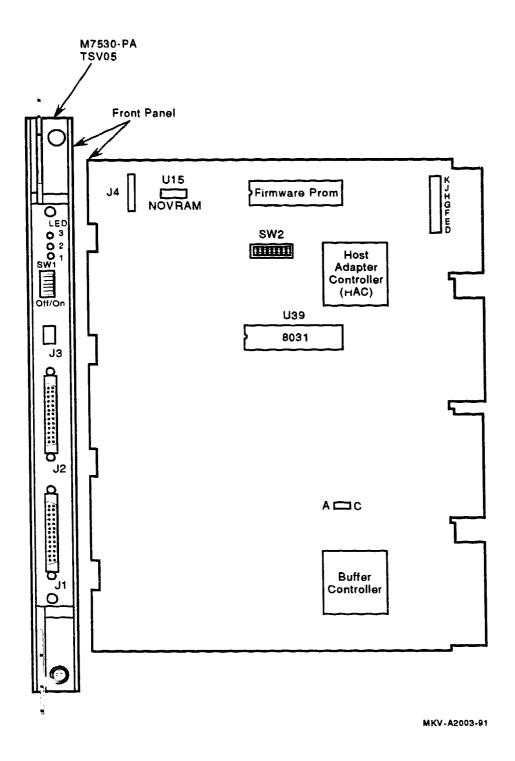

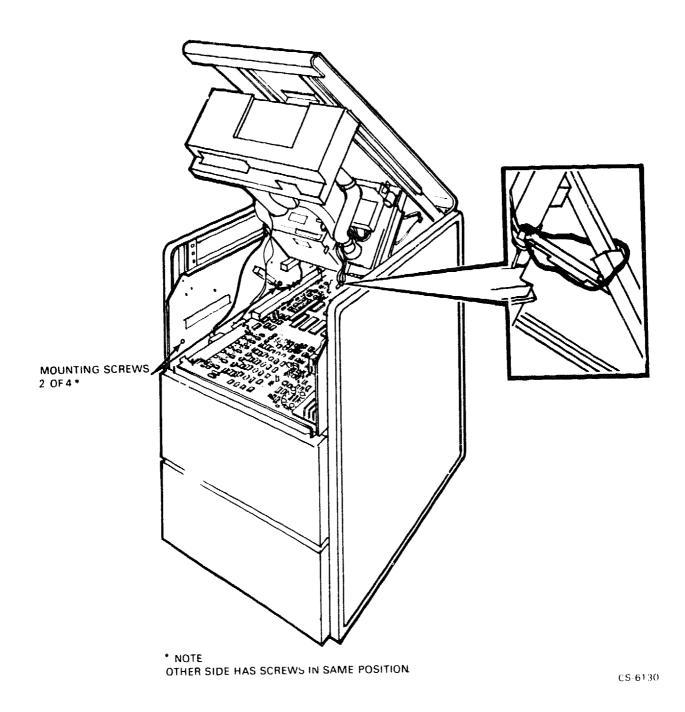

- 5. Remove the M7530 module from the anti-static bag.

- 6. Inspect the module for shipping damage. Check carefully for cracks, breaks, and loose components. Ensure that all PROMs are fully seated in their sockets.

- 7. Report any damage to the shipper and notify the DIGITAL representative.

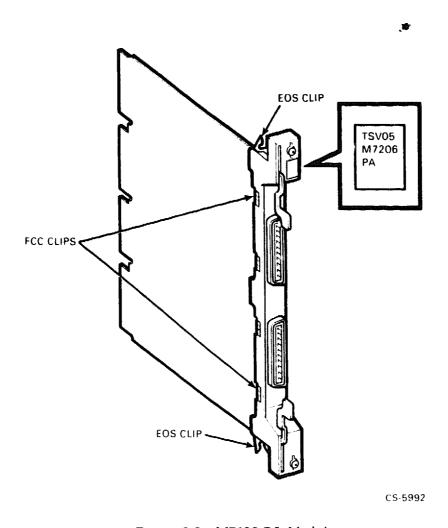

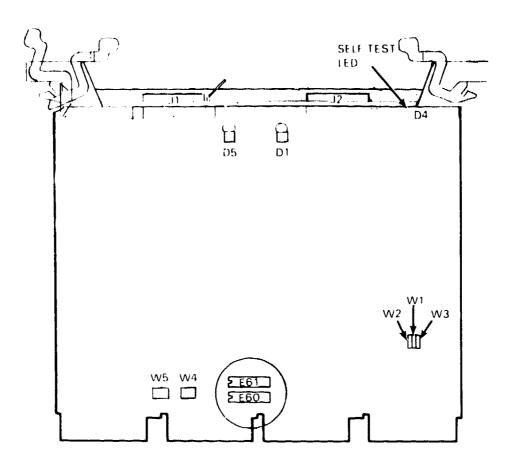

- 8. Ensure that there is no residue or corrosion on the handle EOS and FCC clips (Figure 1-6). If so, remove it with alcohol or other approved mild cleaners.

- 9. Ensure that there is no residue or corrosion on the gap filler assemblies. If so, remove it with alcohol or other approved mild cleaners.

- 10. Ensure that the EOS and FCC clips on the handle are in an arch shape. When pressing slightly, they should return to their original shape.

- 11. If any clip is missing, broken, distorted, or corroded, replace it with EOS clip p/n 12-26922-01, or FCC clip p/n 12-23640-01.

- 12. Either install the controller at this time or return it to the anti-static bag it was originally packaged in (until it is ready to be installed).

Note that the Anti-static Kit (29-26246-00) is not included, but is part of the Field Service Tool Kit.

Figure 1-6 M7530-PA Module

# 1.7 Unpacking The Cable Kit (CK-TS05-15 or CK-TS05-16)

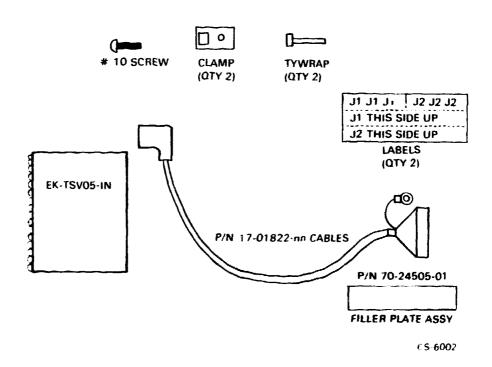

Open the shipping container and check its contents. Reference Table 1-1 and locate the configuration that was ordered. Locate the parts described for that configuration in the Parts List Breakdown (Table 1-2). Table 1-2 contains a list of the contents of the cable kits.

Table 1-1 CK Kits

| Configuration | Configuration Description          |

|---------------|------------------------------------|

| CK-TS05-15    | TS05-Sx Cable Kit (8 foot cables)  |

| CK-TS05-16    | TS05-Sx Cable Kit (16 foot cables) |

Table 1-2 Parts List Breakdown

| Item | Part Number | Description          | 15 | 16 |  |

|------|-------------|----------------------|----|----|--|

| 1    | 17-02487-01 | 50-Pin Cable, 8 ft.  | 2  | •  |  |

| 2    | 17-02487-02 | 50-Pin Cable, 16 ft. | •  | 2  |  |

| 3    | 70-24505-01 | Bulkhead Panel       | 1  | 1  |  |

| 4    | 90-00063-39 | Screw, #10           | 1  | 1  |  |

| 5    | 90-07032-00 | Cable Tie            | 2  | 2  |  |

| 6    | 90-07867-00 | Mount, Cable Tie     | 2  | 2  |  |

#### 1.8 Unpacking The Other Small Cartons

Open the other soft box kit (p/n 70-27321-00) and check its contents. The kit should contain the following:

- 1. TSV05 Installation/Owner's Manual (EK-TSV05-IO)

- 2. TSV05 Installation Addendum (EK-TSV05-UP)

- 3. TSV05 Pocket Service Guide (EK-TSV05-PG)

- 4. Tape Cleaning Kit

- 5. Magnetic Tape (2400 feet, blank)

If any item is damaged, missing, or incorrect, contact dealer from whom the system was purchased.

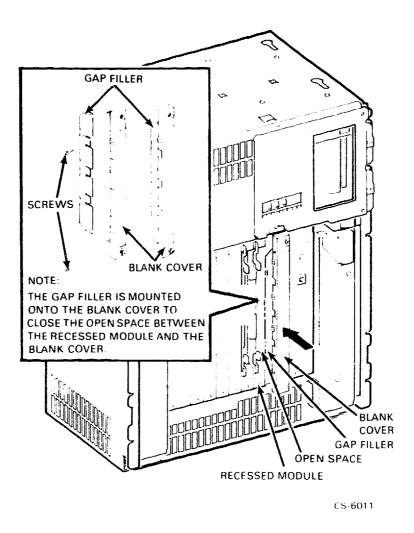

Note that the filler panel kit should include two gap filler assemblies and four 1/4 inch flat-head machine screws.

# **INSTALLING THE TSV05-A/B/Z**

# 2.1 Unpacking And Inspection (TSV05-A/B/Z Models)

The unpacking instructions defined in this section supersede the unpacking instructions defined in Section 3.2 of TSV05 Tape Transport Subsystem Technical Manual (EK-TSV05-TM).

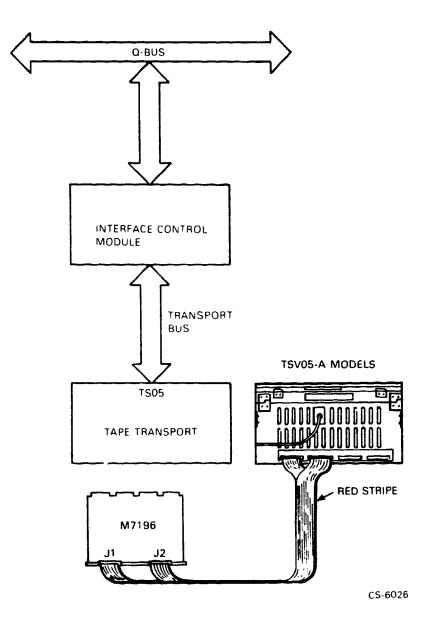

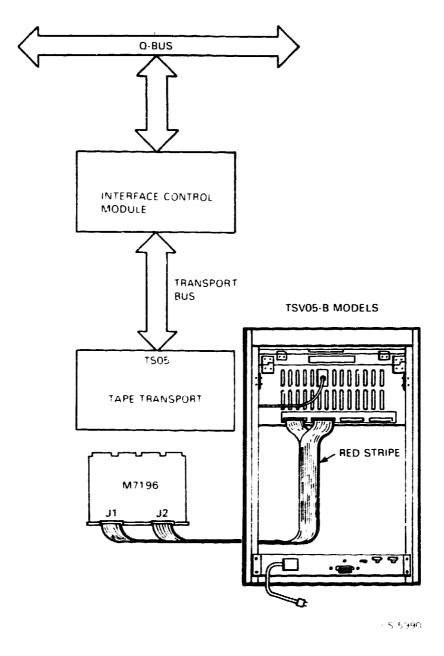

The TSV05-A and the TSV05-Z variations are shipped in one large carton and one (or more) small carton(s). The TSV05-B is shipped as one skid-mounted carton and one (or more) smaller carton(s). The carton on the skid contains the TS05 tape transport cabinet. The smaller carton(s) contains the M7196 interface/controller module, the documentation and accessories, and two individually packaged cables. These smaller items may be shipped in one carton or two, depending on shipping requirements. Check the shipping documents to ensure that the correct model has been shipped. If anything is missing, damaged, or incorrect, contact the dealer from whom the equipment was ordered.

# 2.2 Tools And Working Space

The following tools are required for unpacking the TSV05-B subsystem:

- 1. Scissors

- 2. 3/8 inch wrench

- 3. 11/16 inch wrench

- 4. 3/4 inch wrench

- 5. 5/32 inch hex key

- 6. Anti-static kit (p/n 29-26246-00)

Also, a space of approximately 3 meters (10 feet) square is required for moving the cabinet off of the shipping skid.

# 2.3 Unpacking The Cabinet

#### WARNING

Once the leveling feet are raised, the cabinet is free to roll on its casters. The cabinet is top-heavy and must be handled with care.

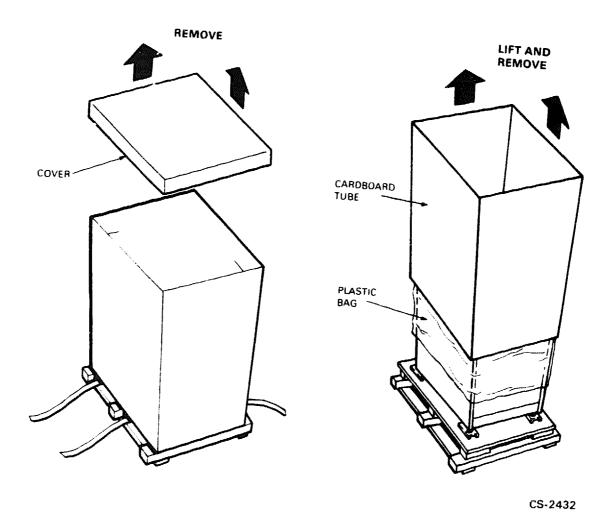

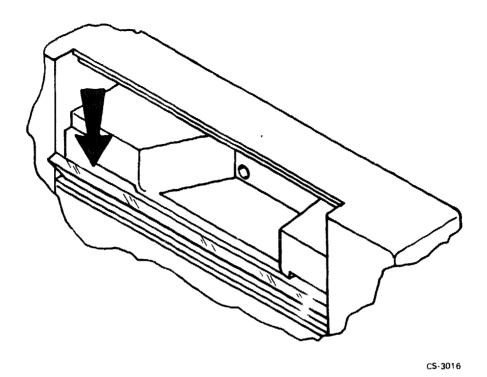

1. Use scissors to cut the nylon straps and remove the cardboard box (Figure 2-1). Remove the plastic bag.

#### 2-2 INSTALLING THE TSV05-A/B/Z

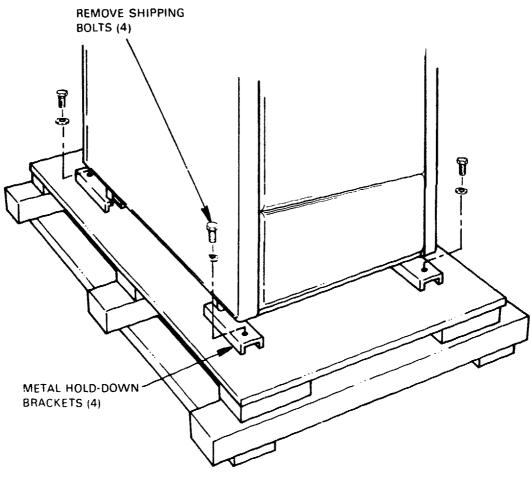

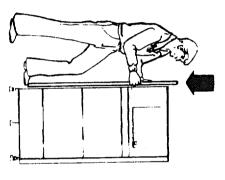

- 2. Using a 3/8 inch wrench, remove the four shipping bolts that hold the cabinet to the skid. Figure 2-2 shows the sequence in which to unpack the unit.

- 3. Remove the metal hold-down brackets.

- 4. Using a 11/16 inch wrench, loosen the leveling feet locking nuts (Figure 2-3).

- 5. Using a 3/8 inch wrench, screw the leveling feet up into the cabinet base all the way.

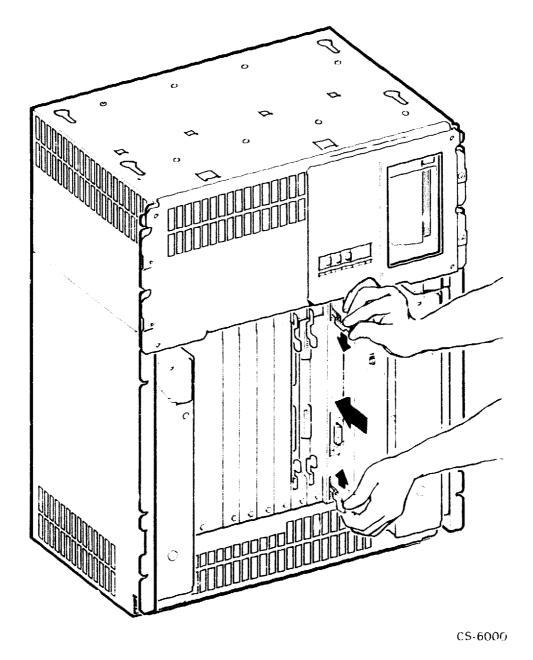

Figure 2-1 **Cabinet Carton Removal**

Figure 2-2 Unpacking Sequence

- 1. Turn Nut Down to Bottom

- 2 Screw Foot into Cabinet Far Enough to Permit Cabinet to be Rolled on its Casters

MKV-A2000-91

Figure 2–3 Raising Leveling Feet

#### 2.4 Deskidding The Cabinet

Use the following procedure to remove the cabinet from the skid.

#### WARNING

Use sufficient manpower to move the cabinet off of the skid.

- 1. Grasp cabinet by the right top and the left top (Figure 2-4).

- 2. Install both ramps onto the pallet deck.

- 3. Roll the cabinet off of the skid and down ramps, taking care to prevent it from toppling over

- 4. Open the rear door using a 5/32 inch hex key (Figure 2-5) and verify that the envelope taped to the bottom of the cabinet contains:

- a. Remote Cable (p/n 70-08288-8F)

- b. Intercabinet Hardware (p/n 74-22224/74-22225)

- c. Four 1/4-20 x 2.75 inch bolts

- d. Twelve 1/4-20 self-retaining nuts

Figure 2-4 Deskidding The Cabinet

Figure 2-5 **Opening Cabinet Door**

#### 2.5 Unpacking TSV05-A, TSV05-B or TSV05-Z Installation Kit

#### CAUTION

The TSV05 installation kit contains a module subject to electrostatic discharge (ESD). Put on ESD protective equipment (see note 1) prior to unpacking the installation kit. Failure to do so can result in equipment damage.

#### NOTE

Do not dispose of the packing material until the module has been successfully installed and is operational.

- Before opening the shipping container, look for external damage to the shipping container such as dents, holes, or crushed corners.

- 2. Put on your anti-static wrist strap.

- 3. Ground the wrist strap and the anti-static mat to a local ground. Use the anti-static mat for placement of the module.

- 4. Open the shipping container.

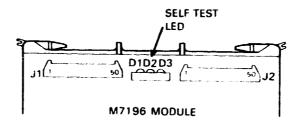

- 5. Remove the M7196 module from the anti-static bag.

- 6. Inspect the module for shipping damage. Check carefully for cracks, breaks, and loose components. Ensure that all PROMs are fully seated in their sockets.

- 7. Report any damage to the shipper and notify the DIGITAL representative.

- 8. Return the M7196 to its protective anti-static bag or proceed to install the controller in the host system.

Note that the anti-static kit (29-26246-00) is not included, but is part of the Field Service Tool Kit.

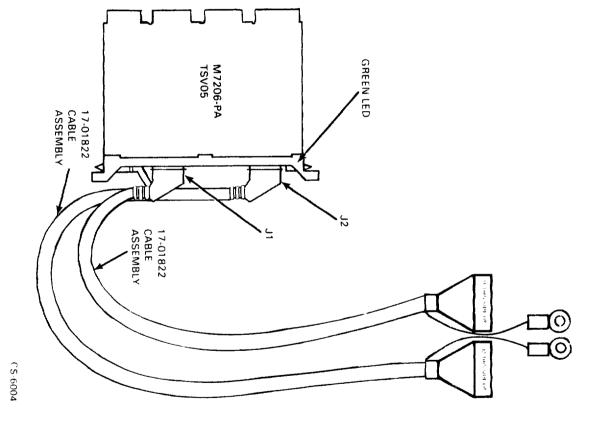

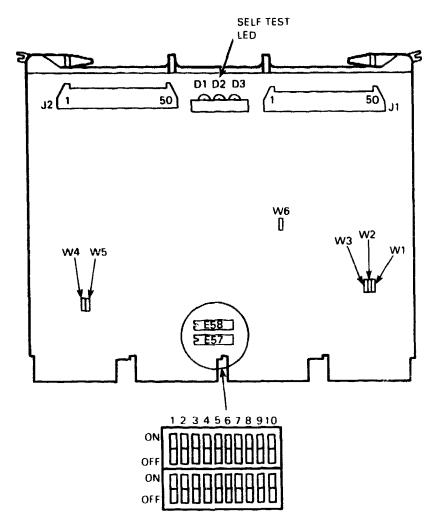

MKV-A2001-91

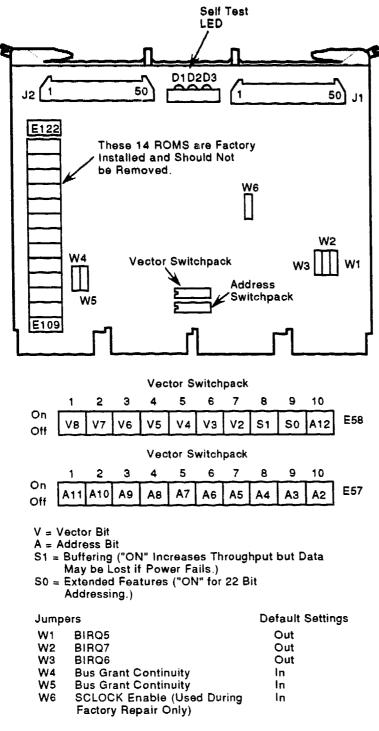

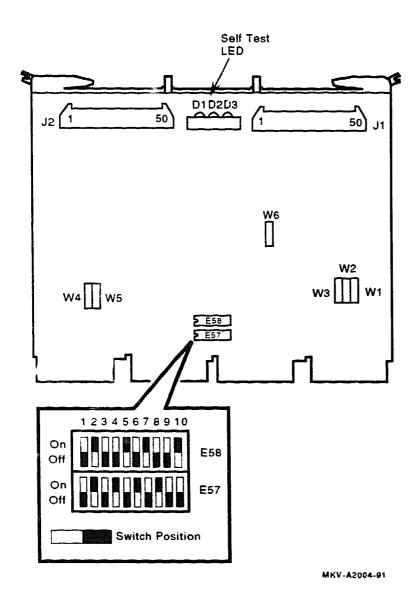

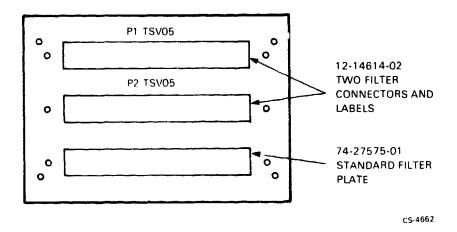

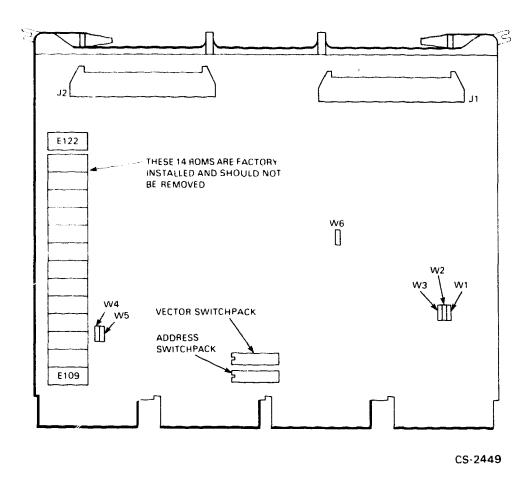

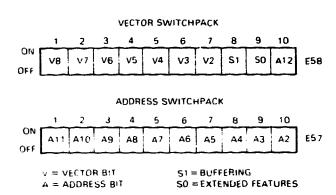

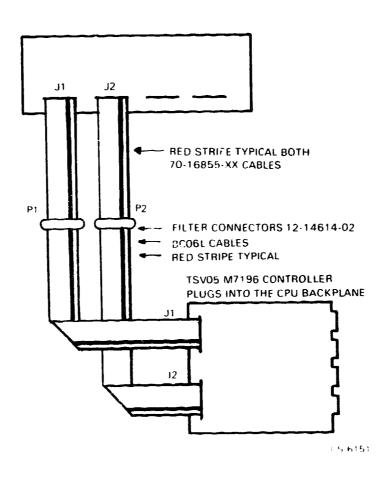

Figure 2-6 M7196 Switch And Jumper Identification

Figure 2-7 M7196 Module

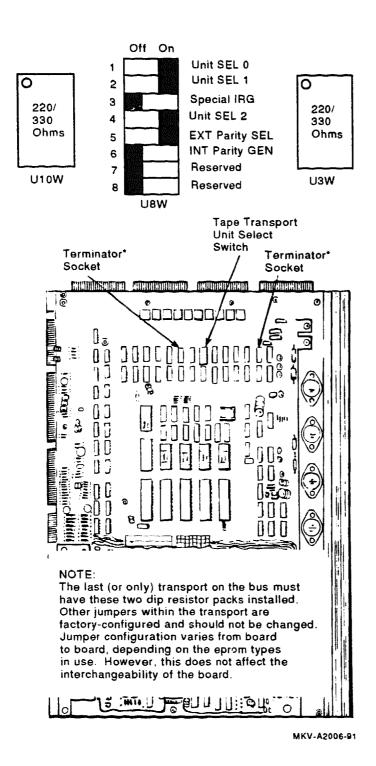

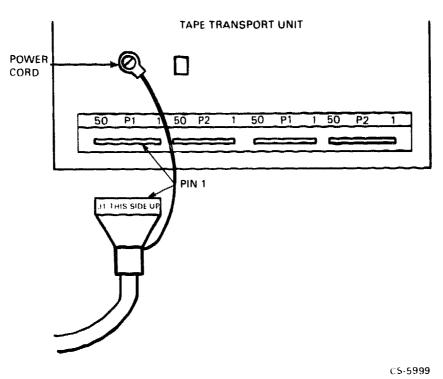

Figure 2-8 Transport Switch And Terminator Identification

#### 2.6 Unpacking The Cable Kits

Open the shipping container and check its contents. Reference Table 2-1 and locate the configuration that was ordered. Locate the parts described for that configuration in the Parts Lie. Breakdown (Table 2-2). Table 2-2 contains a list of the contents of the cable hits.

Trole 2-1 CK Kits

| Configuration Description                                           |

|---------------------------------------------------------------------|

| TS05-A/B Cable Kit for BA123A (World Box Enclosure)                 |

| TS05-A/B Cable Kit for OEM                                          |

| TS05-A/B Cable Kit for H9642 Deep Cabinet (H3490 I/O)               |

| TS05-A/B Cable Kit for BA23A (Pedestal Enclosure and TSV05 Cabinet) |

| -                                                                   |

Table 2-2 Parts List Breakdown

| Item | Part<br>Number | Description        | 11 | 12 | 13 | 14 |

|------|----------------|--------------------|----|----|----|----|

| 1    | 12-14614-02    | Filter Con. 50 Pin | 2  | •  | 2  | 2  |

| 2    | BC06L-1C       | Cable, 1 ft. 3 in. | -  | -  | •  | 2  |

| 3    | BC06L-03       | Cable, 36 in.      | 2  | -  | 2  | -  |

| 4    | 70-16855-12    | Cable, 12 ft.      | 2  | -  | -  | 2  |

| 5    | 70-16855-06    | Cable, 6 ft.       | •  | -  | 2  | -  |

| 6    | 36-25190-01    | Label, I.D.        | 1  | -  | 1  | 1  |

| 7    | 74-27575-01    | Plate, Cover       | •  | -  | -  | 1  |

| 8    | 70-16855-16    | Cable, 16 in.      | -  | 2  | -  | 2  |

# 2.7 Unpacking The Smaller Cartons

Open the other soft box kit (p/n 70-22428-01) and check its contents. It should contain the following:

- 1. TSV05 Installation Manual (EK-TSV05-IN).

- 2. TSV05 User's Guide (EK-TSV05-UG).

- 3. TSV05 Pocket Service Guide (EK-TSV05-PS).

- 4. Magnetic Tape (2400 feet, blank)

- 5. Tape Cleaning Kit

- 6. TSV05 Installation Update Information (EK-TSV05-UP)

Inspect each item. If any item is damaged, missing, or incorrect, contact dealer from whom the system was purchased.

# Tape Transport Subsystem

Technical Manual

# Object Digital Equipment Corporation 1987 All Rights Reserved

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

#### Printed in U.S.A.

This document was produced using the DIGITAL DECpage text processing product. Book production was done by Computer Special Systems Documentation Services in Nashua, NH.

The following are trademarks of Digital Equipment Corporation:

| digitaJ™     | DECwriter    | RSX            |  |  |

|--------------|--------------|----------------|--|--|

| n 8 1 37     | DIBOL        | Scholar        |  |  |

| DEC          | MASSBUS      | ULTRIX         |  |  |

| DEC mate     | PDP          | UNIBUS         |  |  |

| DECset       | P/OS         | VAX            |  |  |

| DECsystem-10 | Professional | VMS            |  |  |

| DECSYSTEM-20 | Rainbow      | VT             |  |  |

| DECUS        | RSTS         | Work Processor |  |  |

# **CONTENTS**

|                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                          | Page                                                                |

|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| PREFACE                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                     |

| CHAPTER                                                                                                                       | 1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                           |                                                                     |

| 1.1<br>1.1.1<br>1.1.2<br>1.2<br>1.3<br>1.4<br>1.4.1                                                                           | DESCRIPTION TSV05 Models Features and Capabilities FUNCTIONAL OVERVIEW CONTROLS AND INDICATORS RELATED DOCUMENTS Customer Ordering DIGITAL Field Service Ordering                                                                                                                                                                                                                                        | . 1-1<br>. 1-2<br>1-9<br>. 1-10<br>. 1-12                           |

| CHAPTER                                                                                                                       | 2 TSV05-S INSTALLATION                                                                                                                                                                                                                                                                                                                                                                                   |                                                                     |

| 2.1<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6<br>2.3<br>2.3.1 | SITE PREPARATION  Space Accessibility Power Receptacles Cooling Air Purity  UNPACKING AND INSPECTION Tools and Working Space Removing the TS05 Tape Transport from the Carton Removing the Cabinet from the Skid Unpacking the TSV05-Sx Installation Kit Unpacking the Cable Kit (CK-TS05-15 or CK-TS05-16) Unpacking the Other Small Cartons TAPE TRANSPORT CABINET INSTALLATION Installing the Cabinet | 2-2-2-4<br>2-4<br>2-4<br>2-5<br>2-5<br>2-10<br>2-15<br>2-15<br>2-17 |

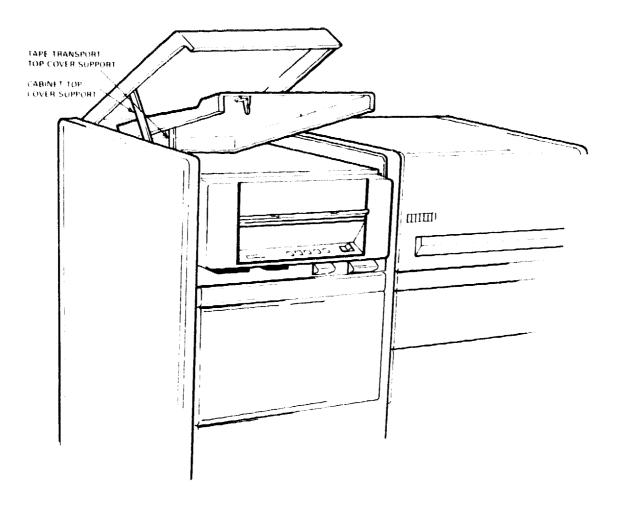

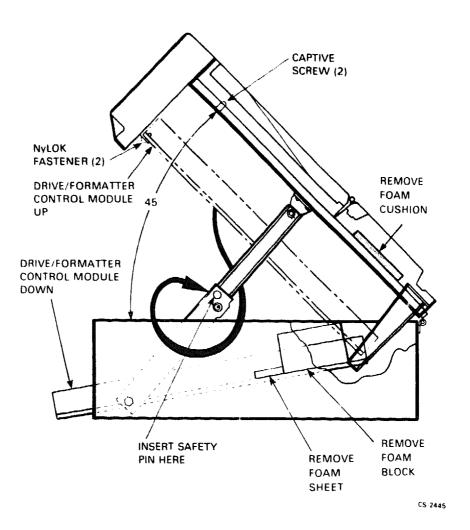

| 2.3.2<br>2.3.2.1<br>2.3.2.2                                                                                                   | Removing the Shipping Foam                                                                                                                                                                                                                                                                                                                                                                               | . 2-17                                                              |

|              |                                                | Page               |

|--------------|------------------------------------------------|--------------------|

| 2.3.3        | Connecting Line Power                          | 2-22               |

| 2.4          | TAPE TRANSPORT CHECKOUT                        |                    |

| 2.4.1        | Power-Up Test                                  |                    |

| 2.4.2        | Tape Loading Test                              |                    |

| 2.4.3        | Tape Movement Test                             |                    |

| 2.4.4        | Tape Unloading Test                            | 2-28               |

| 2.5          | BUS INTERFACE/CONTROLLER MODULE PREPARATION    | 2-29               |

| 2.5.1        | Checking the Configuration                     | 2-29               |

| 2.5.2        | Placing the Module                             | 2-32               |

| 2.5.2.1      | Bus Continuity                                 | 2-32               |

| 2.5.2.2      | Power Supplies                                 | 2-32               |

| 2.5.3        | Finding CSR Addresses and Interrupt Vectors    | 2-34               |

| 2.5.3.1      | Micro/PDP-11 Systems                           | 2-34               |

| 2.5.3.2      | MicroVAX Systems                               | 2-34               |

| 2.5.4        | Configuring the TSV05                          | 2-36               |

| 2.6          | BUS INTERFACE/CONTROLLER MODULE INSTALLATION   |                    |

|              | (M7206)                                        |                    |

| 2.6.1        | Testing the System                             |                    |

| 2.6.2        | Removing the Front Cover                       |                    |

| 2.6.3        | Removing Modules                               |                    |

| 2.6.3.1      | Modules with Handles                           |                    |

| 2.6.3.2      | Modules with Blank Covers                      |                    |

| 2.6.4        | Verifying the Ground Connections               |                    |

| 2.6.5        | Installing the M7206 Module                    |                    |

| 2.7          | INTERCONNECTING CABLE INSTALLATION             |                    |

| 2.7.1        | Labeling the M7206 Module Cables               |                    |

| 2.7.2        | Routing and Connecting the M7206 Module Cables |                    |

| 2.8          | TSV05 SUBSYSTEM CHECKOUT                       | 2-53               |

| СНАРТЕ       | ER 3 TSV05-A/B INSTALLATION                    |                    |

| 2.1          | SITE PREPARATION                               | 2.2                |

| 3.1<br>3.1.1 | Space                                          |                    |

|              | Accessibility                                  |                    |

| 3.1.2        | Power Receptacles                              |                    |

| 3.1.3        |                                                |                    |

| 3.1.4        | Cooling                                        |                    |

| 3.1.5        | Air Purity                                     |                    |

| 3.2          | Tools and Working Space                        |                    |

| 3.2.1        |                                                |                    |

| 3.2.2        | Unpacking the Cabinet                          | ე-ე<br>ე.ი         |

| 3.2.3        | Deskidding the Cabinet                         |                    |

| 3.2.4        | Unpacking the TSV05 Installation Kit           |                    |

| 3.2.5        | Unpacking the Cable Kits                       | , , , 3-14<br>3 1c |

| 3.2.6        | Unpacking the Smaller Cartons                  | 3-15               |

|         |                                                            | Page   |

|---------|------------------------------------------------------------|--------|

| 3.3     | TAPE TRANSPORT CABINET INSTALLATION                        | . 3-16 |

| 3.3.1   | Installing the Cabinet                                     | 3-16   |

| 3.3.2   | Removing the Shipping Foam                                 |        |

| 3.3.2.1 | Removing the Top Foam Pieces                               | . 3-16 |

| 3.3.2.2 | Removing the Bottom Foam Pieces                            |        |

| 3.3.3   | Connecting Line Power                                      | 3-23   |

| 3.4     | TAPE TRANSPORT CHECKOUT                                    |        |

| 3.4.1   | Power-Up Test                                              | 3-24   |

| 3.4.2   | Tape Loading Test                                          | 3-25   |

| 3.4.3   | Tape Movement Test                                         |        |

| 3.4.4   | Tape Unloading Test                                        |        |

| 3.5     | INSTALLING THE CABLE KITS                                  |        |

| 3.5.1   | Installing the Cable Kit for the BA123A Enclosure          |        |

|         | (CK-TS05-11)                                               | 3-30   |

| 3.5.2   | Installing the TSV05-A Cable Kit for the H9642 Deep        |        |

|         | Cabinet (CK-TS05-13)                                       | 3-30   |

| 3.5.3   | Installing Cable Kit for the BA23A Enclosure (CK-TS05-14). |        |

| 3.5.3.1 | Installing the TSV05 Filter Connector (without DECnet).    |        |

| 3.5.3.2 | Installing the TSV05 Filter Connector (with DECnet)        |        |

| 3.6     | BUS INTERFACE/CONTROLLER MODULE INSTALLATION               |        |

|         | (M7196)                                                    | . 3-36 |

| 3.6.1   | General Information                                        |        |

| 3.6.2   | Installing the Controller (M7196) and Cables               | 3-38   |

| 3.6.3   | Connecting the Line Power Cord                             |        |

| 3.7     | CHECKING OUT THE TSV05 SUBSYSTEM                           | . 3-41 |

| CHAPTER | 4 TSV05 CHECKOUT (PDP-11 PROCESSOR)                        |        |

| 4.1     | GENERAL INFORMATION                                        | 4-1    |

| 4.2     | POWER-UP CHECKS                                            |        |

| 4.3     | DIAGNOSTIC TESTS                                           |        |

| 4.3.1   | System Setup                                               |        |

| 4.3.2   | Diagnostic Test Procedures                                 |        |

| 4.3.2.1 | TSV05 Logic Test                                           | 4-5    |

| 4.3.2.2 | Advanced Logic Test                                        | 4-6    |

| 4.3.2.3 | Tape Transport Test                                        |        |

| 4.3.2.4 | Advanced Tape Transport Test                               |        |

| 4.3.2.5 | Data Reliability Test                                      |        |

| 4.4     | ADDITIONAL TESTS                                           |        |

|         |                                                     | Page  |

|---------|-----------------------------------------------------|-------|

| CHAPTE  | R 5 TSV05 CHECKOUT (MicroVAX II PROCESSO            | OR)   |

| 5.1     | GENERAL INFORMATION                                 | 5-1   |

| 5.1.1   | Prerequisites                                       |       |

| 5.1.2   | Hardware Requirements                               |       |

| 5.1.3   | Software Requirements                               |       |

| 5.2     | POWER-UP CHECKS                                     |       |

| 5.3     | DIAGNOSTIC TEST                                     |       |

| 5.3.1   | Loading MicroVAX Maintenance Software               | . 5-3 |

| 5.3.2   | Running the MicroVAX Maintenance Software (Customer |       |

|         | Version)                                            | . 5-3 |

| 5.3.3   | Running the MicroVAX Maintenance Software (Software |       |

|         | Version)                                            | . 5-3 |

| CHAPTE  | R 6 OPERATION                                       |       |

| 6.1     | ROUTINE OPERATING PROCEDURES                        | 6-1   |

| 6.1.1   | Power-Up                                            | . 6-1 |

| 6.1.2   | Loading the Tape                                    | . 6-1 |

| 6.1.3   | Rewinding the Tape                                  | . 6-3 |

| 6.1.4   | Unloading the Tape                                  | . 6-4 |

| 6.1.5   | Restarting the Tape Transport                       |       |

| 6.1.5.1 | Power Failure                                       |       |

| 6.1.5.2 | Hard Errors                                         |       |

| СНАРТЕ  | R 7 MAINTENANCE                                     |       |

| 7.1     | OPERATOR TROUBLESHOOTING                            | 7-1   |

| 7.2     | CONFIDENCE CHECKS                                   | 7-2   |

| 7.3     | CUSTOMER CARE                                       |       |

| 7.3.1   | Care of Magnetic Tape                               |       |

| 7.3.2   | Preventive Maintenance                              |       |

| 7.3.2.1 | Magnetic Tape Transport Cleaning Kit                |       |

| 7.3.2.2 | Accessing the Tape Path Area                        |       |

| 7.3.2.3 | Cleaning the Tape Path and Related Parts            |       |

| 7.3.2.4 | Cleaning the Housing                                |       |

| CHAPTER          | 8 TSV05-S TECHNICAL DESCRIPTION                   |      |

|------------------|---------------------------------------------------|------|

|                  |                                                   |      |

| 8.1              | INTRODUCTION                                      |      |

| 8.1.1            | Scope                                             |      |

| 3.1.2            | Conventions                                       |      |

| 8.1.3            | Terminology                                       |      |

| 8.2              | GENERAL DESCRIPTION                               |      |

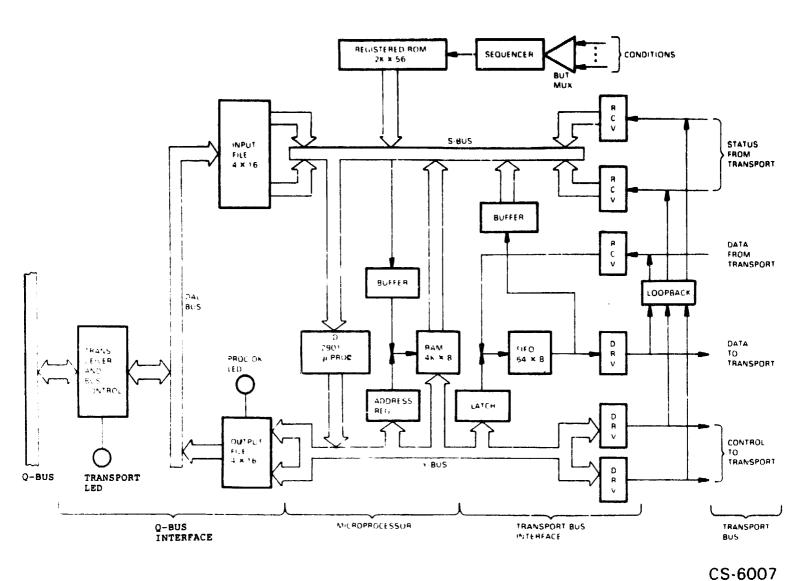

| 8.2.1            | M7206 Q-Bus Interface/Controller Module           |      |

| 8.2.1.1          | Q-Bus Interface                                   |      |

| 8.2.1.2          | Microprocessor                                    |      |

| 8.2.1.3          | Tape Transport Bus Interface                      |      |

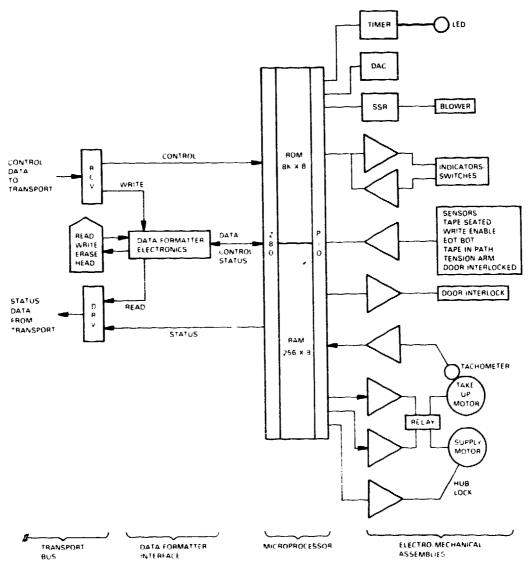

| 8.2.2            | TS05 Tape Transport Unit                          |      |

| 8.2.2.1          | Data Formatter Interface                          |      |

| 8.2.2.2          | Microprocessor                                    |      |

| 8.2.2.3<br>8.2.3 | Electromechanical Assemblies                      |      |

| 8.2.3<br>8.3     | FUNCTIONAL DESCRIPTION                            |      |

| 8.3.1            | M7206 Q-Bus Interface/Controller Module Operation |      |

| 8.3.1.1          | Q-Bus Interface (Sheets D1, D2, and D3)           |      |

| 8.3.1.2          | CSR and Data Memory (Sheet D6)                    |      |

| 8.3.1.3          | Tape Unit Interface (Sheet D7)                    |      |

| 8.3.1.4          | Program Sequencer and Tape Status In (Sheet D8)   |      |

| 8.3.1.5          | Arithmetic Logic Unit (Sheet 9)                   |      |

| 8.3.1.6          | Microprogram ROMs (Sheet D11)                     |      |

| 8.3.1.7          | Loopback Registers (Sheet D4)                     |      |

| 8.3.1.8          | Microprocessor Words                              |      |

| 8.3.1.9          | Microprocessor Chip Description                   |      |

| 8.3.2            | M7206/TS05 Interface                              |      |

| 8.3.2.1          | Interface to Tape Unit                            |      |

| 8.3.2.2          | Interface to Controller                           |      |

| 8.3.3            | TS05 Tape Transport Unit                          |      |

| 8.3.3.1          | Tape Transport Operation                          |      |

| 8.3.3.2          | Tape Transport Microprocessor                     |      |

| 8.4              | FIRMWARE DESCRIPTION                              |      |

| 8.4.1            | Diagnostic                                        |      |

| 8.4.1.1          | Power-Up                                          |      |

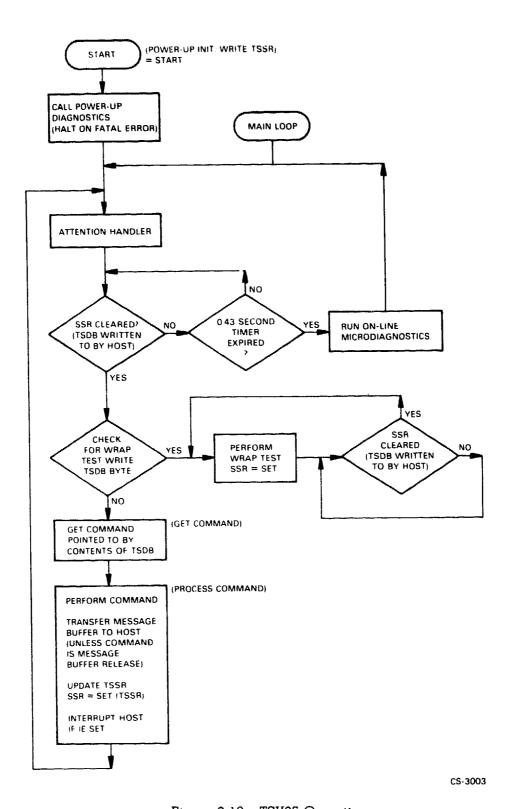

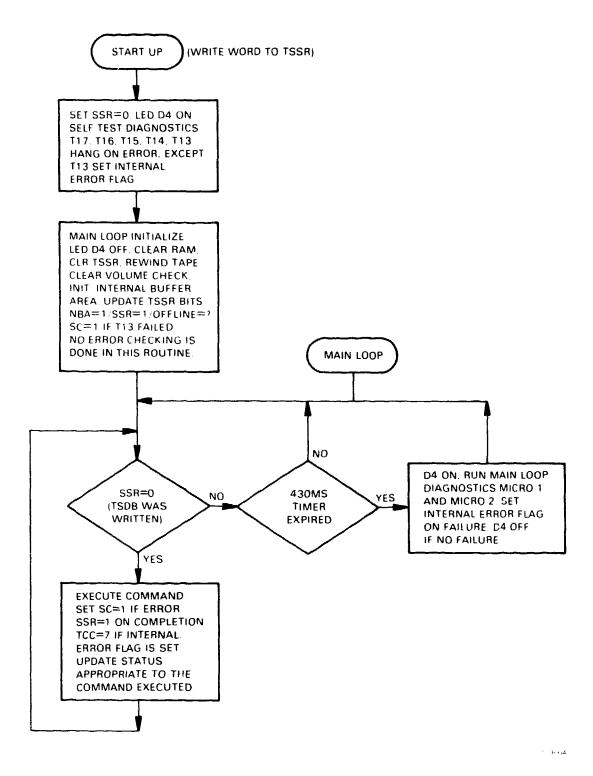

| 8.4.1.2          | Main Loop                                         |      |

| 8.4.1.3          | TSDB Byte Wrap                                    |      |

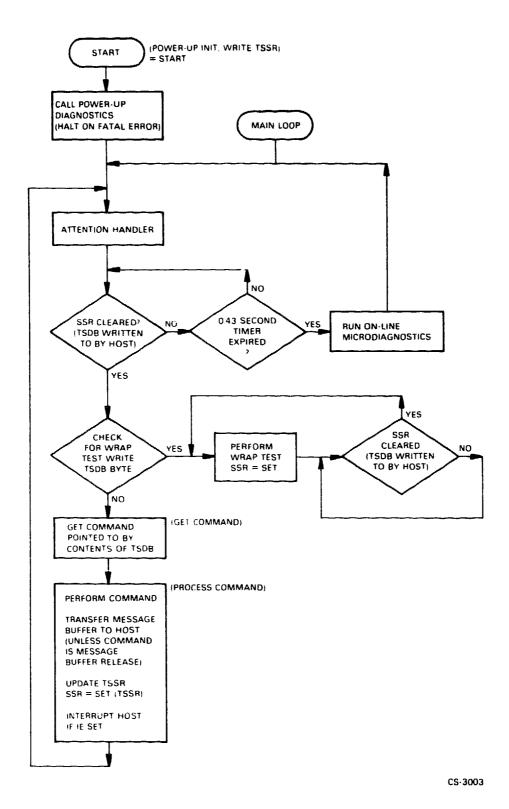

| 8.4.2            | Attention Handler                                 | 8-48 |

| 8.4.3            | Get Command                                       | 8-49 |

| 8.4.4            | Process Command                                   | 8-50 |

| 8.4.5            | Firmware Diagnostic Aids                          | 8-52 |

| 8.4.5.1          | Toggle In Routine                                 |      |

| 8.4.5.2          | Startup                                           |      |

| 8.4.5.3          | Boot Code                                         |      |

| 8.4.6            | Programming Example                               |      |

Page

|                    |                                                   | Page |

|--------------------|---------------------------------------------------|------|

| CHAPTER            | 9 TSV05-A/B TECHNICAL DESCRIPTION                 |      |

| 9.1                | INTRODUCTION                                      | 9-1  |

| 9.1.1              | Scope                                             | 9-1  |

| 9.1.2              | Conventions                                       |      |

| 9.1.3              | Terminology                                       | 9-2  |

| 9.2                | GENERAL DESCRIPTION                               |      |

| 9.2.1              | M7196 Q-Bus Interface/Controller Module           | 9-4  |

| 9.2.1.1            | Q-Bus Interface                                   | 9-4  |

| 9.2.1.2            | Microprocessor                                    |      |

| 9.2.1.3            | Tape Transport Bus Interface                      |      |

| 9.2.2              | TS05 Tape Transport Unit                          | 9-7  |

| 9.2.2.1            | Data Formatter Interface                          |      |

| 9.2.2.2            | Microprocessor                                    | 9-7  |

| 9.2.2.3            | Electromechanical Assemblies                      |      |

| 9.2.3              | Major Data Flows                                  |      |

| 9.3                | FUNCTIONAL DESCRIPTION                            |      |

| 9.3.1              | M7196 Q-Bus Interface/Controller Module Operation |      |

| 9.3.1.1            | Q-Bus Interface (Sheets D1 and D2)                |      |

| 9.3.1.2            | CSR and Data Memory (Sheet D3)                    |      |

| 9.3.1.3            | Tape Unit Interface (Sheet D4)                    | 9-17 |

| 9.3.1.4            | Program Sequencer and Tape Status In (Sheet D5)   | 9-18 |

| 9.3.1.5            | Arithmetic Logic Unit (Sheet D6)                  |      |

| 9.3.1.6            | Pipeline Registers (Sheet D7)                     |      |

| 9.3.1.7            | Microprogram ROMs (Sheet D8)                      | 9-19 |

| 9.3.1.8            | Loopback Registers (Sheet D9)                     |      |

| 9.3.1.9            | Microprocessor Words                              |      |

| 9.3.1.10           | Microprocessor Chip Description                   |      |

| 9.3.2              | M7196/TS05 Interface                              |      |

| 9.3.2.1            | Interface to Tape Unit                            |      |

| 9.3.2.2            | Interface to Controller                           |      |

| 9.3.3              | TS05 Tape Transport Unit                          | 0-40 |

| 9.3.3.1            | Tape Transport Microprocessor                     | 0.41 |

| 9.3.3.2            | FIRMWARE DESCRIPTION                              | 9-42 |

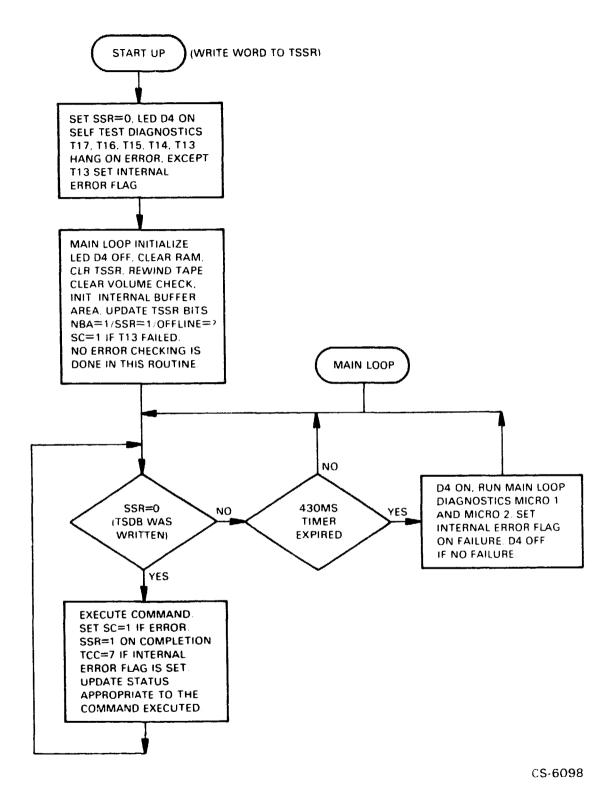

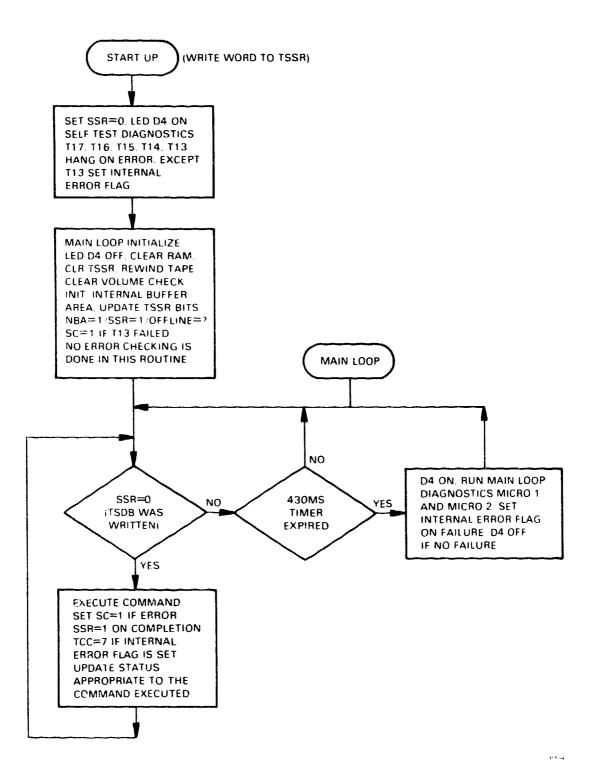

| 9.4<br>9.4.1       | Diagnostic                                        | 9-42 |

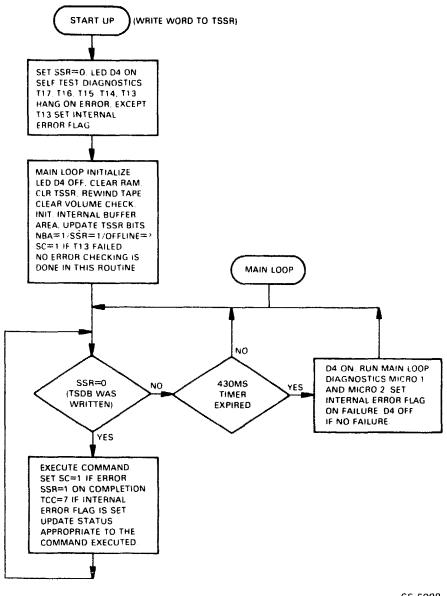

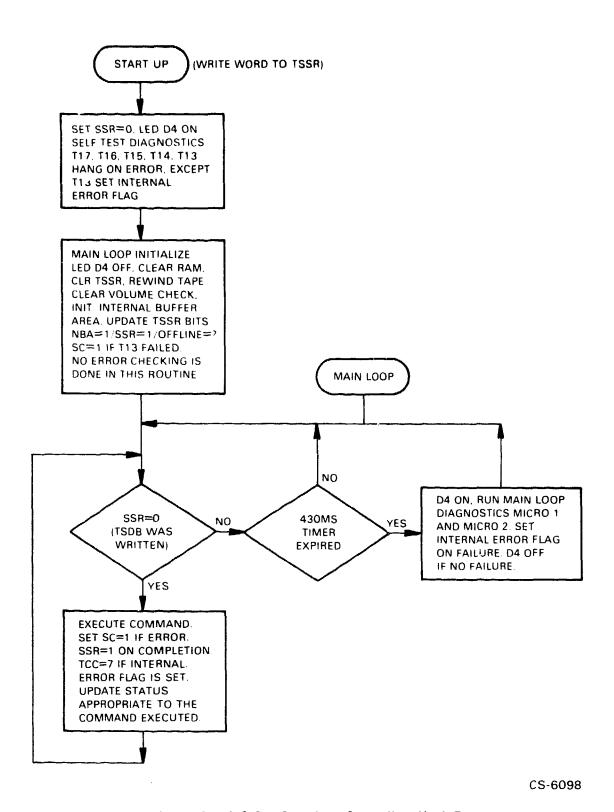

| 9.4.1<br>9.4.1.1   | Power-Up                                          | 9-43 |

| 9.4.1.1            | Main Loop                                         | 9-44 |

| 9.4.1.3            | TSDB Byte Wrap                                    | 9-47 |

| 9.4.1.3            | Attention Handler                                 | 9-48 |

| 9.4.3              | Get Command                                       | 9.49 |

| = :                | Process Command                                   |      |

| 9.4.4<br>9.4.5     | Firmware Diagnostic Aids                          |      |

| 9.4.5.1            | Toggle In Routine                                 | 9.50 |

| 9.4.5.1<br>9.4.5.2 | Startup                                           | 0.53 |

| 9.4.5.3            | Boot Code                                         | 9.56 |

| 9.4.5.3            | Programming Example                               | 9-57 |

|                    |                                                   |      |

|             | Pag                                       | <b>;•</b>  |

|-------------|-------------------------------------------|------------|

| CHAPTE      |                                           |            |

| TECHNIC     | CAL DESCRIPTION                           |            |

| 10.1        | OVERVIEW                                  | 1          |

| 10.1        | REGISTERS                                 | _          |

| 10.2.1      | Bus Address Register (TSBA)               |            |

| 10.2.1      | Data Buffer Register (TSDB)               |            |

| 10.2.3      | Status Register (TSSR)                    |            |

| 10.2.4      | Extended Data Buffer Register (TSDBX) 10- |            |

| 10.2.5      | Extended Status Register 0 (XST0) 10-     |            |

| 10.2.6      | Extended Status Register 1 (XST1) 10-     |            |

| 10.2.7      | Extended Status Register 2 (XST2) 10-     |            |

| 10.2.8      | Extended Status Register 3 (XST3) 10-     | 19         |

| 10.2.9      | Extended Status Register 4 (XST4) 10-     | 21         |

| 10.2.10     | Summary of Registers                      | 22         |

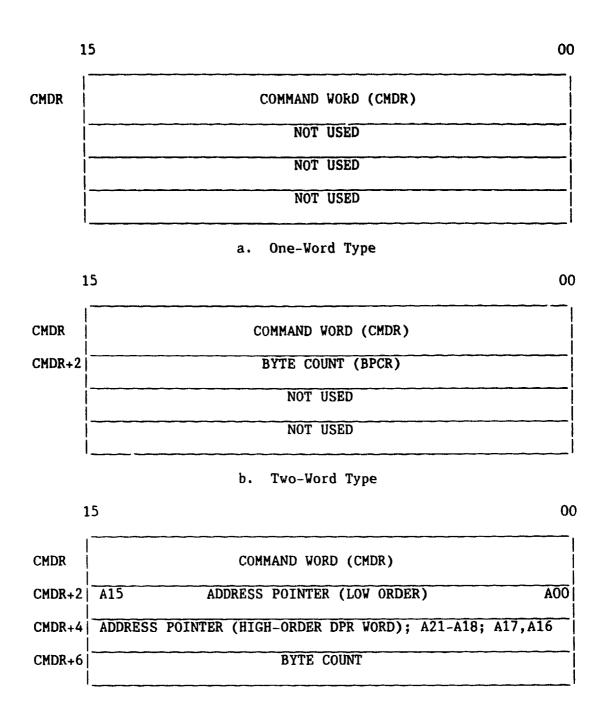

| 10.3        | PACKET PROCESSING                         | 25         |

| 10.3.1      | Buffer Ownership and Control              | 25         |

| 10.3.2      | Buffer Control on Attentions              | 27         |

| 10.3.3      | Message Packet Format                     |            |

| 10.3.4      | General Status Handling Information       |            |

| 10.4        | COMMANDS                                  |            |

| 10.4.1      | Command Packet Definitions                |            |

| 10.4.2      | Get Status Command                        |            |

| 10.4.3      | Read Command                              |            |

| 10.4.4      | Write Characteristics Command             |            |

| 10.4.5      | Write Command                             |            |

| 10.4.6      | Position Command                          |            |

| 10.4.7      | Format Command                            |            |

| 10.4.8      | Control Command                           |            |

| 10.4.9      | Initialize Command                        |            |

| 10.4.10     | Write Subsystem Memory Command            |            |

| 10.5        | RECORD BUFFERING (-A/B ONLY)              |            |

| 10.5.1      | Read Buffering                            | 58         |

| 10.5.2      | Write Buffering                           | 60         |

| E DOCATO    | DE E ODPOSTOSTIONO                        |            |

| APPEND.     | IX A SPECIFICATIONS                       |            |

| <b>A</b> .1 | MECHANICAL AND ELECTRICAL SPECIFICATIONS  | <u>i-1</u> |

| A.2         | ENVIRONMENTAL CONSIDERATIONS              |            |

| A.2.1       | Operating Conditions                      | 1-6        |

| A.2.2       | Nonoperating Conditions                   |            |

| A.2.3       | Emissions                                 | 1-7        |

|             |                                           |            |

| APPEND      | IX B MANUAL LOADING                       |            |

|                                                                         | P                                                                                                                                                                                                                                     | age                                            |

|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| APPENDIX                                                                | C RACK MOUNTING PROCEDURES                                                                                                                                                                                                            |                                                |

| C.1<br>C.1.1<br>C.1.2<br>C.2<br>C.2.1<br>C.2.2<br>C.3<br>C.3.1<br>C.3.2 | TSV05-A AND -SA Cabinet Preparation TS05 Installation  TSV05-SK Cabinet Preparation TS05 Installation  CSV05-Z Cabinet Preparation TSV05-Z Cabinet Preparation TSV05-Installation  TSV05 Installation                                 | C-1<br>C-5<br>C-5<br>C-11<br>C-13<br>C-13      |

| APPENDIX                                                                | D CABINET INSTALLATION PROCEDURES                                                                                                                                                                                                     |                                                |

| D.1<br>D.1.1<br>D.1.2<br>D.1.3<br>D.2                                   | H9642/H9642 CABINET INSTALLATION PROCEDURES Tools Required                                                                                                                                                                            | D-1<br>D-2<br>D-4                              |

| FIGURES                                                                 | I THE HANDION DIGINE DESCRIPTION                                                                                                                                                                                                      |                                                |

| Figure No.                                                              | Title                                                                                                                                                                                                                                 | age                                            |

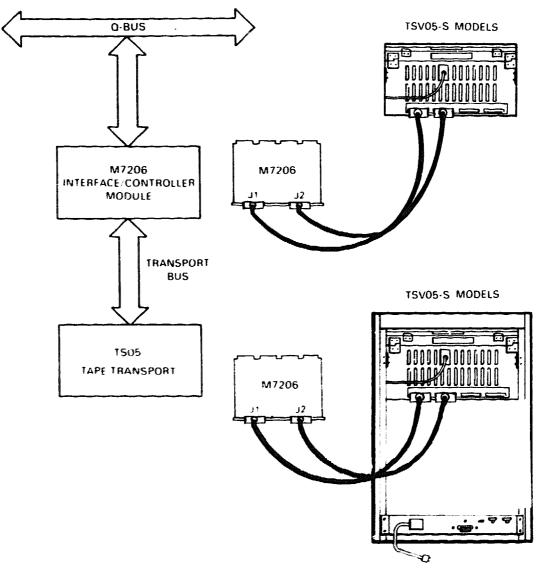

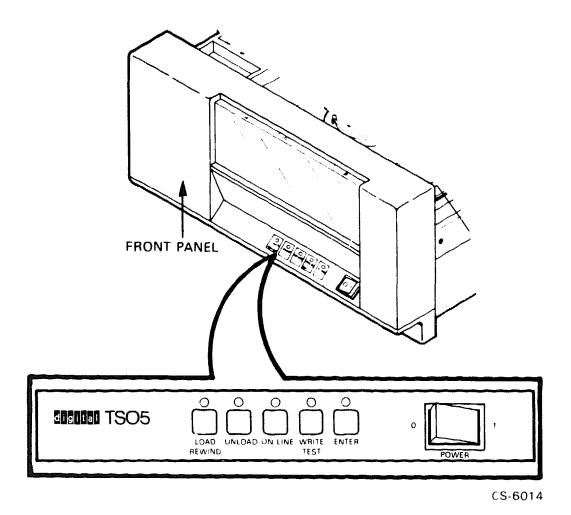

| 1-1<br>1-2<br>1-3<br>1-4<br>2-1<br>2-2<br>2-3<br>2-4<br>2-5             | TSV05-A Subsystem Components TSV05-B Subsystem Components TSV05-S Subsystem Components Operator Front Panel Cabinet Access Requirements Power Line Connections Cabinet Carton Removal Cabinet Shipping Brackets Raising Leveling Feet | 1-6<br>1-7<br>1-10<br>2-3<br>2-4<br>2-7<br>2-8 |

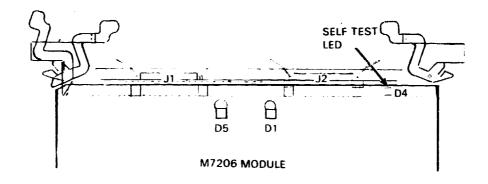

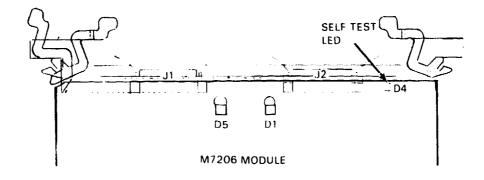

| 2-7<br>2-8<br>2-9<br>2-10<br>2-11<br>2-12                               | Opening Cabinet Door M7206-PA Module CK-TS05-nn Cable Kit Components Cabinet Top Cover Tape Transport Top Cover Tachometer and Takeup Hub                                                                                             | 2-11<br>2-12<br>2-14<br>2-16<br>2-18<br>2-19   |

# FIGURES (Cont)

| Figure No. | Title                                                       | Page   |

|------------|-------------------------------------------------------------|--------|

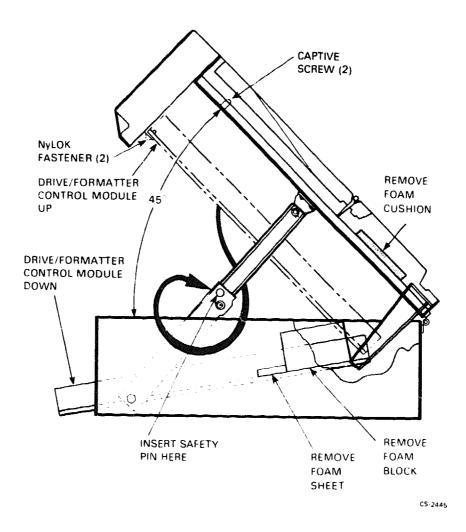

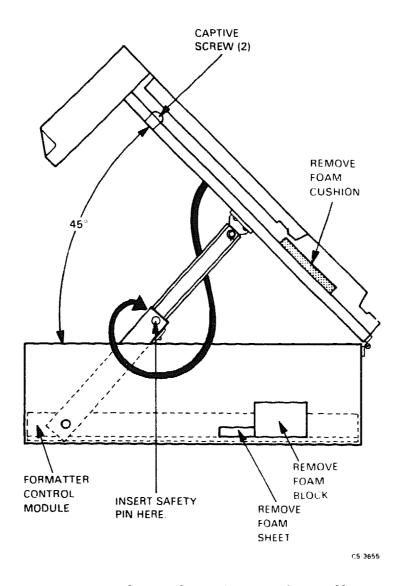

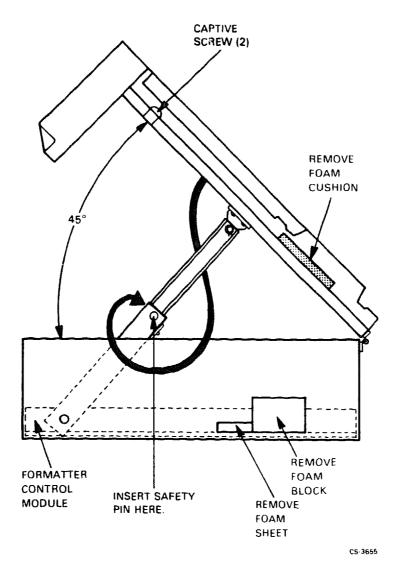

| 2-14       | Service Access Position (Diecast Unit)                      | . 2-24 |

| 2-15       | Front Panel Controls and Indicators                         | . 2-25 |

| 2-16       | Inserting Tape                                              | . 2-27 |

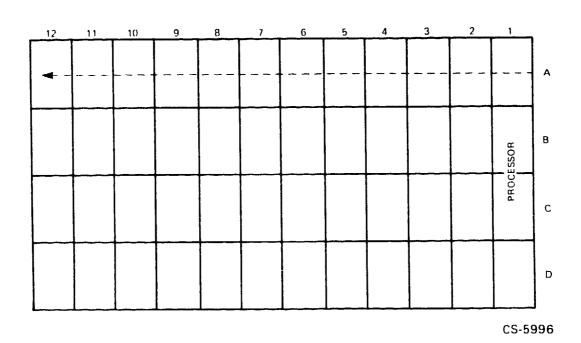

| 2-17       | BA200 Series Configuration Worksheet                        | . 2-30 |

| 2-18       | Bus Grant Continuity Path                                   | . 2-33 |

| 2-19       | SYSGEN Utility Display                                      | . 2-34 |

| 2-20       | M7206 Switch and Jumper Identification                      | . 2-37 |

| 2-21       | M7206 Vector and Address Switches                           | . 2-38 |

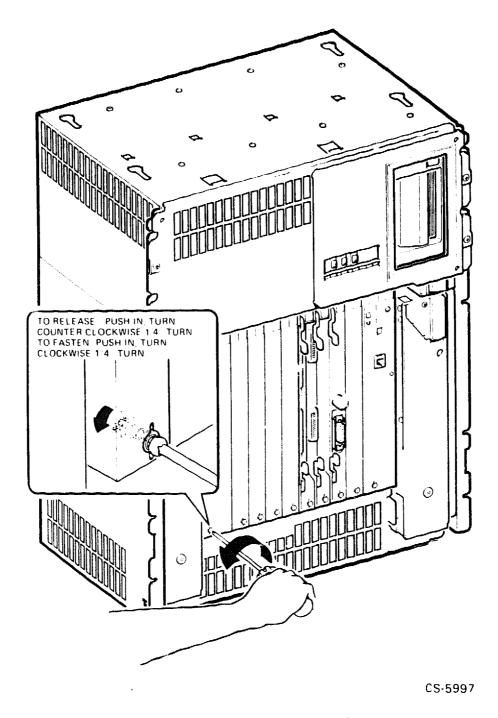

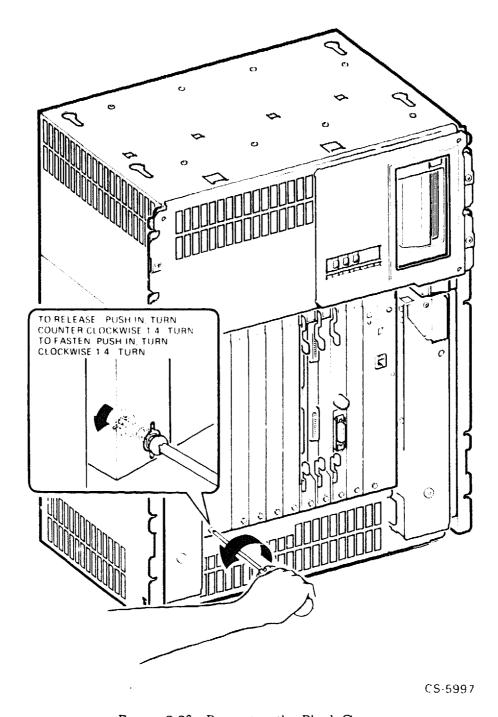

| 2-22       | Unlocking the Front Cover                                   | . 2-40 |

| 2-23       | Removing the Front Cover                                    | . 2-41 |

| 2-24       | Releasing the Captive Screws                                | . 2-43 |

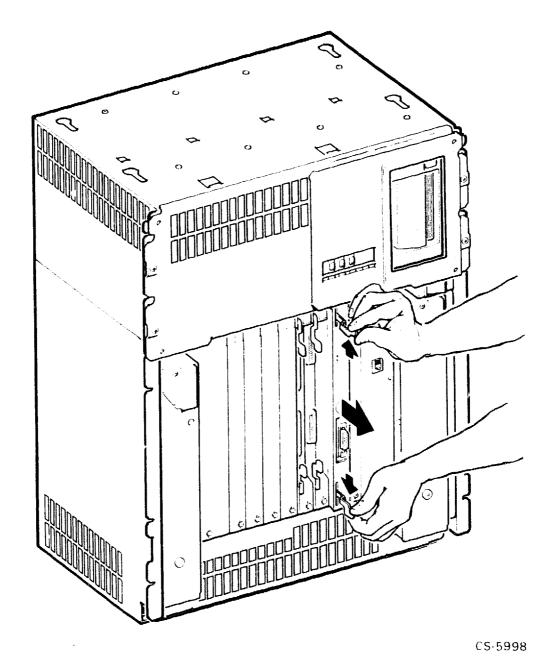

| 2-25       | Unlocking the Release Levers                                | . 2-44 |

| 2-26       | Removing the Blank Cover                                    | . 2-46 |

| 2-27       | Attaching the Gap Filler Assembly                           | . 2-48 |

| 2-28       | Inserting the Module                                        | . 2-50 |

| 2-29       | Ground Connections                                          | . 2-52 |

| 2-30       | Cabling the Tape Transport                                  | . 2-53 |

| 3-1        | Cabinet Access Requirements                                 | 3-3    |

| 3-2        | Power Line Connections                                      | 3-4    |

| 3-3        | Cabinet Carton Removal                                      | 3-6    |

| 3-4        | Cabinet Shipping Brackets                                   | 3-7    |

| 3-5        | Raising Leveling Feet                                       | 3-8    |

| 3-6        | Deskidding the Cabinet                                      | . 3-10 |

| 3-7        | Opening Cabinet Door                                        | . 3-11 |

| 3-8        | M7196 Module                                                | . 3-13 |

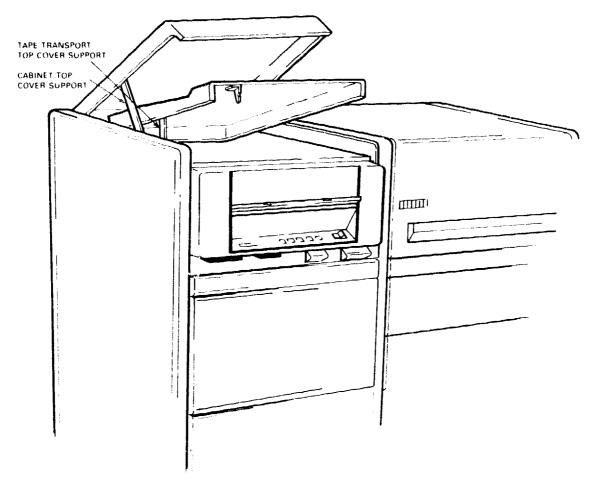

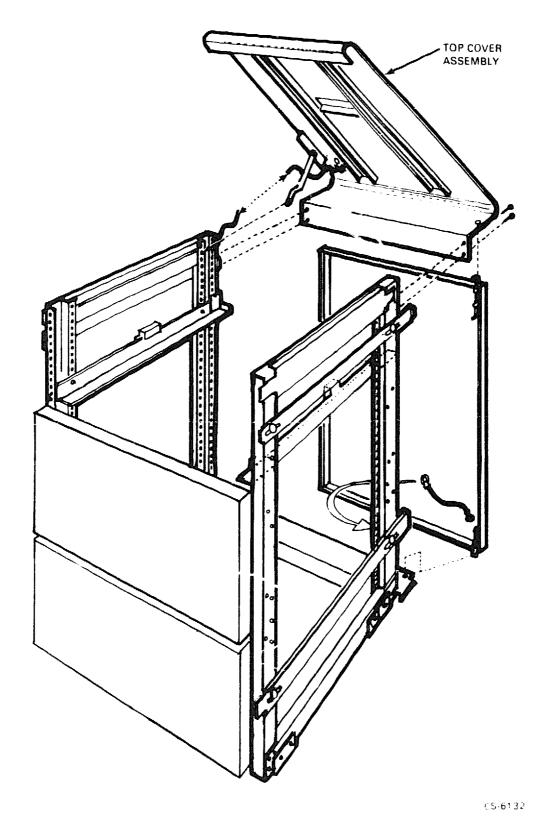

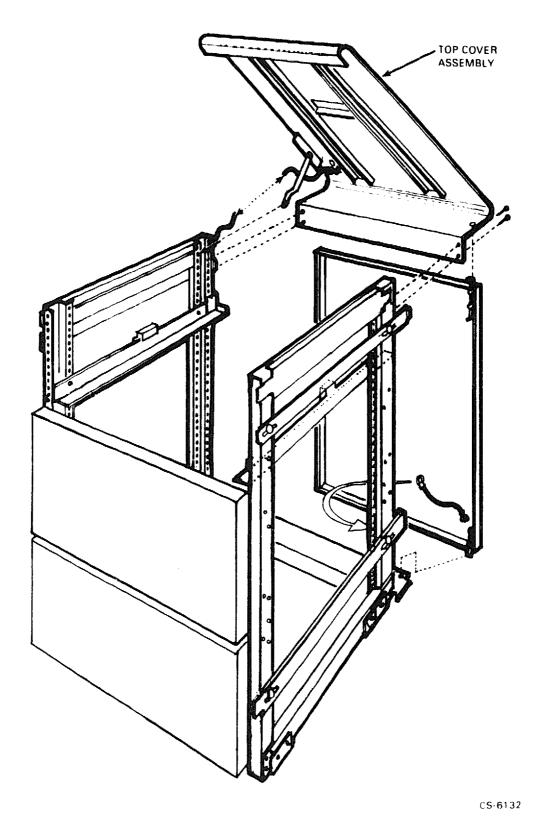

| 3-9        | Cabinet Top Cover                                           | . 3-17 |

| 3-10       | Tape Transport Top Cover                                    | . 3-18 |

| 3-11       | Tachometer and Takeup Hub                                   | . 3-19 |

| 3-12       | Service Access Position (Sandcast Unit)                     | . 3-21 |

| 3-13       | Service Access Position (Diecast Unit)                      | . 3-22 |

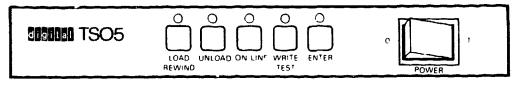

| 3-14       | Front Panel Controls and Indicators                         | . 3-24 |

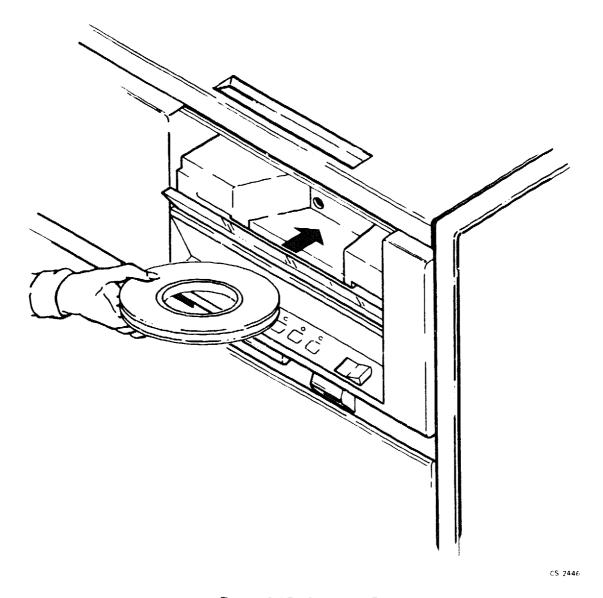

| 3-15       | Inserting Tape                                              | . 3-26 |

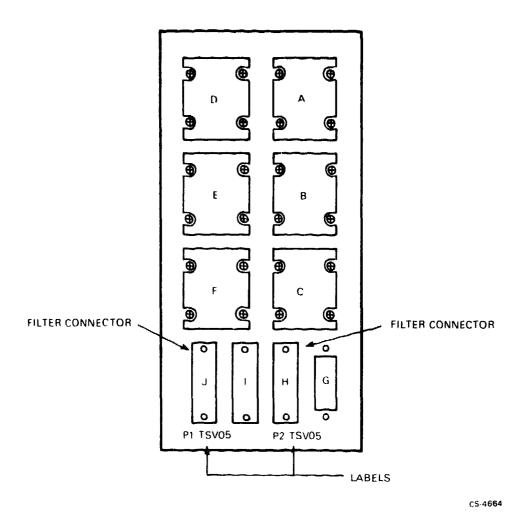

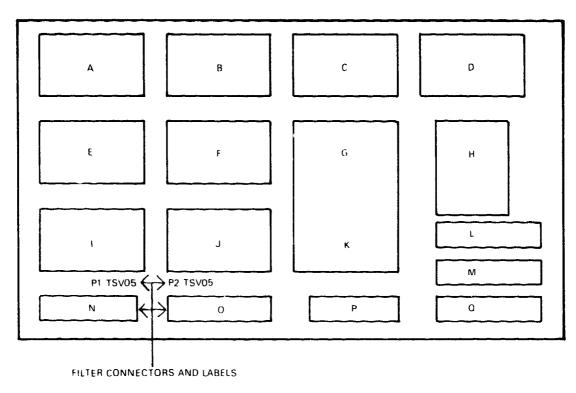

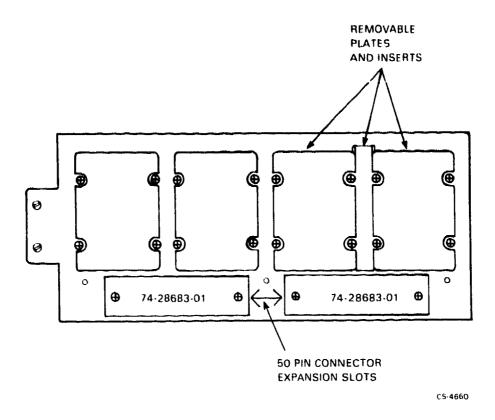

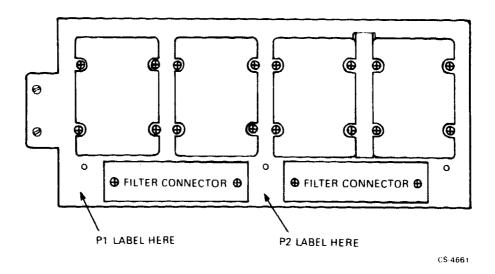

| 3-16       | TSV05 Filter Connector Mounting BA123A                      | . 3-31 |

| 3-17       | TSV05 Filter Connector Mounting, Deep Cabinet               |        |

| 3-18       | BA23A I/O Distribution Panel                                |        |

| 3-19       | BA23A with TSV05 Filter Connector Mounting (without DECnet) | . 3-34 |

| 3-20       | BA23A with TSV05 Filter Connector Mounting (with DECnet)    |        |

| 3-21       | M7196 Switch and Jumper Identification                      | . 3-36 |

| 3-22       | M7196 Vector and Address Switches                           | . 3-37 |

| 3-23       | TSV05 Cable Configuration                                   |        |

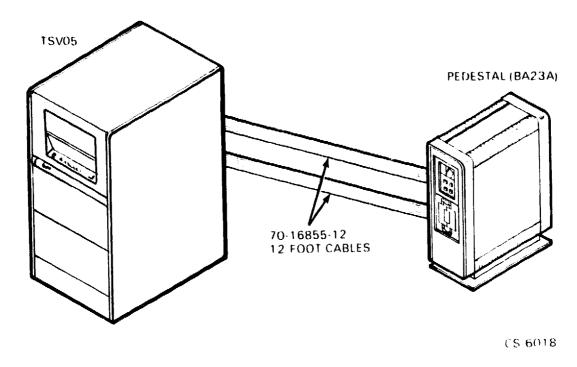

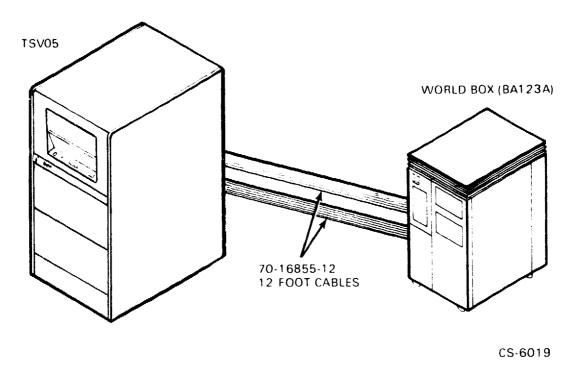

| 3-24       | Configuring the TSV05 with the BA23A Pedestal               | . 3-40 |

| 3-25       | Configuring the TSV05 with the BA123A World Box             | . 3-40 |

| 4-1        | Locating the Interface/Control Module Self-Test LED         |        |

| 5-1        | Locating the Bus Interface Controller Module Self-Test LED  | 5-2    |

| 6-1        | Opening the Front Door Panel                                | 6-3    |

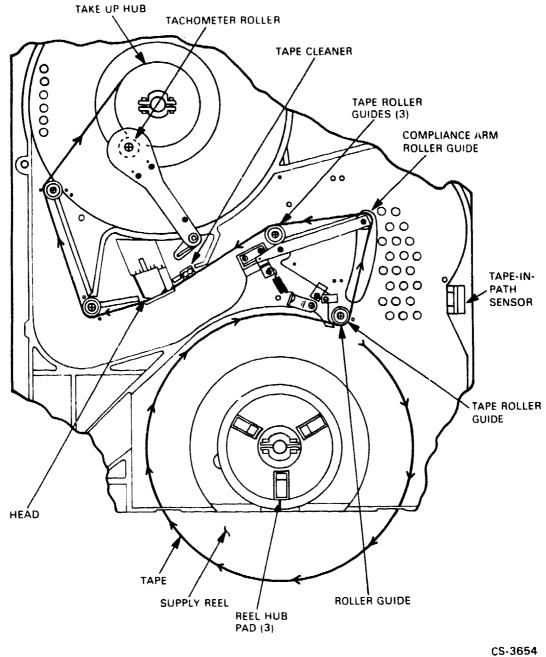

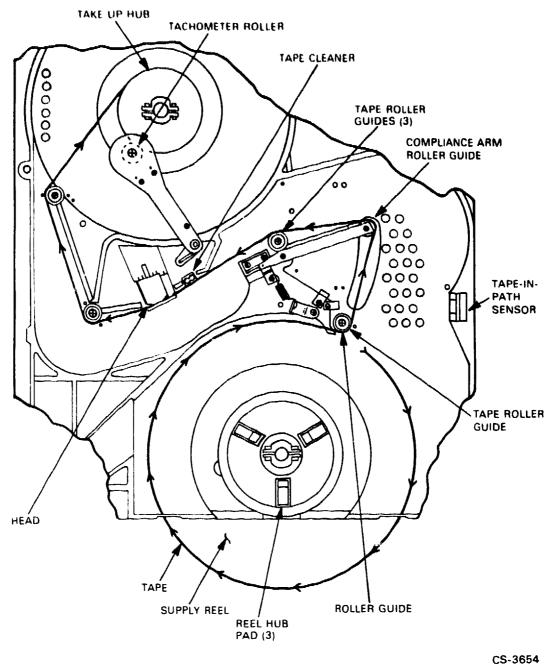

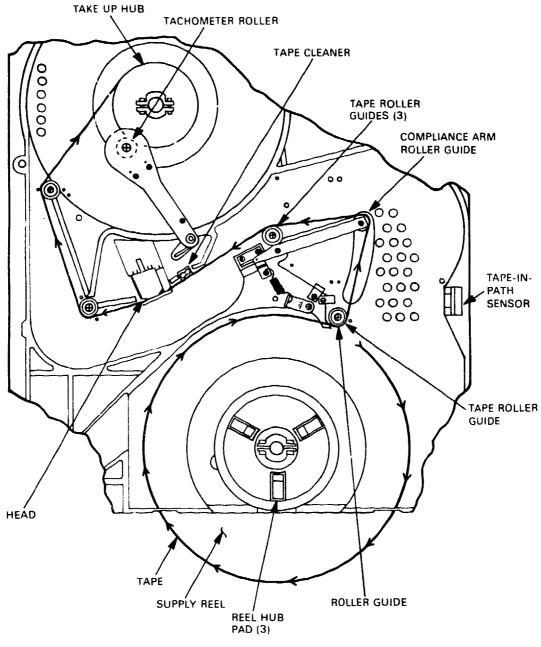

| 7-1        | Accessing the Tape Path Area                                | 7-6    |

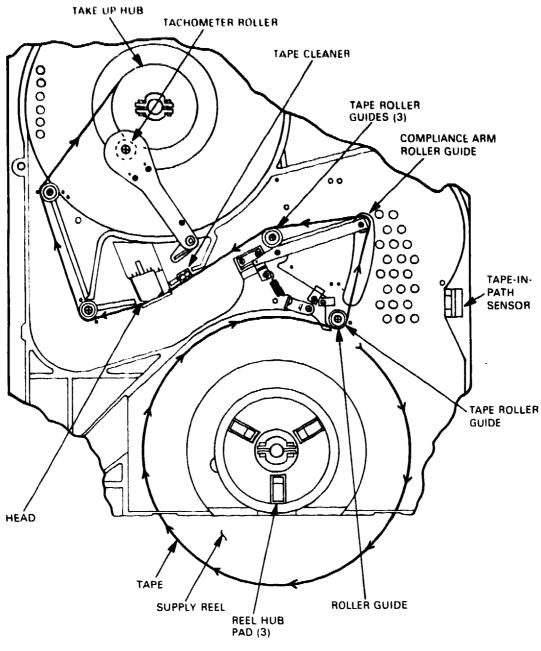

| 7-2        | Tape Path and Related Parts                                 | 7-8    |

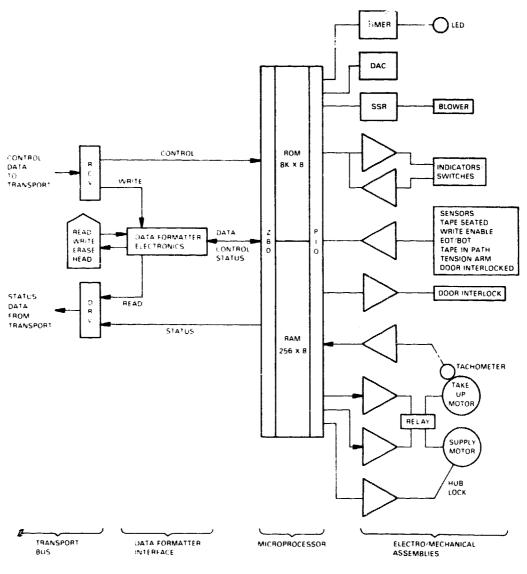

| 8-1        | M7206 Q-Bus Interface/Controller Block Diagram              |        |

| 8-2        | TS05 Tape Transport Block Diagram                           |        |

# FIGURES (Cont)

| Figure No. | Title                                          | Page    |

|------------|------------------------------------------------|---------|

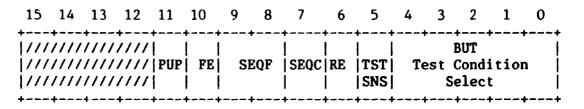

| 8-3        | Word 0                                         |         |

| 8-4        | Word 1                                         |         |

| 8-5        | Word 2                                         | 8-23    |

| 8-6        | Word 3                                         |         |

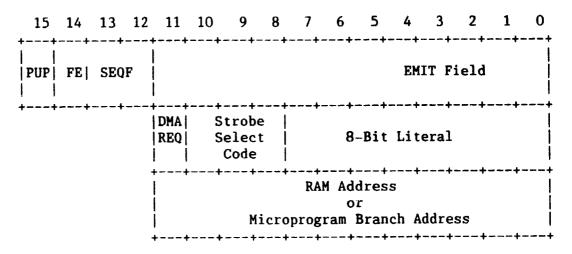

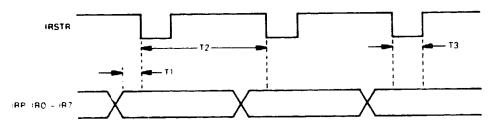

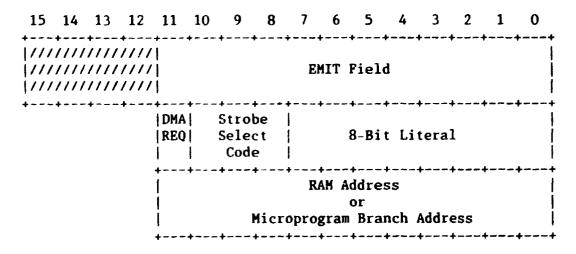

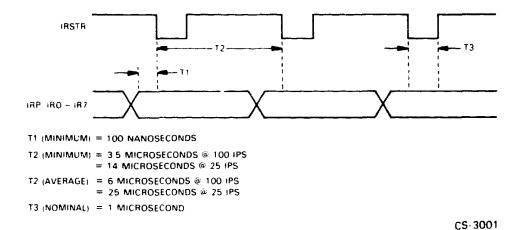

| 8-7        | Write Strobe Timing                            |         |

| 8-8        | Read Strobe Timing                             |         |

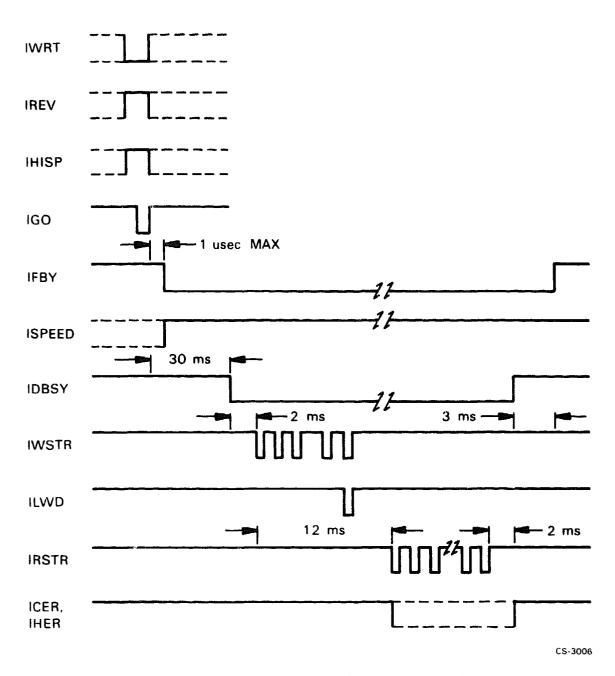

| 8-9        | Write Forward [64 cm/s (25 in/s)]              |         |

| 8-10       | TSV05 Operation                                |         |

| 8-11       | Diagnostic Flowchart                           |         |

| 8-12       | Firmware Diagnostic Flowchart                  |         |

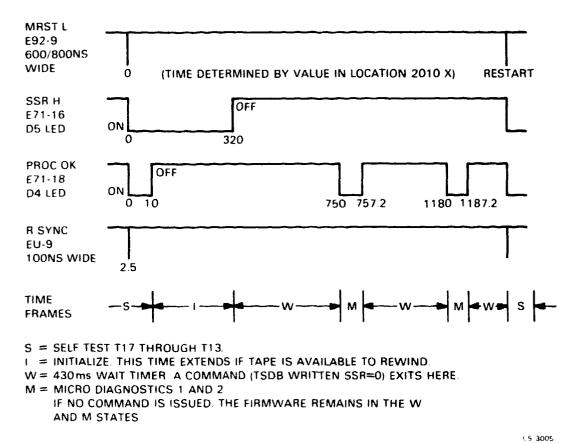

| 8-13       | Firmware Diagnostic Timing                     | . 8-55  |

| 9-1        | M7196 Q-Bus Interface/Controller Block Diagram | 9-5     |

| 9-2        | TS05 Tape Transport Block Diagram              |         |

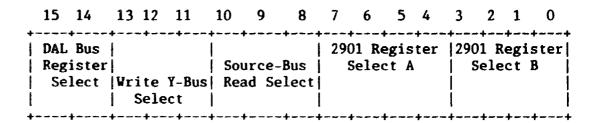

| 9-3        | Word 0                                         | . 9-19  |

| 9-4        | Word 1                                         | . 9-21  |

| 9-5        | Word 2                                         | . 9-23  |

| 9-6        | Word 3                                         | . 9-25  |

| 9-7        | Write Strobe Timing                            | . 9-32  |

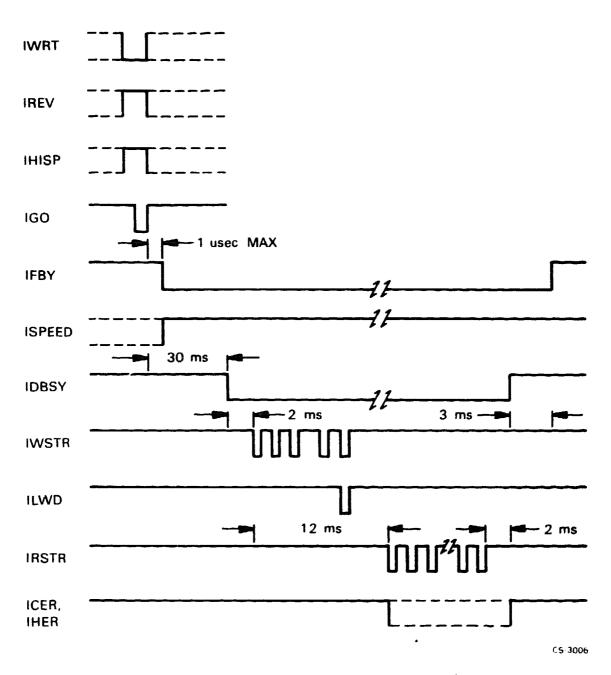

| 9-8        | Read Strobe Timing                             | . 9-32  |

| 9-9        | Write Forward [64 cm/s (25 in/s)]              | . 9-33  |

| 9-10       | TSV05 Operation                                | 9-43    |

| 9-11       | Diagnostic Flowchart                           | . 9-46  |

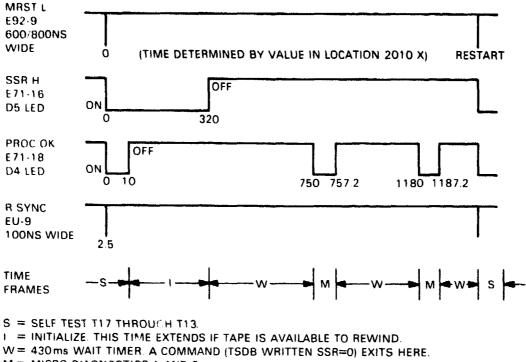

| 9-12       | Firmware Diagnostic Flowchart                  | . 9-54  |

| 9-13       | Firmware Diagnostic Timing                     |         |

| 10-1       | Command Packet Types                           |         |

| 10-2       | TSBA Register Format                           | . 10-6  |

| 10-3       | TSDB Register Format                           | . 10-8  |

| 10-4       | TSSR Register Format                           | 10-9    |

| 10-5       | TSDBX Register Format                          | . 10-13 |

| 10-6       | XSTO Register Format                           | 10-14   |

| 10-7       | XST1 Register Format                           | 10-17   |

| 10-8       | XST2 Register Format                           | 10-10   |

| 10-9       | XST3 Register Format                           | 10-13   |

| 10-10      | XST4 Register Bit Definitions                  | 10-21   |

| 10-11      | TCUOE Enterplad Status Paristers               | 10-22   |

| 10-12      | TSV05 Extended Status Registers                | 10-23   |

| 10-13      | TSV05 Command Register Format                  | 10.29   |

| 10-14      | Command Packet Header Word                     | 10-29   |

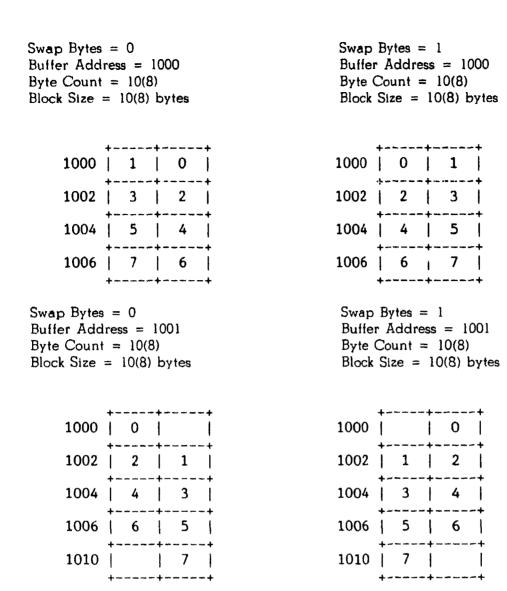

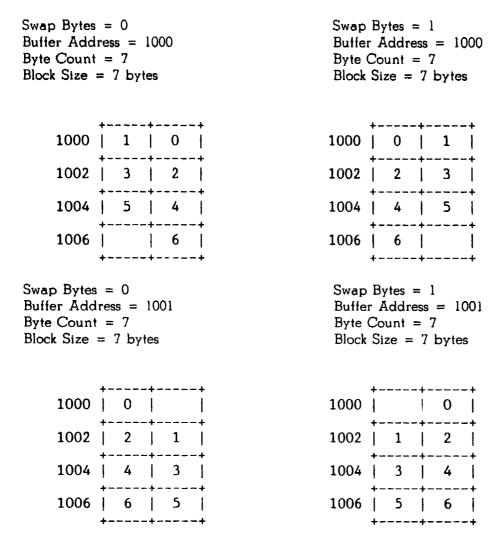

| 10-15      | Memory/Tape Data Byte Positioning              | 10-31   |

| 10-16      | Get Status Command Packet                      | 10-41   |

| 10-17      | Read Command Packet                            | 10-40   |

| 10-18      | Write Characteristics Command Format           | 10-46   |

| 10-19      | Write Command Packet                           | 10.51   |

| 10-20      | Position Command Packet                        | 10-51   |

| 10-21      | Position Command Packet                        | 10-53   |

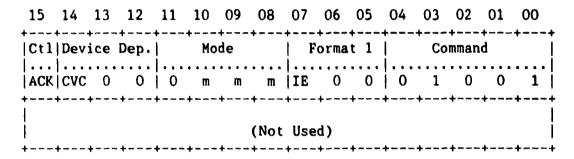

| 10-22      | Format Command Packet                          | 10-54   |

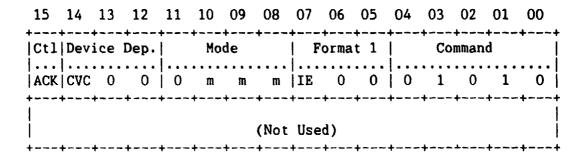

| 10-23      | Control Command Packet                         | 10-33   |

| 10-24      | Initialize Command Packet                      | . 10-30 |

# FIGURES (Cont)

| Figure No.                                                                              | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Page                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B-1                                                                                     | Accessing the Tape Path Area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | B-2                                                                                                                                                                         |

| B-2                                                                                     | Tape Threading Path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                             |

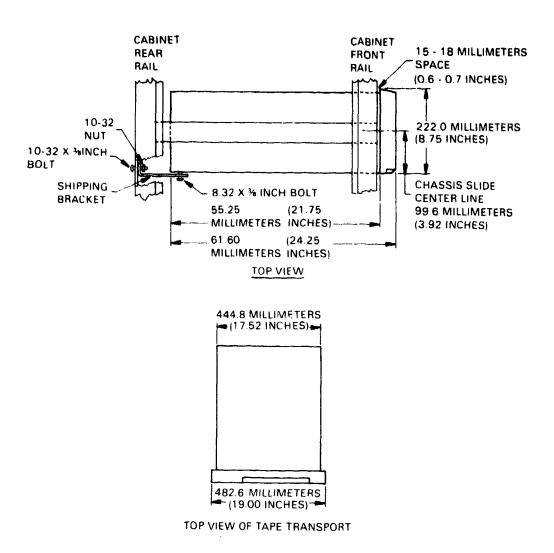

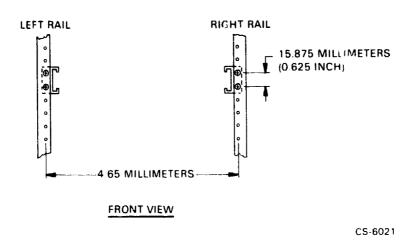

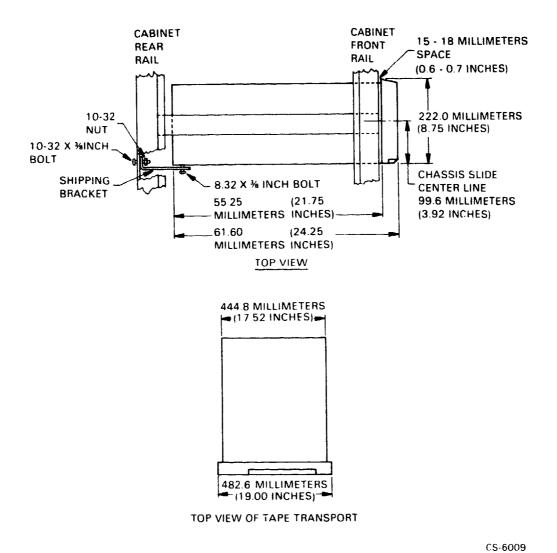

| C-1                                                                                     | TSV05-A [-SA] Mounting Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | C-3                                                                                                                                                                         |

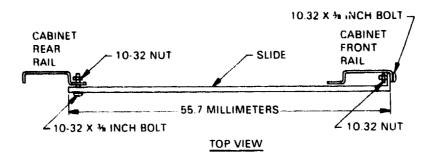

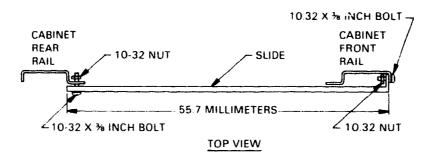

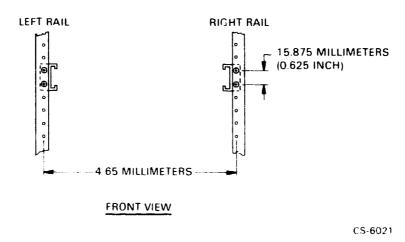

| C-2                                                                                     | Chassis Slide Mounting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | C-4                                                                                                                                                                         |

| C-3                                                                                     | Opening Cabinet Door                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                             |

| C-4                                                                                     | Removing Side Panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                             |

| C-5                                                                                     | Cabinet Preparation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                             |

| C-6                                                                                     | Installing a Side Panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                             |

| C-7                                                                                     | TS05 Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                             |

| C-8                                                                                     | Opening Cabinet Door                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                             |

| C-9                                                                                     | Removing Side Panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                             |

| C-10                                                                                    | Cabinet Preparation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                             |

| C-11                                                                                    | Installing a Side Panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                             |

| C-12                                                                                    | TSV05-Z Mounting Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                             |

| C-13                                                                                    | Chassis Slide Mounting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                             |

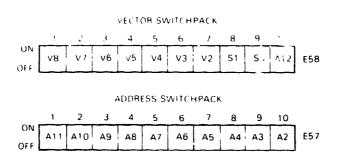

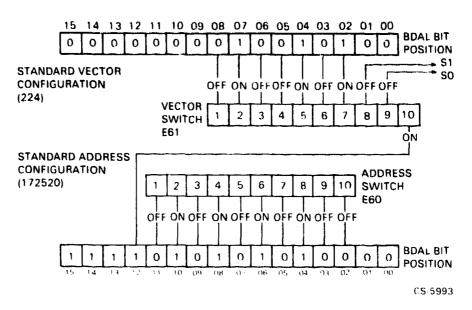

| D-1<br>D-2                                                                              | Removing Side Panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                             |