# DECpc™ 400ST Series Technical Reference Manual

Oruer Number ER-PCT15-TR-002

Digital Equipment Corporation Maynard, Massachusetts

#### August 1992

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation.

Digital Equipment Corporation assumes no responsibility for any errors that might appear in this document.

The software, if any, described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license. No responsibility is assumed for the use or reliability of software or equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Restricted Rights: Use, duplication, or disclosure by the U.S. Government is subject to restrictions as set forth in subparagraph (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at DFARS 252 227-7013.

DECpc 100ST Series Technical Reference Manual Copyright<sup>®</sup> Digital Equipment Corporation. All Rights Reserved.

#### Printed in U.S.A.

Centronics is a trademark of Centronics Corporation.

Dallas is a registered trademark of Dallas Semiconductor.

IBM, PC/XT/AT, and PS/2 are registered trademarks of International Business

Machines Corporation.

Intel is a registered trademark of Intel Corporation.

Intel486 and DX2 are trademarks of Intel Corporation.

Microsoft, MS-DOS, MS OS/2, and Windows are registered trademarks of Microsoft Corporation.

Phoenix BIOS is a trademark of Phoenix Technologies Ltd.

SCO Unix is a trademark of The Santa Cruz Operation, Inc.

SIMM is a registered trademark of Wang Laboratories.

Texas Instruments is a registered trademark of Texas Instruments Corporation

Western Digital is a registered trademark of Western Digital Corporation.

## The following are trademarks of Digital Equipment Corporation:

DEC DECstation RSTS

DEC/CMS DECwriter RSX

DEC/MMS DIBOL UNIBUS

DECnet EduSystem VAX

DECsystem-10 IAS VAXcluster

DECSYSTEM-20 MASSBUS VMS

DECUS PDP VT

DECpc

#### The FCC wants you to know...

This equipment has been tested and found to comply with the limits for a Class B digital device pursuant to Part 15 of the FCC rules. These limits are designed to provide reasonable protection against interference in a residential installation. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, can cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the asser is encouraged to try to correct the interference by one or more of the following measures:

- Reorient the receiving antenna.

- Relocate the computer with respect to the receiver.

- Move the computer away from the receiver.

- Connect the computer into an outlet on a circuit different from that to which the receiver is connected.

- Move the cables connected to the computer to minimize the interference.

- Tighten all screws on cables and the computer housing.

- Install blank panels, originally supplied with the computer, in all unused card slots.

If necessary, the user should consult the dealer or an experienced radio/television technician for additional suggestions. The user may find the following booklet prepared by the Federal Communications Commission helpful: *How to Identify and Resolve Radio-TV Interference Problems*.

This booklet is available from the U.S. Government Printing Office, Washington, D.C., 20402. Stock No. 004-00398-5.

| CAUTION                                                                                                                                                                                                                                                                                    |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Any changes or modifications not expressly approved by the grantee of this device can void the user's authority to operate the equipment.                                                                                                                                                  |  |  |

| NOTE                                                                                                                                                                                                                                                                                       |  |  |

| If a Class A device is installed within this computer, then the computer is to be considered a Class A computer.                                                                                                                                                                           |  |  |

| NOTE                                                                                                                                                                                                                                                                                       |  |  |

| To maintain the Class B limit on this computer product, only peripherals (computer input/output devices, terminals, printers) that comply with the Class B limits may be attached. Operation with non-compliant peripherals is likely to result in interference to radio and TV reception. |  |  |

This device complies with Part 15 of the FCC Rules. Operation of this device is subject to the following two conditions: (1) This device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

This digital apparatus does not exceed the Class B limits for radio noise emissions set out in the radio interference regulations of the Canadian Department of Communications.

この装置は、第二種情報装置(住宅地域又はその隣接した地域において使用されるべき情報装置)で住宅地域での電波障害防止を目的とした情報処理装置等電波障害自主規制協議会(VCCI)基準に適合しております。

しかし、本装置をラジオ、テレビジョン受信機に近接してご使用になると、受信障害の原因となることがあります。

取扱説明書に従って正しい取り扱いをして下さい。

This equipment is in the 2nd Class category (information equipment to be used in a residential area or an adjacent area thereto) and conforms to the standards set by the Voluntary Control Council For Interference by Data Processing Equipment and Electronic Office Machines aimed at preventing radio interference in such residential area.

When used near a radio or TV receiver, it may become the cause of radio interference. Read the instructions for correct handling.

This equipment meets or exceeds requirements for safety in the U.S. (UL 1950), Canada (CSA C22.2 No. 950), and Europe (EN 60950/IEC 950) with Nordic requirements.

This equipment meets or exceeds the ergonomic requirements of ZH1/618 and is certified to bear the GS mark by TUV Rheinland of N.A.

This equipment has been tested for radio frequency emissions and has been verified to meet VDE 0871 Class B

#### Declaration of the Manufacturer or Importer

We hereby certify that the DECpc 400ST Series computer is in compliance with vfg 1046/1984 and is RFI suppressed.

The marketing and sale of the equipment was reported to the German Postal Service.

The right to retest this equipment to verify compliance with the regulation was given to the German Postal Service.

Digital Equipment Corporation

| About This Manual                         | χV    |

|-------------------------------------------|-------|

| Purpose                                   | χv    |

| Audience                                  | ΧV    |

| Organization of This Manual               | XV    |

| Notational Conventions                    | xviii |

| Special Notices                           | xix   |

| Related Documentation                     | XX    |

| 1 System Board Overview                   | 1-1   |

| Introduction                              | 1 - 1 |

| DECpc 400ST System Board Features         | 1-4   |

| EISA Slots                                | 1-5   |

| 82357 Integrated System Peripheral        | 1-5   |

| 82358DT EISA Bus Controller               | 1-6   |

| Programmable ASIC Devices                 | 1-6   |

| IDE Hard Drive Interface                  | 1-6   |

| Diskette Drive Controller                 | 1-6   |

| Asynchronous Communications Element (ACE) | 1-6   |

| Serial Ports                              | 1-7   |

| Parallel Port                             | 1-7   |

| Keyboard and Mouse Controller             | 1-7   |

| PS/2 Keyboard Port and PS/2 Mouse Port    | 1-8   |

| Speaker                                   | 1-8   |

| System BIOS                                                                                                                                                                                                                                 |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Non-Volatile Memory                                                                                                                                                                                                                         |    |

| CMOS Battery Backup/Real-Time Clock                                                                                                                                                                                                         |    |

| Direct Memory Access (DMA)                                                                                                                                                                                                                  |    |

| System Memory                                                                                                                                                                                                                               |    |

| Buses                                                                                                                                                                                                                                       |    |

| BX Bus                                                                                                                                                                                                                                      |    |

| EISA Bus                                                                                                                                                                                                                                    |    |

| MEM Bus                                                                                                                                                                                                                                     |    |

| X Bus                                                                                                                                                                                                                                       | ,  |

| Z Bus                                                                                                                                                                                                                                       |    |

| System Configuration Utility                                                                                                                                                                                                                |    |

| CPU Module Features                                                                                                                                                                                                                         |    |

| Memory Module Features                                                                                                                                                                                                                      | ., |

| CPU Module Technology                                                                                                                                                                                                                       |    |

| •                                                                                                                                                                                                                                           |    |

| CPU Module Technology                                                                                                                                                                                                                       |    |

| CPU Module Technology                                                                                                                                                                                                                       |    |

| CPU Module Technology  Introduction Intel486 Microprocessor.                                                                                                                                                                                |    |

| CPU Module Technology  Introduction Intel486 Microprocessor Basic Architecture                                                                                                                                                              |    |

| Introduction Intel486 Microprocessor Basic Architecture Central Processing Unit                                                                                                                                                             |    |

| Introduction Intel486 Microprocessor Basic Architecture Central Processing Unit. Memory Management Unit                                                                                                                                     |    |

| Introduction Intel486 Microprocessor Basic Architecture Central Processing Unit. Memory Management Unit Numeric Coprocessor Unit                                                                                                            |    |

| CPU Module Technology  Introduction Intel486 Microprocessor  Basic Architecture  Central Processing Unit  Memory Management Unit  Numeric Coprocessor Unit  Cache Memory Unit                                                               |    |

| Introduction Intel486 Microprocessor Basic Architecture Central Processing Unit Memory Management Unit Numeric Coprocessor Unit Cache Memory Unit Modes of Operation                                                                        |    |

| Introduction Intel486 Microprocessor Basic Architecture Central Processing Unit Memory Management Unit Numeric Coprocessor Unit Cache Memory Unit Modes of Operation External Caches                                                        |    |

| Introduction Intel486 Microprocessor Basic Architecture Central Processing Unit Memory Management Unit Numeric Coprocessor Unit Cache Memory Unit Modes of Operation External Caches Write-Through Cache                                    |    |

| Introduction Intel486 Microprocessor Basic Architecture Central Processing Unit. Memory Management Unit Numeric Coprocessor Unit Cache Memory Unit Modes of Operation External Caches Write-Through Cache Write-Back Cache                  |    |

| Introduction Intel486 Microprocessor Basic Architecture Central Processing Unit Memory Management Unit Numeric Coprocessor Unit Cache Memory Unit Modes of Operation External Caches Write-Through Cache Write-Back Cache Base Architecture |    |

|   |                                        | Contents |

|---|----------------------------------------|----------|

| 3 | 82358 EISA Bus Controller              | 3-1      |

|   | Introduction                           | 3-1      |

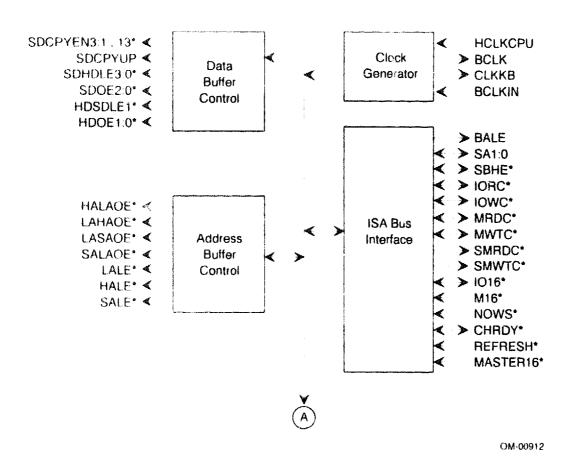

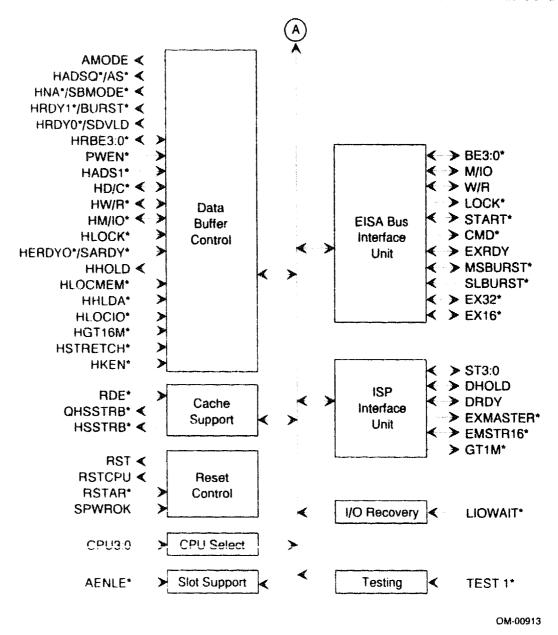

|   | Host Bus Interface                     | 3-4      |

|   | EISA and ISA Bus Interfaces            | 3-4      |

|   | Integrated System Peripheral Interface | 3-5      |

|   | Address Buffer Control                 | 3-5      |

|   | Data Buffer Control                    | 3-5      |

|   | Cache Support                          | 3-6      |

|   | Reset Control                          | 3-6      |

|   | I/O Recovery                           | 3-6      |

|   | Slot Support                           | 3-7      |

|   | Clock Generation                       | 3-7      |

|   | Pinouts                                | 3-7      |

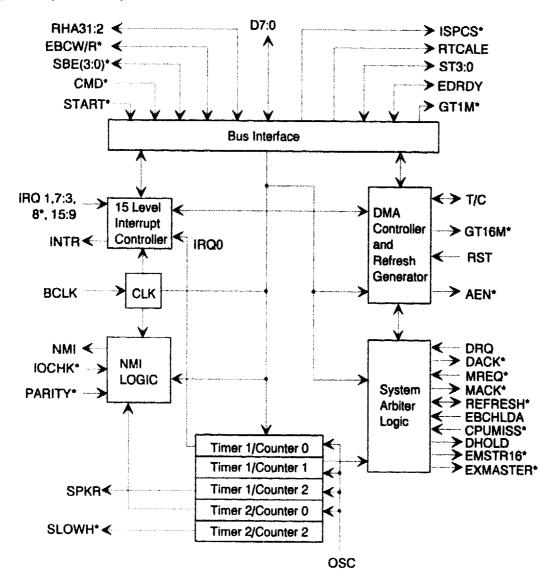

| 4 | Integrated System Peripheral           | 4-1      |

|   | Introduction                           | 4-1      |

|   | Bus Interface                          | 4-3      |

|   | DMA Controller and Refresh Generator   | 4-3      |

|   | System Arbiter                         | 4-8      |

|   | Timer/Counters                         | 4-8      |

|   | NMI Logic                              | 4-9      |

|   | Clock                                  | 4-9      |

|   | Interrupt Controller                   | 4-10     |

| egister Descriptions                                                                                                                                                                                                                                                                                                                                                              |          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| DMA Registers                                                                                                                                                                                                                                                                                                                                                                     |          |

| Chain Buffer Expiration Control                                                                                                                                                                                                                                                                                                                                                   |          |

| Channel Interrupt Status                                                                                                                                                                                                                                                                                                                                                          |          |

| Command Register                                                                                                                                                                                                                                                                                                                                                                  |          |

| Extended Mode Register                                                                                                                                                                                                                                                                                                                                                            |          |

| Mask Register                                                                                                                                                                                                                                                                                                                                                                     |          |

| Mode Register                                                                                                                                                                                                                                                                                                                                                                     |          |

| Request Register                                                                                                                                                                                                                                                                                                                                                                  |          |

| Set Chaining Mode Register                                                                                                                                                                                                                                                                                                                                                        |          |

| Set Chaining Mode Status                                                                                                                                                                                                                                                                                                                                                          |          |

| Status Register                                                                                                                                                                                                                                                                                                                                                                   |          |

| Stop Registers                                                                                                                                                                                                                                                                                                                                                                    |          |

| NMI Registers                                                                                                                                                                                                                                                                                                                                                                     |          |

| Timer/Counters                                                                                                                                                                                                                                                                                                                                                                    |          |

| Timer/Counters                                                                                                                                                                                                                                                                                                                                                                    |          |

| Pinouts  /D16C552 or TL16C552 Asynchronous Communication                                                                                                                                                                                                                                                                                                                          |          |

| Pinouts /D16C552 or TL16C552 Asynchronous Communication                                                                                                                                                                                                                                                                                                                           | S        |

| Pinouts /D16C552 or TL16C552 Asynchronous Communication lement                                                                                                                                                                                                                                                                                                                    | S        |

| Pinouts  /D16C552 or TL16C552 Asynchronous Communication lement  Introduction Serial Communication Ports                                                                                                                                                                                                                                                                          | S        |

| Pinouts  /D16C552 or TL16C552 Asynchronous Communication  lement  Introduction  Serial Communication Ports  Serial Port Register Descriptions                                                                                                                                                                                                                                     | S        |

| Pinouts  /D16C552 or TL16C552 Asynchronous Communication  lement  Introduction  Serial Communication Ports  Serial Port Register Descriptions  Receive Buffer Register                                                                                                                                                                                                            | S        |

| Pinouts  /D16C552 or TL16C552 Asynchronous Communication  lement  Introduction  Serial Communication Ports  Serial Port Register Descriptions  Receive Buffer Register  Transmit Buffer Register                                                                                                                                                                                  | S        |

| Pinouts  /D16C552 or TL16C552 Asynchronous Communication  Introduction Serial Communication Ports Serial Port Register Descriptions Receive Buffer Register Transmit Buffer Register Interrupt Enable Register                                                                                                                                                                    | S        |

| Pinouts  /D16C552 or TL16C552 Asynchronous Communication  lement  Introduction  Serial Communication Ports  Serial Port Register Descriptions  Receive Buffer Register  Transmit Buffer Register  Interrupt Enable Register  Interrupt Identification Register                                                                                                                    | S        |

| Pinouts  /D16C552 or TL16C552 Asynchronous Communication  Ilement  Introduction  Serial Communication Ports  Serial Port Register Descriptions  Receive Buffer Register  Transmit Buffer Register  Interrupt Enable Register  Interrupt Identification Register  FIFO Control Register                                                                                            | 5        |

| Pinouts  /D16C552 or TL16C552 Asynchronous Communication  Introduction Serial Communication Ports Serial Port Register Descriptions Receive Buffer Register Transmit Buffer Register Interrupt Enable Register Interrupt Identification Register FIFO Control Register Line Control Register                                                                                      | <b>S</b> |

| Pinouts  /D16C552 or TL16C552 Asynchronous Communication  lement  Introduction  Serial Communication Ports  Serial Port Register Descriptions  Receive Buffer Register  Transmit Buffer Register  Interrupt Enable Register  Interrupt Identification Register  FIFO Control Register  Line Control Register  Modem Control Register                                              | . S      |

| Pinouts  /D16C552 or TL16C552 Asynchronous Communication  lement  Introduction  Serial Communication Ports  Serial Port Register Descriptions  Receive Buffer Register  Transmit Buffer Register  Interrupt Enable Register  Interrupt Identification Register  FIFO Control Register  Line Control Register  Modem Control Register  Line Status Register                        | <b>S</b> |

| Pinouts  /D16C552 or TL16C552 Asynchronous Communication  lement  Introduction  Serial Communication Ports  Serial Port Register Descriptions  Receive Buffer Register  Transmit Buffer Register  Interrupt Enable Register  Interrupt Identification Register  FIFO Control Register  Line Control Register  Modem Control Register  Line Status Register  Modem Status Register | <b>S</b> |

| Pinouts  /D16C552 or TL16C552 Asynchronous Communication  lement  Introduction  Serial Communication Ports  Serial Port Register Descriptions  Receive Buffer Register  Transmit Buffer Register  Interrupt Enable Register  Interrupt Identification Register  FIFO Control Register  Line Control Register  Modem Control Register  Line Status Register                        | <b>S</b> |

|                                       | Contents |

|---------------------------------------|----------|

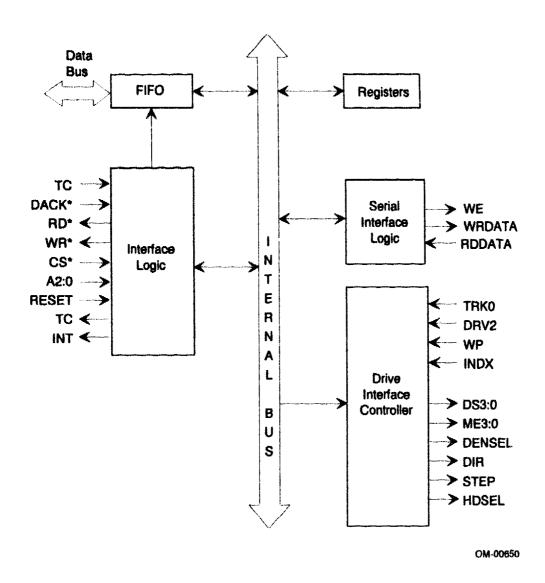

| 6 82077 Diskette Drive Controller     | 6-1      |

| Introduction                          | 6-1      |

| FIFO                                  | 6-3      |

| Interface Logic                       | 6-3      |

| Serial Interface Logic                | 6-3      |

| Drive Interface Controller            | 6-3      |

| General Registers                     | 6-4      |

| Digital Output Register               | 6-5      |

| Tape Drive Register                   | 6-5      |

| Main Status Register                  | 6-6      |

| Data Rate Select Register             | 6-6      |

| Data Register                         | 6-7      |

| Digital Input Register                | 6-7      |

| Configuration Control Register        | 6-7      |

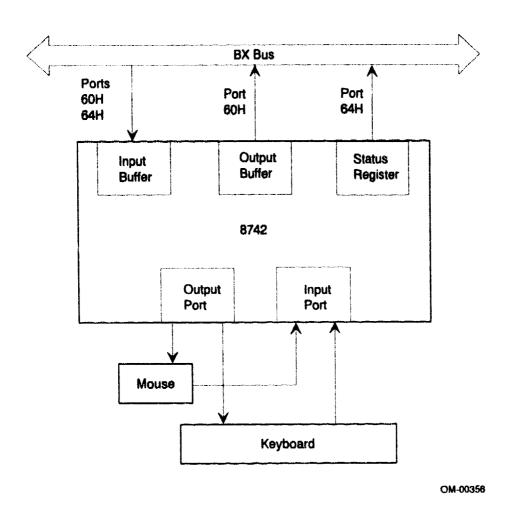

| Introduction                          | 7-1      |

| Status Register                       | 7-3      |

| Output Buffer                         | 7-4      |

| Input Buffer                          | 7-4      |

| Input and Output Ports                | 7-5      |

| Controller Commands                   | 7-6      |

| Keyboard and Mouse Data Stream        | 7-8      |

| Sending Data to the Keyboard          | 7-9      |

| Set/Reset Status Indicators (EDh)     | 7-9      |

| Echo (EEh)                            | 7-10     |

| Select Alternate Scan Codes (F0h)     | 7-10     |

| Read ID (F2h)                         | 7-10     |

| Set Typematic Rate/Delay (F3h)        | 7-11     |

| Enable (F4h)                          | 7-13     |

| Default Disable (F5h)                 | 7-13     |

| Set Default (F6h)                     | 7-13     |

| Set All Keys (F7h, F8h, F9h, and FAh) | 7-13     |

| Set Key Type (FBh, FCh, and FDh)      | 7-13     |

| Resend (FEh)                          | 7-13     |

| Reset (FFh)                           | 7-13     |

| Receiving Data from the Keyboard            | 7-14 |

|---------------------------------------------|------|

| Overrun or Key Detection Error (00h Or FFh) | 7-14 |

| Keyboard ID (83ABh)                         | 7-14 |

| BAT Completion Code (AAh)                   | 7-15 |

| Echo (EEh)                                  | 7-15 |

| BAT Failure Code (FCh)                      | 7-15 |

| Acknowledge (FAh)                           | 7-15 |

| Resend (FEh)                                | 7-15 |

| System-To-Mouse Commands                    | 7-16 |

| Reset Scaling (E6h)                         | 7-16 |

| Set Scaling (E7h)                           | 7-16 |

| Set Resolution (E8h)                        | 7-17 |

| Status Request (E9h)                        | 7-18 |

| Set Stream Mode (EAh)                       | 7-18 |

| Read Data (EBh)                             | 7-19 |

| Reset Wrap Mode (ECh)                       | 7-19 |

| Set Wrap Mode (EEh)                         | 7-19 |

| Set Remote Mode (F0h)                       | 7-19 |

| Read Device Type (F2h)                      | 7-19 |

| Set Sampling Rate (F3h)                     | 7-20 |

| Enable (F4h)                                | 7-20 |

| Disable (F5h)                               | 7-21 |

| Set Default (Fóh)                           | 7-21 |

| Resend (FEh)                                | 7-21 |

| Reset (FFh)                                 | 7-21 |

| Mouse-To-System Replies                     | 7-21 |

| Acknowledge (FAh)                           | 7-22 |

| Resend (FEh)                                | 7-22 |

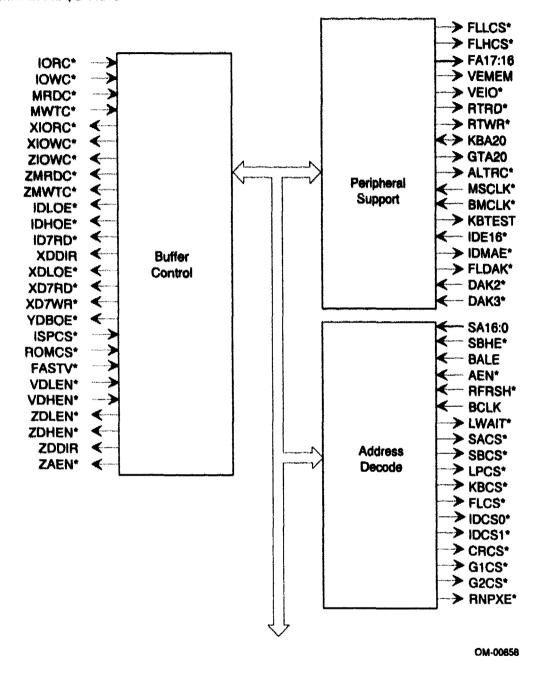

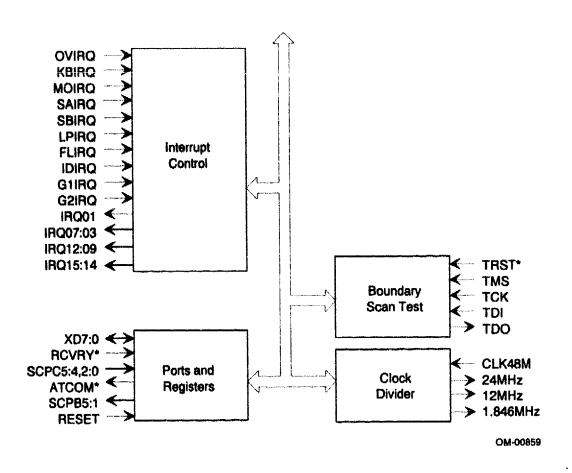

| 8 | Common Local I/O ASIC                | 8-1  |

|---|--------------------------------------|------|

|   | Introduction                         | 8-1  |

|   | Functional Description               | 8-3  |

|   | Address Decode                       | 8-6  |

|   | Boundary Scan                        | 8-7  |

|   | Buffer Control                       | 8-7  |

|   | Clock Divider                        | 8-8  |

|   | Interrupt Control                    | 8-8  |

|   | Peripheral Support                   | 8-8  |

|   | Ports and Registers                  | 8-9  |

|   | System Control Port Descriptions     | 8-11 |

|   | BIOS Counter Port                    | 8-11 |

|   | System Control Port A                | 8-12 |

|   | System Control Port B                | 8-13 |

|   | System Control Port C                | 8-14 |

|   | System Control Port D                | 8-15 |

|   | System Control Register Descriptions | 8-15 |

|   | Configuration Data Register (CDR)    | 8-15 |

|   | Configuration Index Register (CIR)   | 8-16 |

|   | EISA ID Registers                    | 8-16 |

| Configuration Register Descriptions                        | 8-16 |

|------------------------------------------------------------|------|

| ID Register                                                | 8-17 |

| Feature Control A Register                                 | 8-18 |

| Feature Control B Register                                 | 8-19 |

| Serial Port 1 Register                                     | 8-20 |

| Serial Port 2 Register                                     | 8-21 |

| Parallel Port Register                                     | 8-22 |

| Keyboard and Mouse Register                                | 8-23 |

| Diskette Register                                          | 8-24 |

| IDE Register                                               | 8-25 |

| General Purpose Peripheral 1 Register                      | 8-26 |

| General Purpose Peripheral 2 Register                      | 8-27 |

| General Purpose Chip 1 and 2 Select Mask Registers         | 8-28 |

| General Purpose Chip 1 and 2 Select Low Address Registers  | 8-28 |

| General Purpose Chip 1 and 2 Select High Address Registers | 8-28 |

| Shadow Register                                            | 8-29 |

| EISA ID Configuration Registers                            | 8-29 |

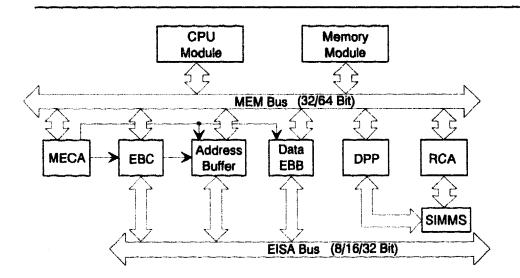

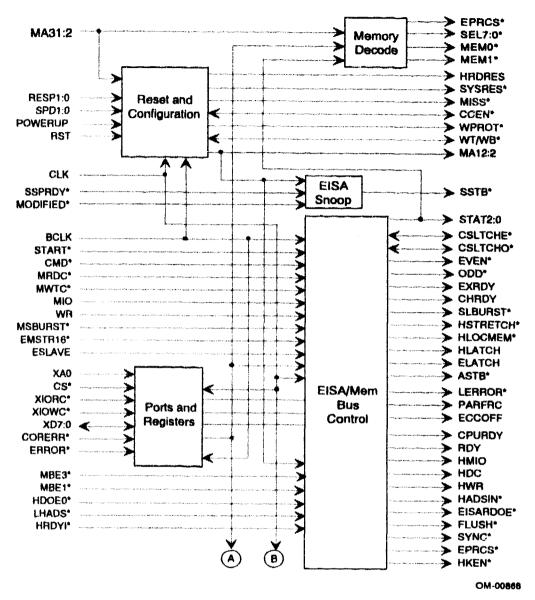

| 9 MEM Bus-To-EISA Control Array                            | 9-1  |

| Introduction                                               | 9-1  |

| Functional Description                                     | 9-2  |

| Boundary Scan Test                                         | 9-4  |

| EISA/MEM Bus Control                                       | 9-4  |

| Memory Decode                                              | 9-5  |

| Ports and Registers                                        | 9-5  |

| Reset and Configuration                                    | 9-8  |

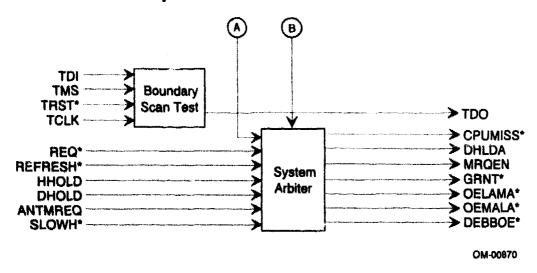

| System Arbitrator                                          | 9.9  |

| Register Descriptions                    |  |

|------------------------------------------|--|

| ID Register                              |  |

| Memory Attribute Registers               |  |

| Memory Attribute Range Registers         |  |

| BIOS Shadow Control Register             |  |

| Memory Decode and Control Register       |  |

| Memory Error Control Register            |  |

| Memory Error Address Registers           |  |

| Memory Partition Disable Register        |  |

| CPU Speed Register                       |  |

| CPU Module ID Register                   |  |

| Memory Partition Configuration Registers |  |

| Memory Partition Boundary Registers      |  |

| General Control Register                 |  |

| DPP, EBB, and RCA                        |  |

| Introduction                             |  |

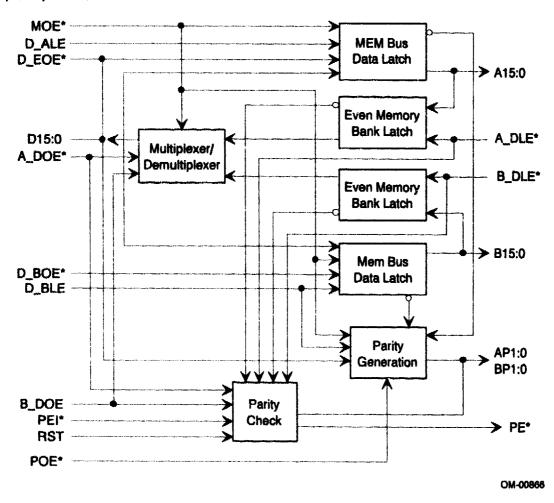

| DPP Functional Description               |  |

| Bus Latches                              |  |

| Multiplexer/Demultiplexer                |  |

| Parity Generation and Checking           |  |

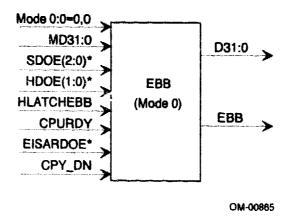

| EBB Functional Description               |  |

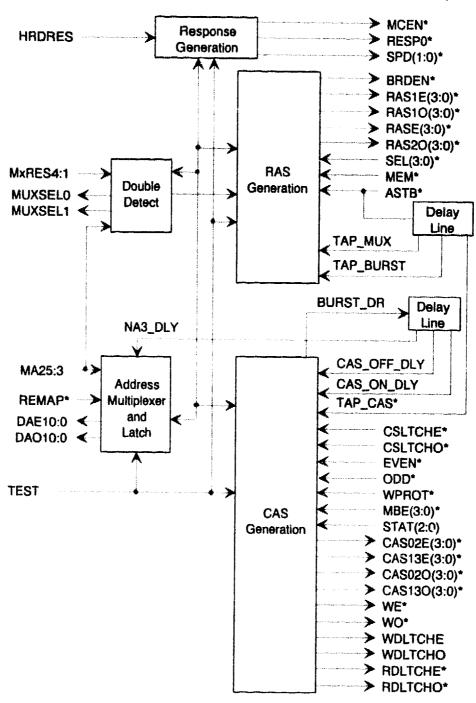

| RCA Functional Description               |  |

| Address Multiplexer and Latch            |  |

| CAS Generation.                          |  |

| Double Detect                            |  |

| RAS Generation                           |  |

| Response Generation                      |  |

|   | DS1287 Real-Time Clock                                      | 11-1  |

|---|-------------------------------------------------------------|-------|

|   | Introduction                                                | 11-1  |

|   | RTC I/O Operations                                          | 11-1  |

|   | Status Register A Bit Assignments                           | 11-5  |

|   | Status Register B Bit Assignments                           | 11-6  |

|   | Status Register C Bit Assignments                           | 11-7  |

|   | Status Register D Bit Assignments                           | 11-7  |

|   | Diagnostic Status                                           | 11-8  |

|   | Reason for Shut Down Bit Assignments                        | 11-9  |

|   | Type of Diskette Drive                                      | 11-10 |

|   | Type of Hard Disk Bit Assignments                           | 11-11 |

|   | Language Bit Assignments                                    | 11-12 |

|   | Installed Hardware Bit Assignments                          | 11-13 |

|   | Shadow Control Byte Bit Assignments                         | 11-14 |

|   | BIOS Options Bit Assignments                                | 11-14 |

|   | Manufacturer Option 1 Bit Assignments                       | 11-15 |

|   | Manufacturer Option 2 Bit Assignments                       | 11-16 |

|   | Manufacturer Option 3 Bit Assignments                       | 11-17 |

|   | Manufacturer Option 4 Bit Assignments                       | 11-18 |

|   | Manufacturer Option 5 Bit Assignments                       | 11-19 |

|   | Setup Information Bit Assignments                           | 11-20 |

|   | CPU Speed, Cache, and Extended CMOS Control Bit Assignments | 11-20 |

|   | Time-Of-Day Registers                                       | 11-21 |

| A | Specifications                                              | A-1   |

|   | Introduction                                                | A-1   |

|   | Computer Specifications                                     | A-2   |

|   | Expansion Slots                                             | A-4   |

|   | System Component Current Requirements                       | A-4   |

| B | BIOS Routines                                               | B-1   |

|   | Introduction                                                | B-1   |

|   | Interrupt Vector Table                                      | B-1   |

|   | DIOS Carrieros                                              | B-5   |

| C | Device Mapping                                                  | <b>C</b> -1 |

|---|-----------------------------------------------------------------|-------------|

| D | Configuring the Computer                                        | <b>D</b> -1 |

|   | Introduction                                                    | <b>D</b> -1 |

|   | Configuring Your Computer                                       | D-2<br>D-4  |

|   | Extended Memory Range Definition  Expansion Board Address Space | D-4<br>D-4  |

|   | Expansion Slot 4 Operation.                                     | D-5         |

| E | System Board Jumpers                                            | E-1         |

|   | Introduction                                                    | E-1         |

|   | System Board Jumpers                                            | E-2         |

|   | Diskette Write Protect                                          | E-5         |

|   | System Configuration Reset                                      | E-5         |

|   | Password                                                        | E-5         |

|   | Memory Bank 0, 1                                                | E-6         |

|   | FLASH Memory Write                                              | E-6         |

|   | FLASH Recovery Boot                                             | E-6         |

| F | Updating the System BIOS                                        | F-1         |

|   | Introduction                                                    | F-1         |

|   | BIOS File Header Information                                    | F-2         |

|   | FLASH Memory Update Utility                                     | F-3         |

|   | Verify FLASH Memory Area With a File                            | F-3         |

|   | Save FLASH Memory Area to a File                                | F-4         |

|   | Update FLASH Memory Area from a File                            | F-4         |

|   | BIOS Recovery Procedure                                         | E 5         |

| 3 C  | PU Modules                                                 | G-1  |

|------|------------------------------------------------------------|------|

| 1    | Introduction                                               | G-1  |

| (    | CPU Module Descriptions                                    | G-2  |

|      | 25 MHz CPU Module                                          | G-3  |

|      | 33 MHz CPU Module                                          | G-4  |

|      | 50 MHz CPU Module                                          | G-5  |

|      | Intel486 DX2 50 MHz CPU Module                             | G-6  |

|      | Intel486 DX2 66 MHz CPU Module .                           | G-7  |

| (    | CPU Module Jumpers                                         | G-8  |

|      | 25 MHz CPU Module Jumpers                                  | G-8  |

|      | 33 MHz CPU Module Jumpers                                  | G-10 |

|      | Intel486 DX2 50MHz and 66 MHz CPU Module Jumpers           | G-10 |

| Figu | res                                                        |      |

| 1-1  | DECpc 400ST Series System Board Block Diagram              | 1-2  |

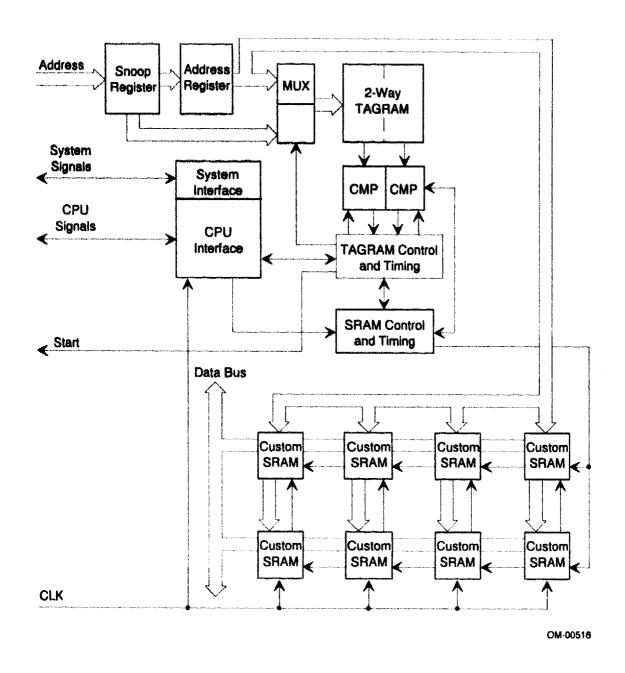

| 2-1  | External Cache Functional Block Diagram                    | 2-6  |

| 3-1  | 82358 EISA Bus Controller Block Diagram                    | 3-2  |

| 4-1  | 82357 Integrated System Peripheral Block Diagram           | 4-2  |

| 6-1  | Diskette Drive Controller Block Diagram                    | 6-2  |

| 7-1  | Keyboard and mouse Controller Block Diagram                | 7-2  |

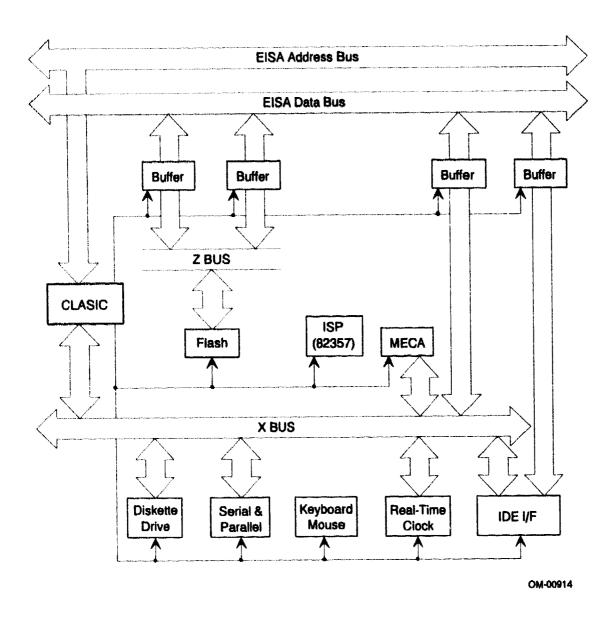

| 8-1  | Local I/O Bus Architecture                                 | 8-2  |

| 8-2  | CLASIC Functional Block Diagram                            | 8-4  |

| 9-1  | MECA/System Interface                                      | 9-1  |

| 9.2  | MECA Block Diagram                                         | 9-3  |

| 10-1 | DPP Block Diagram                                          | 10-2 |

| 10-2 | EBB Block Diagram                                          | 10-3 |

| 10-3 | RCA Block Diagram                                          | 10-5 |

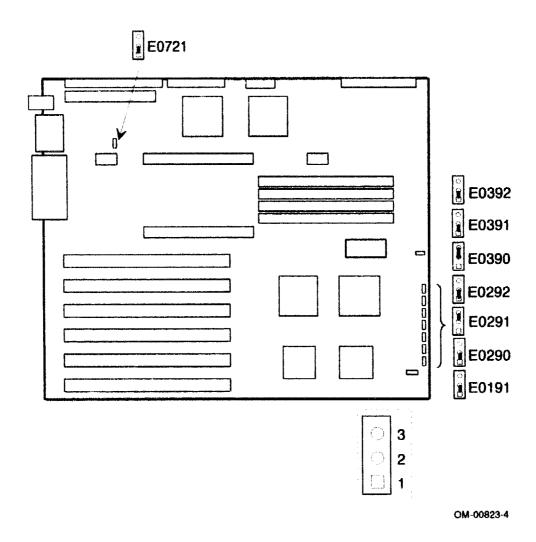

| E-1  | System Board Jumper Locations                              | E-3  |

| F-1  | Location of FLASH Write Enable and Recovery Jumpers        | F-6  |

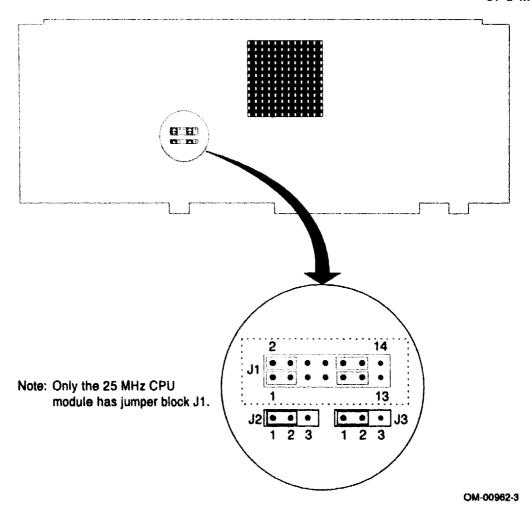

| G-1  | 25 MHz and 33 MHz CPU Module Jumper Settings               | G-9  |

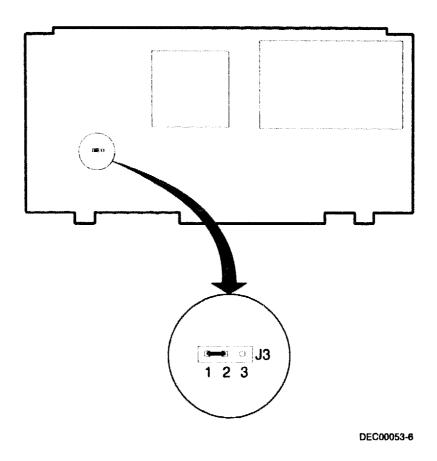

| G-2  | Intel486 DX2 50 MHz and 66 MHz CPU Module Jumper Locations | G-11 |

# **Tables**

| 1 - 1 | System Memory Allocation                                    |

|-------|-------------------------------------------------------------|

| 3-1   | EBC Signal Cross Reference                                  |

| 4-1   | DMA Controller Register Address Map                         |

| 4-2   | DMA Channel Registers Address Map                           |

| 4-3   | Timer/Counter Address Map                                   |

| 4-4   | Interrupt Controller Address Map                            |

| 4-5   | Chain Buffer Expiration Control Register Bit Assignments    |

| 4-6   | Channel Interrupt Status Register Bit Assignments           |

| 4-7   | Command Register Bit Assignments                            |

| 4-8   | Extended Mode Register Bit Assignments                      |

| 4-9   | Mask Register Bit Assignments                               |

| 4-10  | Mode Register Bit Assignments                               |

| 4-11  | Request Register Bit Assignments                            |

| 4-12  | Set Chaining Mode Register Bit Assignments                  |

| 4-13  | Set Chaining Mode Status Register Bit Assignments           |

| 4-14  | Status Register Bit Assignments                             |

| 4-15  | Stop Register I/O Port Addresses                            |

| 4-16  | NMI Register I/O Addresses                                  |

| 4-17  | Status and Control Register Bit Assignments                 |

| 4-18  | Enable/Disable and Real Time Clock Register Bit Assignments |

| 4-19  | Extended Status and Control Register Bit Assignments        |

| 4-20  | Software NMI Generation Register Bit Assignments            |

| 4-21  | Control Word Bit Assignments                                |

| 4-22  | ISP Signal Cross Reference                                  |

| 5-1   | Serial Communication Ports Address Map                      |

| 5-2   | Serial Communication Port Register Selection                |

| 5-3   | Interrupt Enable Register Bit Assignments                   |

| 5-4   | Interrupt Identification Register Bit Assignments           |

| 5-5   | FIFO Control Register Bit Assignments                       |

| 5-6   | Line Control Register Bit Assignments                       |

| 5-7   | Modem Control Register Bit Assignments                      |

| 5-8   | Line Status Register Bit Assignments                        |

| 5-9   | Modem Status Register Bit Assignments                       |

| 5-10  | Baud Rates Using 1.846MHz Clock                             |

| 5-11  | Parallel Port Register Address Map                          |

| 5-12 | Parallel Port Register Bit Assignments                | 5-11 |

|------|-------------------------------------------------------|------|

| 6-1  | DDC Register Address Map                              | 6-4  |

| 6-2  | Digital Output Register (DOR) Bit Assignments         | 6-5  |

| 6-3  | Tape Drive Register (TDR) Bit Assignments             | 6-5  |

| 6-4  | Main Status Register (MSR) Bit Assignments            | 6-6  |

| 6-5  | Data Select Rate (DSR) Register Bit Assignments       | 6-6  |

| 6-6  | Configuration Control Register (CCR) Bit Assignments  | 6-7  |

| 7-1  | Status Register Bit Definitions                       | 7-3  |

| 7-2  | Input Port Bit Assignments                            | 7-5  |

| 7-3  | Output Port Bit Assignments                           | 7-6  |

| 7-4  | Controller Comands                                    | 7-7  |

| 7-5  | Data Stream Bits                                      | 7-8  |

| 7-6  | Status Indicator Bits                                 | 7-9  |

| 7-7  | Typematic Rate/Delay Bit Definitions                  | 7-11 |

| 7-8  | Typematic Rate                                        | 7-12 |

| 7-9  | Scaling Input and Output Relationships                | 7-16 |

| 7-10 | Byte/Resolution Relationship                          | 7-17 |

| 7-11 | Format of Mouse Status Request Bytes                  | 7-18 |

| 7-12 | Mouse Sampling Rates                                  | 7-20 |

| 8-1  | CLASIC Address Decode Map                             | 8-6  |

| 8-2  | System Control Ports and Registers Address Map        | 8-9  |

| 8-3  | CLASIC Configuration Register Indexes                 | 8-10 |

| 8-4  | System Control Port A                                 | 8-12 |

| 8-5  | System Control Port B                                 | 8-13 |

| 8-6  | System Control Port C Bit Assignments                 | 8-14 |

| 8-7  | System Control Port D Bit Assignments                 | 8-15 |

| 8-8  | Feature Control A Register Bit Assignments            | 8-18 |

| 8.9  | Feature Control B Register Bit Assignments            | 8-19 |

| 8-10 | Serial Port 1 Register Bit Assignments                | 8-20 |

| 8-11 | Serial Port 2 Configuration Register Bit Assignments  | 8-21 |

| 8-12 | Parallel Port Register Bit Assignments                | 8-22 |

| 8-13 | Keyboard and Mouse Register Bit Assignments           | 8-23 |

| 8-14 | Diskette Register Bit Assignments                     | 8-24 |

| 8-15 | IDE Register Bit Assignments                          | 8-25 |

| 8-16 | General Purpose Peripheral 1 Register Bit Assignments | 8-26 |

| 8-17 | General Purpose Peripheral 2 Register Bit Assignments | 8-27 |

| 8-18 | Shadow Register Bit Assignments                       | 8-29 |

| 9.1  | MECA I/O Ports Address Man                            | 9-5  |

| 9-2   | MECA Configuration Register Indexes                         |

|-------|-------------------------------------------------------------|

| 9-3   | Memory Attribute Register Bit Assignments                   |

| 9-4   | Memory Attribute Programmability                            |

| 9-5   | Memory Range Lower Limit Register Bit Assignments           |

| 9-6   | Memory Range Upper Limit Register Bit Assignments           |

| 9.7   | BIOS Shadow Control Register Bit Assignments                |

| 9-8   | Memory Decode and Control Register Bit Assignments          |

| 9.9   | Memory Error Control Register                               |

| 9-10  | Memory Error Address LSB Register Bit Assignments           |

| 9-11  | Memory Error Address Middle Byte Register Bit Assignments   |

| 9-12  | Memory Error Address MSB Register Bit Assignments           |

| 9-13  | Memory Partition Diable Register Bit Assignments            |

| 9-14  | CPU Speed Register Bit Assignments                          |

| 9-15  | CPU Module ID Register Bit Assignments                      |

| 9-16  | Memory Partition Configuration Register Bit Assignments     |

| 9-17  | Memory Partition Boundary Register Bit Assignments          |

| 9-18  | General Control Register Bit Assignments                    |

| 11-1  | RTC Address Map                                             |

| 11-2  | Status Register A Bit Assignments                           |

| 11-3  | Status Register B Bit Assignments                           |

| 11-4  | Status Register C Bit Assignments                           |

| 11-5  | Status Register D Bit Assignments                           |

| 11-6  | Diagnostic Status Bit Assignments                           |

| 11-7  | Reason for Shutdown Bit Assignments                         |

| 11-8  | Type of Diskette Drive Bit Assignments                      |

| 11-9  | Type of Hard Disk Bit Assignments                           |

| 11-10 | Language Bit Assignments                                    |

| 11-11 | Installed Hardware Bit Assignments                          |

| 11-12 | Shadow Control Byte Bit Assignments                         |

| 11-13 | BIOS Options Bit Assignments                                |

| 11-14 | Manufacturer Option 1 Bit Assignments                       |

| 11-15 | Manufacturer Option 2 Bit Assignments                       |

| 11-16 | Manufacturer Option 3 Bit Assignments                       |

| 11-17 | Manufacturer Option 4 Bit Assignments                       |

| 11-18 | Manufacturer Option 5 Bit Assignments                       |

| 11-19 | Setup Information Bit Assignments                           |

| 11-20 | CPU Speed, Cache, and Extended CMOS Control Bit Assignments |

| 11-21 | Time-of-Day Registers Address Map                           |

| 11-41 | Time-of-Day Registers Address Map                           |

| A-1        | Computer Performance Specifications                              |

|------------|------------------------------------------------------------------|

| A-2        | Computer Dimensions                                              |

| A-3        | Computer Environmental Specifications                            |

| A-4        | Acoustics: Preliminary Declared Values per ISO 9296 and ISO 7779 |

| A-8        | Typical Current Requirements                                     |

| B-1        | Interrupt Functions and Types                                    |

| B-2        | Print Screen Service.                                            |

| B-3        | Equipment List Service.                                          |

| B-4        | Memory Size Service                                              |

| <b>B-5</b> | Diskette Service                                                 |

| B-6        | Hard Disk Service                                                |

| B-7        | Serial Communication Service                                     |

| B-8        | System Services                                                  |

| B-9        | Keyboard Service                                                 |

| B-10       | Parallel Printer Service                                         |

| B-11       | Time-of-Day Service                                              |

| C-1        | System Memory Map                                                |

| C-2        | I/O Address Map                                                  |

| C-3        | System Interrupt Levels                                          |

| C-4        | DMA Channel Assignment                                           |

| E-1        | System Board Jumper Settings                                     |

| F-1        | Contents of FLASH Memory Update Utility Diskette                 |

| F-2        | Recovery Procedure Beep Codes                                    |

| G-1        | CPU Module Features                                              |

| G-2        | DECpc 425ST CPU Module Specifications                            |

| G-3        | DECpc 433ST CPU Module Specifications                            |

| G-4        | DECpc 450ST CPU Module Specifications                            |

| G-5        | Intel486 DX2 50 MHz CPU Module Specifications                    |

| G-6        | Intel486 DX2 66 MHz CPU Module Specifications                    |

| G-7        | 25 MHz CPU Module Jumpers                                        |

| G-8        | 33 MHz CPU Module Jumper Settings                                |

| G-9        | Intel486 DX2 50 MHz and 66 MHz CPU Module Jumper Settings        |

# **About This Manual**

# **Purpose**

The purpose of this manual is to provide a comprehensive hardware description of the major components in a typical DECpc 400ST Series computer. Descriptions include:

- System architecture

- Buses

- Interfaces

- System specifications

- Basic input/output system (BIOS) specifications

- Configuration options

# **Audience**

This manual is written specifically for a system engineer or hardware designer familiar with the fundamental concepts of microprocessor based computers. The information in this manual assumes a familiarity with the general terminology used in the field of microprocessor and computer design. In addition, this manual contains information for engineers who design computer accessories and for programmers who require hardware and firmware specifications.

# **Organization of This Manual**

The following briefly describes the 11 chapters and six appendices found in this manual:

| Chapter 1 | <ul> <li>System Board Overview -</li> </ul> | <ul> <li>describes t</li> </ul> | the major features of the |

|-----------|---------------------------------------------|---------------------------------|---------------------------|

|-----------|---------------------------------------------|---------------------------------|---------------------------|

DECpc 400ST Series system board.

Chapter 2 CPU Module Technology — describes the technology used by

Intel486™ microprocessors and associated external caches.

Chapter 3 82358 EISA Bus Controller — describes the EISA bus

controller and provides a signal cross reference listing.

Chapter 4 82357 Integrated System Peripheral — describes the integrated

system peripheral and lists programming information about its

internal registers.

Chapter 5 WD16C552 or TL16C552 Asynchronous Communication

Element — provides programming information for the serial and parallel ports implemented by this integrated circuit.

Chapter 6 82077 Diskette Drive Controller — describes the diskette drive

controller and lists programming information about its internal

registers.

Chapter 7 8742 Keyboard and Mouse Controller — describes the

keyboard and mouse controller and lists programming

information about its internal registers.

Chapter 8 CLASIC — describes the Common Local I/O ASIC (CLASIC)

and lists programming information about its internal registers.

Chapter 9 MECA — describes the MEM Bus EISA Control ASIC

(MECA) and provides programming information about its

internal registers.

Chapter 10 DPP, EBB, and RCA — describes the data path parity (DPP)

and RAS CAS Address (RCA) ASICs. It also describes the

82352 EISA bus buffer (EBB).

Chapter 11 DS1287 Real-Time Clock — describes the real time clock and

lists programming information about its internal registers.

Appendix A Specifications — lists general specifications for the computer,

and environmental and dimensional specifications for the system box. It also includes system board jumper information.

Appendix B BIOS Interrupt Routines — describes the interrupt service

routines available in the system's BIOS.

Appendix C Device Mapping — provides tables that list the computer's

memory map, I/O address map, interrupt map, and DMA map.

Appendix D Configuring the Computer—describes how to use the system

configuration utility and its three advance features.

Appendix E System Board Jumpers—describes the system board jumpers.

Appendix F Updating the System BIOS—describes how to update the

system BIOS and how to recover the system BIOS if it becomes

corrupt during an update.

Appendix G CPU Modules—describe the CPU module features and jumper

positions.

Index — includes important terms arranged in alphabetical

order for quick reference.

## **Notational Conventions**

Notational conventions used throughout this manual include:

| * | In connector pinout listings, the asterisk (*) indicates an active |

|---|--------------------------------------------------------------------|

|   | low signal. For example, IOCHCK*                                   |

For example, 0F8h equals 0F8 (hexadecimal).

Kb A Kb suffix to a numerical value indicates size in kilobits. For

example, 512 Kb. A kilobit equals 1024 bits.

KB A KB suffix to a numerical value indicates size in kilobytes. For

example, 640 KB, 7168 KB, etc. A kilobyte equals 1024 bytes.

Mb A Mb suffix to a numerical value indicates size in megabits. For

example, 4 Mb. A megabit equals 1,048,576 bits.

MB An MB suffix to a numerical value indicates size in megabytes.

For example, 1 MB, 256 MB, etc. A megabyte equals 1,048,576

bytes.

GB A GB suffix to a numerical value indicates size in gigabytes. For

example, 1 GB, 256 GB, etc. A gigabyte equals 1,073,741,824

bytes.

An italicized word or phrase represents a variable or to lend emphasis in textual descriptions. Italic also specifies file names, path names, and directories.

# **Special Notices**

WARNING

Warnings indicate the presence of a hazard that can cause personal injury if the hazard is not avoided.

CAUTION

Cautions indicate the presence of a hazard that might cause damage to hardware or that might corrupt software.

NOTE

Notes provide important or explanatory information.

Three kinds of special notices emphasize specific information throughout this manual:

# **Related Documentation**

The following related documents are available as supplements to the information provided in this manual.

| Document                                                                                            | Part Number |

|-----------------------------------------------------------------------------------------------------|-------------|

| DECpc 400ST Series User's Guide (Multilingual)                                                      | ER-PCT15-UM |

| DECpc 400ST Series User's Guide (English)                                                           | ER-PCT15-UA |

| DECpc 400ST Series Installation Guide (Multilingual)                                                | ER-PCT15-IM |

| DECpc 400ST Series Installation Guide (English)                                                     | ER-PCT15-IA |

| DECpc 400ST Series Service Guide                                                                    | ER-PCT15-SV |

| DECpc 400ST Series 25 MHz, 33 MHz, 50 MHz CPU Upgrade Kit Installation Guide (Multilingual)         | ER-T16AA-IG |

| DECpc 400ST Series Intel486 DX2 50 MHz and 66 MHz CPU Upgrade Kit Installation Guide (Multilingual) | ER-T31AF IM |

| DECpc 400ST Series Intel486 DX2 50 MHz and 66 MHz CPU Upgrade Kit Installation Guide (English)      | ER-T31AA-IA |

# **System Board Overview**

## Introduction

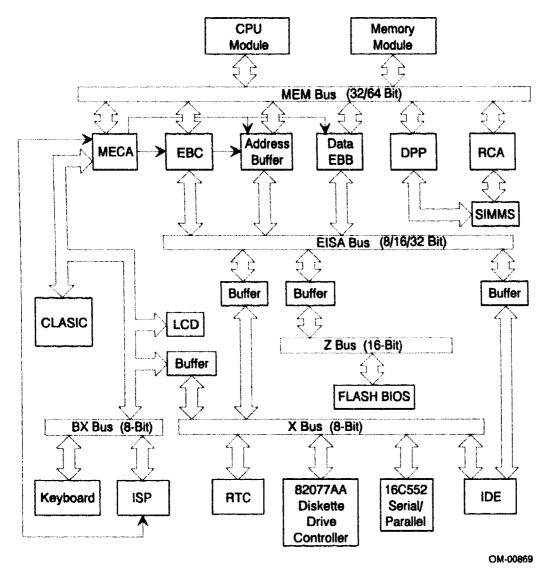

This chapter provides an overview of the DECpc 400ST Series system board (see Figure 1-1). The system board supports:

- High performance CPU modules that use Intel486 microprocessors (including external caches)

- Extended Industry Standard Architecture (EISA)

- Intel 82358 EISA Bus Controller (EBC)

- Intel 82357 Integrated System Peripheral (ISP)

- Intel CLASIC, MECA, DPP, and RCA Application Specific Integrated Circuits (ASICs)

- Intel 82352 EISA Bus Buffer

- Onboard 82077 diskette drive controller

- Integrated Disk Electronics (IDE) support

- Up to 64 MB (using 16 MB SIMMs) of onboard DRAM

- Up to 128 MB (using 16 MB SIMMs) of additional DRAM using an optional memory module

- Supports up to 384 MB of DRAM (using 32 MB SIMMs, when available)

#### **System Board Overview**

Figure 1-1. DECpc 400ST Series System Board Block Diagram

In addition, the system board supports:

- Six EISA bus master slots

- Two 9-pin serial ports

- One 25-pin parallel port

- 6-pin (mini-DIN) keyboard and 6-pin (mini-DIN) mouse connectors

- One 254 Watt power supply

- One CPU module connector

- One memory module connector

The remainder of this chapter provides descriptions of the system board, CPU module, and memory module. It also includes a brief memory description (including memory expansion board) and a brief description of the system board busses.

# **DECpc 400ST System Board Features**

The performance features of the system board include:

- Six Extended Industry Standard Architecture (EISA) master slots

- 82357 Integrated System Peripheral (ISP)

- 82358 EISA Bus Controller (EBC)

- Two programmable ASICs (CLASIC and MECA)

- Two non-programmable ASICs (DPP and RCA)

- IDE interface that supports two hard disk drives

- Diskette drive controller that supports two diskette drives

- Two RS-232C 9-pin serial communication ports

- One Centronics™ compatible 25-pin parallel port

- Keyboard and mouse controller

- One PS/2-style keyboard port

- One PS/2-style mouse port

- One piezo speaker

- Non-volatile storage in FLASH memory

- Phoenix Technologies<sup>™</sup> BIOS, based in FLASH memory

- CPU module connector

- Memory module connector

- Up to 64 MB of DRAM using 16 MB SIMMs

- EISA System Configuration Utility (SCU)

#### **EISA Slots**

The six EISA bus master slots provide for system expansion and performance enhancement. The EISA bus is an extension to the Industry Standard Architecture (ISA) bus. It extends the capability of the ISA bus while maintaining compatibility so ISA expansion boards also work. In addition, a bus snooping algorithm optimizes for maximum EISA bus performance, even when write-back cache mode CPU modules are in use. EISA bus clock speed is 8.33 MHz. The EISA bus provides:

- 32-bit memory addressing

- Type A transfers at 5.33 MB per second

- Type B transfers at 8.00 MB per second

- Burst transfers at 33 MB per second

- 8-bit, 16-bit, or 32-bit data transfers

- Automatic translation of bus cycles between EISA and ISA masters and slaves

- Interrupt sharing

# 82357 Integrated System Peripheral

The 82357 Integrated System Peripheral (ISP) integrates key EISA I/O commands by providing:

- 8237A-compatible Direct Memory Access (DMA) support

- 8254-compatible Programmable Interrupt Timers (PIT) support

- 8259-compatible Programmable Interrupt Controllers (PIC) support

## 82358DT EISA Bus Controller

The 82358DT EISA Bus Controller (EBC) monitors cycles initiated on either the EISA or MEMbus and provides control for the data buffers between the two buses.

## **Programmable ASIC Devices**

Four programmable application specific integrated circuit (ASIC) devices improve reliability and reduce system board costs. The MEM bus EISA control (MECA) ASIC controls optional EISA expansion boards. The common local I/O (CLASIC) ASIC controls local system board I/O. The RAS/CAS address (RCA) ASIC and data parity path (DPP) ASIC implement DRAM control logic.

#### **IDE Hard Drive Interface**

The IDE hard drive interface interfaces IDE hard disk drives with the Intel486 microprocessor. The interface supports up to two hard disk drives and can be disabled using the System Configuration Utility (SCU). When disabled, the IDE interface interrupt (IRQ 14) is available for other EISA expansion boards.

#### Diskette Drive Controller

A single 82077 diskette drive controller supports both double and high density media in 3 1/2-inch and 5 1/4-inch diskette drives. The diskette drive controller can be disabled with the System Configuration Utility (SCU). When disabled, the diskette controller interrupt (IRQ 6) is available for other EISA expansion boards. The diskette controller also supports fast floppy streaming tape; however, the system BIOS does not support this feature.

# **Asynchronous Communications Element (ACE)**

A single Western Digital<sup>™</sup> 16C552 or Texas Instruments<sup>™</sup> TL16C552 Asynchronous Communications Element (ACE) provides the interface for two serial ports and one parallel port.

#### **Serial Ports**

Each serial port uses a 9-pin D-sub connector and the ports can be configured as logical COM1, COM2, COM3 or COM4. The System Configuration Utility (SCU) enables and disables the serial ports. Each serial port can be separately disabled to allow any EISA bus resource access to its interrupt. The ports connect to the EISA bus with a 16-byte FIFO interface. This interface supports 16-bit software and provides baud rates of 300, 1200, 2400, 9600, 19200, 38400, and 56000 bytes per second. The system BIOS supports baud rates up to 9600 bytes per second. The higher baud rates can be used if the application driver does not use the system BIOS for serial port control. Tranzorbs protect the serial ports from surges caused by external electrical transients. RS-232C cable lengths should not exceed 50 feet (15.24 meters).

#### **Parallel Port**

The parallel port uses a 25-pin DB25 connector. The System Configuration Utility (SCU) enables, disables, or configures the parallel port. It also configures the parallel port as LPT1 or LPT2. It also can be set to either standard (Centronics compatible) or bidirectional (PS/2 compatible) using the BIOS setup utility. Disabling the parallel port allows any EISA bus resource access to its interrupts.

## **Keyboard and Mouse Controller**

A single 8742 Universal Peripheral Interface Microcontroller (also known as the keyboard and mouse controller) supports PS/2 compatible keyboards and the PS/2 style mouse. This microcontroller supports the following HOT key sequences:

#### Ctrl-Alt-Del

This key sequence does a software reset of the system by jumping to the beginning of the BIOS code and running the power-on self test (POST) operation (excluding the memory tests).

### System Board Overview

### Ctrl-Alt-1

### Ctrl-Alt-2

These two key sequences switch between slow and fast modes. Ctrl-Alt-1 selects slow mode that emulates an 8 MHz 80286 microprocessor by placing the CPU in hold for a period of time and disabling all caching circuitry. Ctrl-Alt-2 selects fast mode that enables full-speed operation of the Intel486 microprocessor and enables all cache memory logic at its full speed. The key sequences are valid only on the numeric keypad.

## PS/2 Keyboard Port and PS/2 Mouse Port

A PS/2 keyboard port and a PS/2 mouse port use a dual stacked 6-pin mini DIN connector. An Intel 8742 Universal Peripheral Interface Microcontroller that incorporates Phoenix Technologies keyboard controller firmware controls these ports. The PS/2 mouse port interrupt can be disabled using the SCU, allowing any EISA bus resource to use interrupt (IRQ 12).

## Speaker

The speaker provides audible tones under software control.

## **System BIOS**

System BIOS is from Phoenix Technologies. It is stored in two 32-pin 8-bit FLASH memories and can occupy up to 192 KB.

## Non-Volatile Memory

Non-volatile memory consists of 8 KB and located in the user area of FLASH memory. In addition, 50 bytes of CMOS are available in the real-time clock.

## **CMOS Battery Backup/Real-Time Clock**

The system board uses a Dallas Semiconductor™ DS1287 CMOS Real-time Clock. The DS1287 contains 64 bytes of general purpose RAM that stores system BIOS configuration information, clock registers, and general purpose control registers. The DS1287 provides an accuracy of ±1 minute per month. An integral lithium battery powers the clock for up to 10 years in the absence of power.

## **Direct Memory Access (DMA)**

The system board provides seven ISA-compatible DMA channels through the computer's EISA bus implementation. An EISA DMA controller also supports demand and block mode DMA transfers. These modes enable multiple continuous transfers and high speed bus cycles and can achieve data transfer rates up to 33 MB per second. You can program each DMA channel for 8, 16 or 32-bit DMA device size. Also, all channels support ISA compatible, Type A (5.33 MB per second), Type B (8 MB per second), or Burst DMA (33 MB per second) timing modes. The DMA memory mapper supports the full 4 GB memory range using up to a 16 MHz clock rate. When enabled, the onboard diskette drive controller and IDE hard disk interface use DMA channels 2 and 3, respectively.

## **System Memory**

System memory, located on the system board, consists of the RAS/CAS Address (RCA) ASIC and four SIMM sockets that support up to 64 MB of (70ns or 80ns) DRAM using 16 MB SIMMs. The RCA ASIC provides DRAM control functions RAS, CAS. WE, and address multiplexing addresses, and generates MEM bus response signals. Table 1-1 shows the system memory allocation.

The DECpc 400ST Series computers do not support use of the 000E 0000 to 000E FFFF address ranges for DEC EtherWORKS (DEPCA) controllers. DEC EtherWORKS controllers should be configured for the 000D 0000 to 000D FFFF address range to run in the 64 KB mode or for 00C 8000 to 00C FFFF to run in the 32 KB mode.

## **System Board Overview**

Table 1-1. System Memory Allocation

| Address Range          |                                            | 0:     | Ohada  | Casha |

|------------------------|--------------------------------------------|--------|--------|-------|

| <u>(In hex)</u>        | <u>Function</u>                            | Size   | Shadow | Cache |

| 0010 0000 to 01FF FFFF | Extended memory(1)                         | 192 MB | No     | Yes   |

| 000F 0000 to 000F FFFF | System BIOS                                | 64 KB  | Yes    | Yes   |

| 000E 8000 to 000E FFFF | EISA configuration 32 KB No information(2) |        | No     |       |

| 000E 0000 to 000E 7FFF | Adapter BIOS extension                     | 32 KB  | Yes(3) | Yes   |

| 000D 0000 to 000D FFFF | Adapter BIOS extension                     | 64 KB  | No     | No    |

| 000C 8000 to 000C FFFF | Adapter BIOS extension                     | 32 KB  | Yes(3) | Yes   |

| 000C 0000 to 000C 7FFF | Video BIOS or adapter<br>BIOS extension    | 32 KB  | Yes(3) | Yes   |

| 000A 0000 to 000B FFFF | Video RAM                                  | 128 KB | No     | No    |

| 0000 0000 to 0009 FFFF | Base memory                                | 640 KB | No     | Yes   |

<sup>(1)</sup> The SCU provides an option for creating a 1 MB open space between 15 MB and 16 MB to which you can map expansion board BIOS

<sup>(2)</sup> Not available for mapping expansion board memory or BIOS

<sup>(3)</sup> User configurable

### **Buses**

The system board supports five buses (see Figure 1-1):

- BX

- EISA

- MEM

- X

- Z

### **BX Bus**

The BX bus is an 8-bit bus that provides an interface among the keyboard, 82357 ISP, CLASIC, MECA ASIC, and LCD.

### **EISA Bus**

The EISA bus provides computer feature expansion by allowing installation of EISA or ISA expansion boards. The EISA slot connectors implement the Extended Industry Standard Architecture and maintain compatibility with the earlier Industry Standard Architecture (ISA).

### **MEM Bus**

The MEM bus is an Intel proprietary bus that connects the CPU module and optional memory module with the EISA bus.

### X Bus

The X bus is an 8-bit bus that provides the interface between DMA and non-memory non-DMA devices.

### Z Bus

The Z bus is a 16-bit bus that provides the interface between FLASH memory and the EISA bus.

## **System Configuration Utility**

The SCU is on language-specific diskettes and sets up and configures the computer using menu driven utilities. The installed hardware and the required level of computer security determines which part of the SCU to access. Access these computer functions with the SCU:

- Select a specific keyboard type

- Copy the System Configuration Diskette

- Learn about configuring the computer

- Set the computer date and time

- Configure the computer

- Maintain the System Configuration Diskette

- Access the password utility

### **CPU Module Features**