# DECpc 316SX

## **Technical Reference Manual**

Order Number ER-PC44Y-DD-001

#### December 1991

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation.

Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software, if any, described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license. No responsibility is assumed for the use or reliability of software or equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Restricted Rights: Use, duplication, or disclosure by the U.S. Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

Utility Files: Copyright © 1985-1991 Tandy Corporation. All Rights Reserved.

BIOS ROM: Copyright @ 1985-1990 Phoenix Software Associates Ltd. All Rights Reserved

QAPlus: Copyright @ 1990-1991 DiagSoft, Inc. All Rights Reserved

DECpc 316SX Technical Reference Manual

Copyright @ 1991 Tandy Corporation.

Licensed to Digital Equipment Corporation.

All Rights Reserved.

Any reproduction or copying in any form without the express written permission of Tandy Corporation and Digital Equipment Corporation is strictly prohibited.

Printed in U.S.A.

IBM, AT, PS/2, and Personal System/2 are registered trademarks of International Business Machines Corporation

Intel 386 and 386SX are registered trademarks of Intel Corporation

Microsoft, MS-DOS, and MS OS/2 are registered trademarks of Microsoft Corporation

SIMM is a registered trademark of Wang Laboratories

ST-506 is a registered trademark of Seagate Technologies

Hercules is a trademark of Hercules Computer Technology.

QAPlus is a trademark of DiagSoft, Inc.

The following are trademarks of Digital Equipment Corporation:

DEC DECSYSTEM-20 **RSTS** DEC/CMS DECUS RSX DEC/MMS **DECwriter UNIBUS DECnet** DIBOL VAX DECpc EduSystem **VAXcluster** DECstation **MASSBUS VMS** DECsyste 1-10 PDP VT

## **Contents**

| introduction About This Manual Conventions                                                                                                                                                                                                          |                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Specifications and Features System Specifications Device and Component Specifications                                                                                                                                                               | <b>5</b><br>5<br>8         |

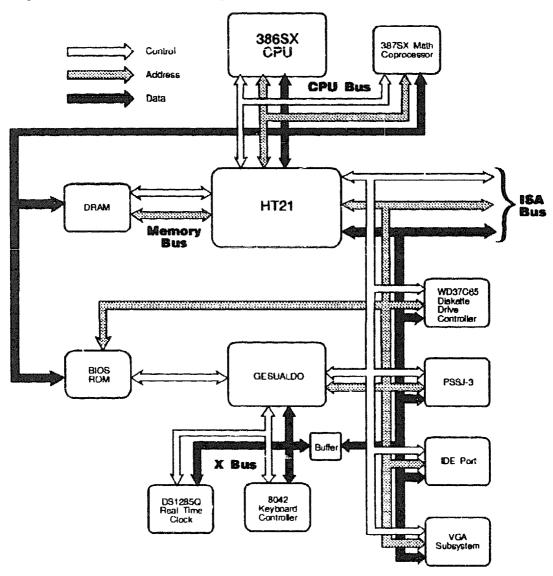

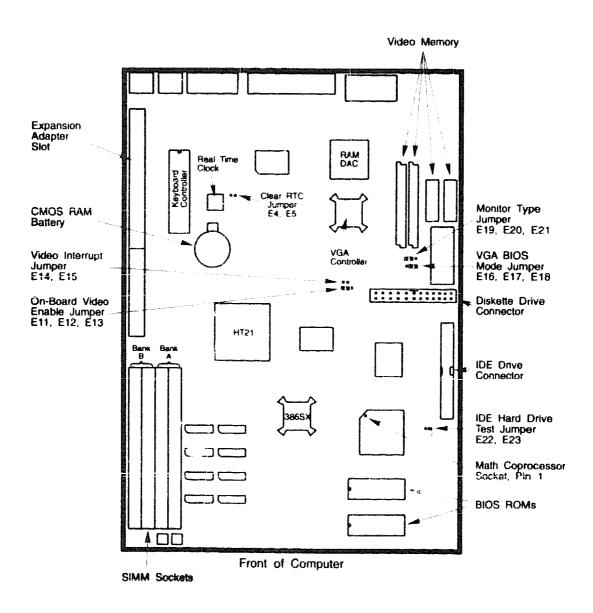

| Theory of Operation System Memory Map System I/O Map Direct Memory Access (DMA) IRQ Assignments System Block Diagram Components on the Main Logic Board                                                                                             | 16<br>17<br>18<br>19       |

| System Configuration Jumper Settings Main Logic Board Layout Programmable configuration settings Memory Configurations Supported Hardware Peripherals Internal Connector Pin Assignments External Connector Pin Assignments Power Supply Connectors | 35<br>36<br>37<br>39<br>39 |

| Device Programming 386SX Microprocessor                                                                                                                                                                                                             | 71<br>78<br>79<br>84       |

| BIOS Services                                         | 97  |

|-------------------------------------------------------|-----|

| Software Interrupt Summary                            | 98  |

| Interrupt 10h: Video Display Functions                |     |

| Interrupt 11h: Equipment Functions                    |     |

| Interrupt 12h: Memory Size Functions                  | 125 |

| Interrupt 13h: Diskette Drive I/O Support Functions   | 126 |

| Interrupt 1Eh: Diskette Drive Parameter Functions     |     |

| Interrupt 13h: Hard Disk I/O Support                  |     |

| Interrupts 41h and 46h: Hard Disk Parameter Functions | 140 |

| Interrupt 14h: Serial Communications Functions        |     |

| Interrupt 15h: System Support Functions               |     |

| Interrupt 16h: Keyboard Functions                     |     |

| Interrupt 17h: Line Printer Functions                 |     |

| Interrupt 1Ah: System Clock Functions                 |     |

| Keyboard                                              | 163 |

# Introduction

| About This Manual          | 1 |

|----------------------------|---|

| Conventions                | 2 |

| Abbreviations and Acronyms | 2 |

| Standard Prefixes          | 3 |

| Special Notations          |   |

| Special Print Styles       |   |

## Introduction

This manual is written for software developers, systems integrators and others who require technical knowledge of the DECpc 316SX computer system. The manual is not intended as a tutorial or tool for teaching microcomputer architecture.

The following documents provide more detailed information about the standard components used in the DECpc 316SX computer system:

Intel 386SX Data Book

Headland HT21 Data Book

Intel 8042 Microcontroller Data Sheet

Western Digital WD37C65 Diskette Controller Data Sheet

Dallas Semiconductor DS1285Q Real-time Clock Data Sheet

Western Digital WD90C00 VGA Controller Data Sheet

We recommend you have these documents readily available when you use this manual.

#### **About This Manual**

The purpose of this manual is to provide technical information about the hardware architecture and device programming of the DECpc 316SX. The manual is divided into the following sections:

**Introduction** Describes the purpose of the

manual and notational conventions

used.

Specifications and Features Provides a basic technical

description of the system

equipment.

Theory of Operation Describes the individual

components of the system and their

interaction.

System Configuration Lists the default configuration

settings. Describes modification of

the standard configuration.

**Device Programming** Describes the registers and

programming of all programmable

components in the system.

BIOS Services Provides a detailed listing of BIOS

services and error messages available to programmers.

#### **Conventions**

This section describes the notations, abbreviations, and special print styles used in this manual.

## **Abbreviations and Acronyms**

A variety of abbreviations and acronyms are used throughout this manual. They are listed here for convenient reference.

| Abbreviation or Acronym                      | Full Meaning                                                                                                                                                                                                                         |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A b B BCD Btu BPI Hz IDE in. ISA SCSI SIMM V | Amperes (amps) bit(s) byte(s) Binary Coded Decimal British Thermal Unit Bits per Inch Hertz Integrated Drive Electronics inch(es) Industry Standard Architecture Small Computer Systems Interface Single In-line Memory Module Volts |

Abbreviations and Acronyms

#### **Standard Prefixes**

This manual uses standard prefixes to indicate multiples of fundamental units. The standard prefixes are listed in the following table:

| Prefix                | Symbol | Multiple                                              |  |

|-----------------------|--------|-------------------------------------------------------|--|

| Tera- (binary sense)  | Т      | 2 <sup>64</sup><br>10 <sup>9</sup>                    |  |

| giga-                 | G      | 109                                                   |  |

| mega- (aecimal sense) | M      | 10 <sup>6</sup>                                       |  |

| Mega- (binary sense)  | M      | <sub>2</sub> 20                                       |  |

| kilo- (decimal sense) | k      | 10 <sup>6</sup><br>2 <sup>20</sup><br>10 <sup>3</sup> |  |

| Kilo- (binary sense)  | K      | 2 <sup>10</sup>                                       |  |

| centi-                | С      | 10 <sup>-2</sup>                                      |  |

| milli-                | m      | 10-3                                                  |  |

| micro-                | $\mu$  | 10 <sup>-6</sup>                                      |  |

| nano-                 | n      | 10 <sup>-9</sup>                                      |  |

Standard Prefixes

#### **Special Notations**

Signal names are specified in uppercase letters, such as HIGH. A signal name followed by a minus sign, as in LOW-, indicates an active low signal. A signal name without a minus sign indicates an active high signal.

#### **Special Print Styles**

The following print styles are used to differentiate various types of information:

- Words that are printed in small bold capital letters represent keys on your keyboard. For example: ENTER.

- Groups of keys are printed like this: ctrl+alt+bel. Press and hold the keys (ctrl, alt, and bel in this example) in the order shown.

- Information that you should type or that is shown on the screen is printed as in the following example:

Type 3 at the Select the Desired Action prompt.

PAGE 4 IS A BLANK PAGE

# **Specifications and Features**

| System Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Configuration Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5  |

| Available System Upgrades                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6  |

| Physical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| Environmental Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7  |

| Operational Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| oporational orial action of the second of th |    |

| Device and Component Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8  |

| Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8  |

| System Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8  |

| BIOS ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9  |

| Expansion Slots                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| Diskette Drive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| Output Voltages and Currents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| Keyboard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| Battery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10 |

| DMA Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| Interrupt Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| Video Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12 |

| Video Sync Frequencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

## **Specifications and Features**

This section lists the major subassemblies and components in the DECpc 316SX and provides detailed specifications for most subassemblies and components.

## **System Specifications**

This section includes a summary of the standard configuration of the DECpc 316SX. Refer to "Device and Component Specifications" for detailed specifications of each component listed.

This section also summarizes the physical and electrical characteristics of the system unit and defines the environmental requirements for safe operation.

## **Configuration Overview**

The following devices and components are included in the standard configuration of the DECpc 316SX.

Devices in standard configuration

- 386SX microprocessor

- 1MB DRAM (80 ns)

- 1.44MB 3½-inch diskette drive

- 100-watt power supply

- 101-key enhanced keyboard

- Built-in diskette drive controller and IDE Drive interface

- Built-in 16-bit Super VGA graphics

**Expansion support**

- Three ISA 16/8-bit expansion slots

- Four SIMM sockets for system memory expansion

- Two 3½-inch drive bays and one 5¼-inch drive bay

- 387SX math coprocessor socket

Self-test diagnostic procedures

ROM-based; perform memory tests and verify operation on power-up and after reset

Clock speeds

**CPU**

16 or 8 MHz, software selectable

Expansion bus

8 MHz

I/O ports

Centronics-compatible parallel port

RS-232 serial port

PS/2-style keyboard port

PS/2-style mouse port

#### **Available System Upgrades**

The following lists describe some of the internal options and examples of external options that are available for the DECpc 316SX.

Internal options supported

- SIMM memory upgrades

- 31/2- and 51/4-inch storage including diskette drives, IDE hard disk drives, and tape cartridge systems

- 387SX (16 MHz) math coprocessor

- Network adapters

External options supported

- **Printers**

- Modems

- PS/2-style serial mouse

## **Physical Specifications**

Dimensions of system unit Depth: 38.2 cm (15 in.)

Width: 39.4 cm (15½ in.) Height: 10.7 cm (41/4 in.)

Weight

Total system unit, keyboard, power cord, manual, and

packing material

10.4 kg (23 lbs.)

System unit only with one

1.44MB, 31/2-inch diskette drive

6.6 kg (14.5 lbs.)

## **Electrical Specifications**

Power output (maximum) 100 Watts continuous

138.5 Watts peak

Input surge current 50 A peak

| Input Voltage |                | Fre     | quency      |

|---------------|----------------|---------|-------------|

| Nominal       | Range          | Nominal | Range       |

| 120 VAC       | 90 to 135 VAC  | 60 Hz   | 47 to 63 Hz |

| 230 VAC       | 190 to 264 VAC | 50 Hz   | 47 to 63 Hz |

#### **Environmental Requirements**

Acceptable temperature range

Operating: 10°C to 35°C (50°F to 95°F) Storage: -40°C to 66°C (-40°F to 150°F)

**Humidity tolerance**

Operating: 20% to 80% (non-condensing) Storage: 10% to 90% (non-condensing)

## **Operational Characteristics**

Heat output 297.3 Btu/hr, typical

Workspace clearance requirements 12 inches top, back, and sides

Valid operating positions upright on bottom

Industry certification UL, CSA, FCC Class B, VDE Class B

## **Device and Component Specifications**

This section provides physical, electrical and operational specifications for most devices and components in the standard configuration.

#### **Processor**

Processor type Intel 386SX, 16 MHz

Data types supported Bit, byte, word, doubleword

Registers 34 base architecture registers

Address space 16MB physical address space

64 Terabytes (64 x 2<sup>64</sup> bytes) virtual

address space

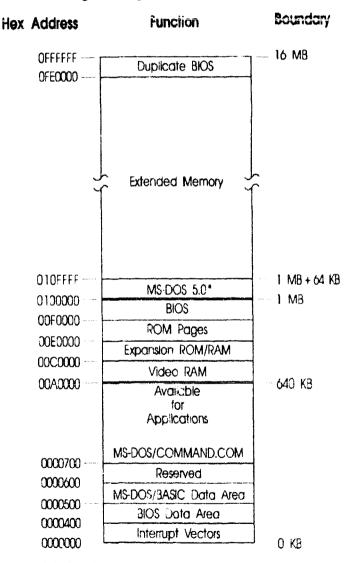

## System Memory

Standard configuration 1MB

Memory type Eight 256KB X 4 DRAMs (SOJ

package) plus four 256 X 1 parity DRAMs on main logic board 256KB X 9 or 1MB X 9 DRAMs (SIMM package) in memory

expansion sockets

Memory speed 80 ns (or faster)

Memory upgrade support Expandable to 5MB on system

board

Memory organization Page mode, two- or four-way

interleave

Local bus type 16 dedicated data lines

24-bit address bus

**BIOS ROM**

Source Phoenix

Version 1.10

**Expansion Slots**

Type Three 98-pin 16/8-bit ISA slots

**Diskette Drive**

Model SONY MP-F17W-04, or equivalent

95 ms

Recording method MFM

Capacity 1.44MB formatted

Average access time (including settling time)

Transfer rate 500K bits per second

Mean Time Between Failure 30,000 power-on hours

## **Power Supply**

Power output (maximum) 100 Watts continuous

138.5 Watts peak

Input voltage

Nominal 120/230 VAC

Range 90-135 VAC at 60 Hz 190-264 VAC at 50 Hz

Frequency Range 47–63 Hz

## **Output Voltages and Currents**

| Voltage           | Itage Ripple/Noise Voltage<br>400 Hz or less |                   |  |  |  |

|-------------------|----------------------------------------------|-------------------|--|--|--|

| +12 VDC (± 5%)    | 50 mV p-p                                    | 0.15 A to 1.53 A* |  |  |  |

| + 5 VDC (+5%/-4%) | 100 mV p-p                                   | 1.25 A to 9.0 A   |  |  |  |

| -12 VDC (± 10%)   | 150 mV p-p                                   | 0 A to 0.3 A      |  |  |  |

<sup>\*</sup> The +12 VDC line will have a constant current load of 2.75 A for 5 seconds at startup.

## Keyboard

Model (US 101-key) DEC PCXAL-AA

Power requirements +5 VDC ±10%, 300 mA max.

**Battery**

Model CR2032 (lithium) or equivalent

Life expectancy 5 years

Voltage rating 3 Volts DC

**DMA Controller**

HT21 internal, equivalent to 2 X Intel Model

8237A-5 cascaded

7 Number of channels

**Interrupt Controller**

HT21 internal, equivalent to 2 X Intel Model

8259 cascaded

Number of interrupt levels 15

**Ports**

Parallel Centronics-compatible

Serial Standard RS-232

Data length: 5-, 6-, 7-, and 8-bits

Stop bits: 1, 11/2, or 2 Parity: odd, even, or none Transmission rates: 50 to 56,000

**UART: 16451 equivalent**

## **Video Support**

All models are factory equipped with a standard VGA adapter with 512KB video memory built in to the main logic board. With an appropriate monitor, the DECpc 316SX can support Super VGA modes, including 132-column text, 800 x 600 graphics, and 1024 x 768 interlaced graphics. The following tables describe the various video modes.

| Notes             | 0m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Monitor           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Char.<br>Size     | 90000000000000000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |