# VAX 6000 Model 500 System Technical User's Guide

Order Number: EK-650EA-TM-001

This manual serves as a reference on how to write software to this machine and covers the information needed to do field-level repair or programming customized to the CPU. It includes information on interrupts, error handling, and detailed theory of operation.

#### First Printing, June 1991

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation.

Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software, if any, described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license. No responsibility is assumed for the use or reliability of software or equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Copyright @1991 by Digital Equipment Corporation

All Rights Reserved. Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation:

DEMNA PDP VAXcluster

DEC ULTRIX VAXELN

DEC LANcontroller UNIBUS VMS

DECnet VAX XMI

DECUS VAXBI diiqii [ 3]

FCC NOTICE: The equipment described in this manual generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. Operation of this equipment in a residential area may cause interference, in which case the user at his own expense may be required to take measures to correct the interference.

#### Contents PREFACE xvII CHAPTER 1 THE VAX 6000 MODEL 500 SYSTEM 1-1 SYSTEM ARCHITECTURE 1.1 1-2 1.2 **SAMPLE SYSTEM** 1-4 1.3 SYSTEM FRONT VIEW 1-6 1.4 SYSTEM REAR VIEW 1-8 1-10 1.5 SUPPORTED ADAPTERS CHAPTER 2 KA65A CPU MODULE 2-1 2.1 **OVERVIEW** 2-2 2.2 **BLOCK DIAGRAM DESCRIPTION** 2-4 2.2.1 CPU and Floating-Point Accelerator \_\_\_\_\_ 2-4 2.2.2 MC-Chip and Backup Cache 2-5 2.2.3 System Support Chip \_\_\_\_\_ 2-5 2.2.4 XMI Interface 2-5 2.3 **CPU SECTION** 2-6 2.3.1 Data Types \_\_\_\_\_\_ 2-6 2.3.2 Instruction Set 2-7 2.3.3 Memory Management \_ 2-8 2.3.3.1 Translation Buffer • 2-8 2.3.3.2 Memory Management Control Registers • 2-9 2.3.4 Exceptions and Interrupts \_ 2-11 2.3.4.1 interrupts • 2-12 2.3.4.2 Exceptions • 2-14 2.3.4.3 Unique Exceptions • 2-15 2.3.4.4 Console Halt • 2-23

|     | 2.3.5 System Control Block |              |                                                  | _ 2–25       |  |

|-----|----------------------------|--------------|--------------------------------------------------|--------------|--|

|     | 2.3.6                      | Process :    | Structure                                        | _ 2-27       |  |

|     | 2.3.7                      | Primary (    | Cache                                            | _ 2-27       |  |

|     | 2.3.8                      | Floating-    | Point Accelerator                                | _ 2-29       |  |

| 2.4 | CACHE                      | E MEMORY     |                                                  | 2–31         |  |

|     | 2.4.1                      | Writebac     | k Cache                                          | _ 2-32       |  |

|     | 2.4.2                      | Cache Co     | oherency                                         | 2–33         |  |

|     | 2.4.3                      |              | Cache                                            |              |  |

|     | 2.4.4                      | _ 2-37       |                                                  |              |  |

|     |                            | 2.4.4.1      | CacheBackup Cache RAM Addressing • 2-38          |              |  |

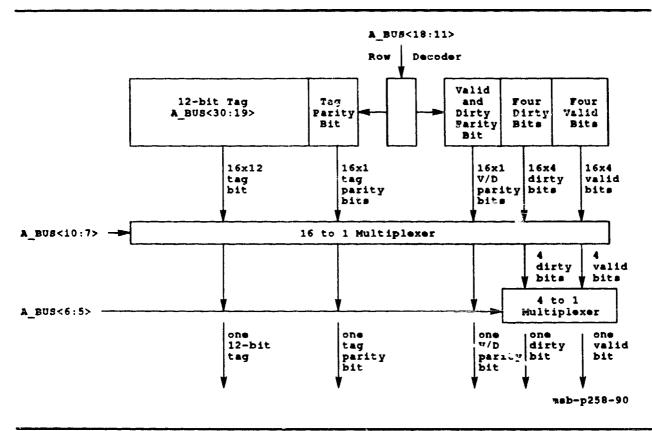

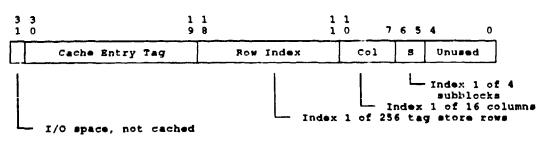

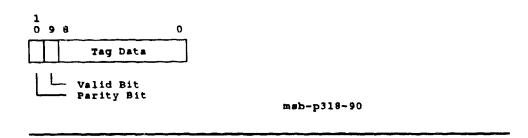

|     |                            | 2.4.4.2      | Backup Cache Tag Store Organization • 2-39       |              |  |

|     |                            | 2.4.4.3      | Backup Cache Internal Processor Registers • 2-3  |              |  |

|     |                            | 2.4.4.4      | Backup Cache Tag Store Block Diagram Descripti   | on • 2–40    |  |

|     |                            | 2.4.4.5      | Using Backup Cache Registers 2-41                |              |  |

| 2.5 | SYSTE                      | M SUPPOR     | RT CHIP                                          | 2-43         |  |

|     | 2.5.1                      | Console      | Serial Line                                      | 2-44         |  |

|     |                            | 2.5.1.1      | Console Serial Line Connections • 2-44           |              |  |

|     |                            | 2.5.1.2      | CTRL/P Detection • 2-44                          |              |  |

|     |                            | 2.5.1.3      |                                                  |              |  |

|     |                            | 2.5.1.4      | Console Serial Line Interrupt Levels and Vectors | 2-45         |  |

|     | 2.5.2                      | Time-of-     | Year Clock and Timers                            | 2–45         |  |

| 2.6 | XMI IN                     | ITERFACE     |                                                  | 2–46         |  |

|     | 2.6.1                      | KA65A        | (MI Private I/O Address Space Map and            |              |  |

|     |                            | Transactions |                                                  |              |  |

|     | 2.6.2                      |              | es                                               |              |  |

|     | 2.6.3                      | Writebac     | k Queue                                          | 2-51         |  |

|     | 2.6.4                      |              | Avoidance                                        |              |  |

|     | 2.6.5                      | _            |                                                  |              |  |

|     | 2.0.0                      |              | Device Interrupts (INTRs) • 2-52                 |              |  |

|     |                            | 2.6.5.2      | Implied Vector Interrupts (IVINTRs) • 2–52       |              |  |

|     |                            | 2.6.5.3      | Read Interrupt Vector and IDENT • 2-52           |              |  |

|     | 2.6.6                      |              | isters                                           | 2-53         |  |

| 2.7 | SCA!                       | ADMECTO      | R INTERACTION                                    | 2-55         |  |

| £.1 | •                          |              |                                                  | 2-55<br>2-56 |  |

|     | 2.7.1                      |              | nstruction Execution                             |              |  |

|     | <b>2.7.2</b>               | ≥xceptic     | ons and Errors                                   | 2-57         |  |

| 2.8 | KA65A | CPU MODULE REGISTERS                                |       | 2-58  |

|-----|-------|-----------------------------------------------------|-------|-------|

|     | 2.8.1 | Internal Processor Registers                        |       | 2-58  |

|     |       | INTERVAL CLOCK CONTROL AND STATUS                   | 0.60  |       |

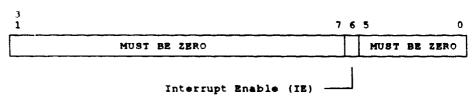

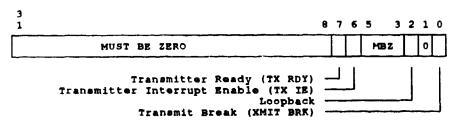

|     |       | REGISTER (ICCS) CONSOLE RECEIVER CONTROL AND STATUS | 2-63  |       |

|     |       | REGISTER (RXCS)                                     | 2-64  |       |

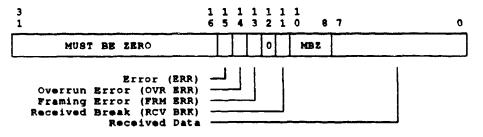

|     |       | CONSOLE RECEIVER DATA BUFFER REGISTER               | 2 04  |       |

|     |       | (RXDB)                                              | 2~66  |       |

|     |       | CONSOLE TRANSMITTER CONTROL AND STATUS              |       |       |

|     |       | REGISTER (TXCS)                                     | 2-68  |       |

|     |       | CONSOLE TRANSMITTER DATA BUFFER REGISTER            |       |       |

|     |       | (TXDB)                                              | 2-70  |       |

|     |       | MACHINE CHECK ERROR SUMMARY REGISTER                |       |       |

|     |       | (MCESR)                                             | 2–71  |       |

|     |       | ACCELERATOR CONTROL AND STATUS REGISTER             | 2-72  |       |

|     |       | (ACCS) CONSOLE SAVED PROGRAM COUNTER REGISTER       | 2-12  |       |

|     |       | (SAVPC)                                             | 2-74  |       |

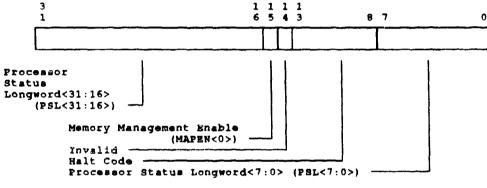

|     |       | CONSOLE SAVED PROCESSOR STATUS                      | •     |       |

|     |       | LONGWORD (SAVPSL)                                   | 2-75  |       |

|     |       | TRANSLATION BUFFER TAG REGISTER (TBTAG)             | 2-77  |       |

|     |       | I/O RESET REGISTER (IORESET)                        | 2-78  |       |

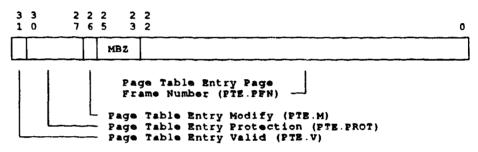

|     |       | TRANSLATION BUFFER DATA REGISTER (TBDATA)           | 2-79  |       |

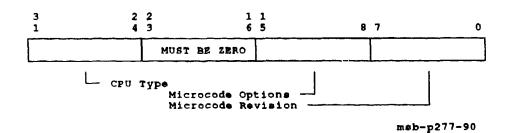

|     |       | SYSTEM IDENTIFICATION REGISTER (SID)                | 2-81  |       |

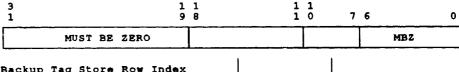

|     |       | BACKUP CACHE INDEX REGISTER (BCIDX)                 | 2-83  |       |

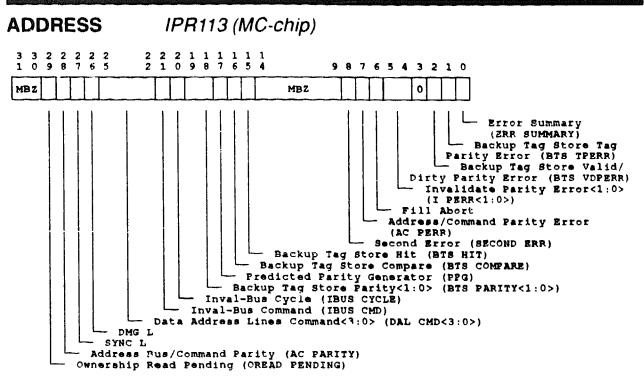

|     |       | BACKUP CACHE STATUS REGISTER (BCSTS)                | 2-84  |       |

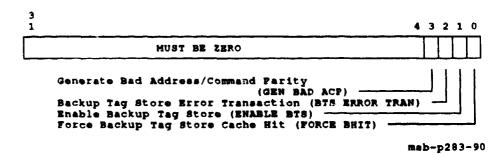

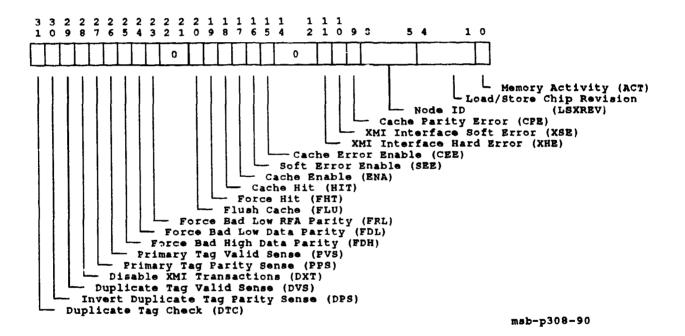

|     |       | BACKUP CACHE CONTROL REGISTER (BCCTL)               | 2–91  |       |

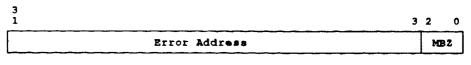

|     |       | BACKUP CACHE ERROR ADDRESS REGISTER                 |       |       |

|     |       | (BCERA)                                             | 2-94  |       |

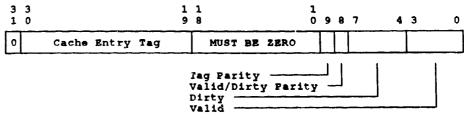

|     |       | BACKUP CACHE TAG STORE REGISTER (BCBTS)             | 2-95  |       |

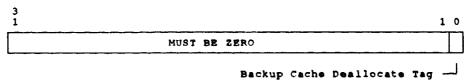

|     |       | BACKUP CACHE DEALLOCATE TAG REGISTER                | 2-98  |       |

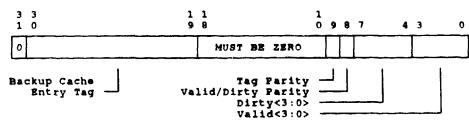

|     |       | (BCDET) BACKUP CACHE ERROR TAG REGISTER (BCERT)     | 2-99  |       |

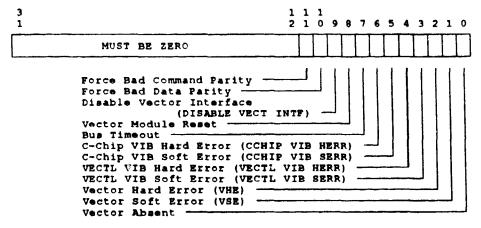

|     |       | VECTOR INTERFACE ERROR STATUS REGISTER              | 2-00  |       |

|     |       | (VINTSR)                                            | 2-101 |       |

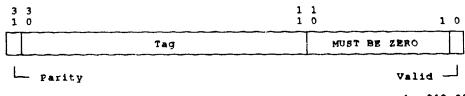

|     |       | PRIMARY CACHE TAG ARRAY REGISTER (PCTAG)            | 2-109 |       |

|     |       | PRIMARY CACHE INDEX REGISTER (PCIDX)                | 2-110 |       |

|     |       | PRIMARY CACHE ERROR ADDRESS REGISTER                |       |       |

|     |       | (PCERR)                                             | 2-111 |       |

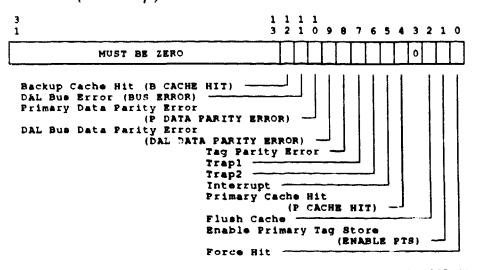

|     |       | PRIMARY CACHE STATUS REGISTER (PCSTS)               | 2-112 |       |

|     | 2.8.2 | XMI Registers                                       |       | 2-117 |

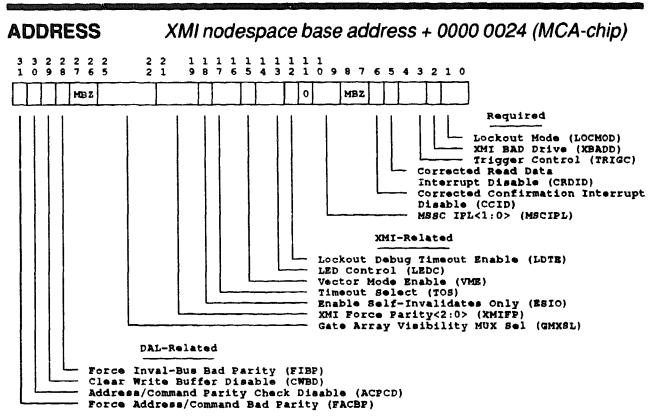

|     |       | CONTROL REGISTER 0 (CREGO)                          | 2-119 |       |

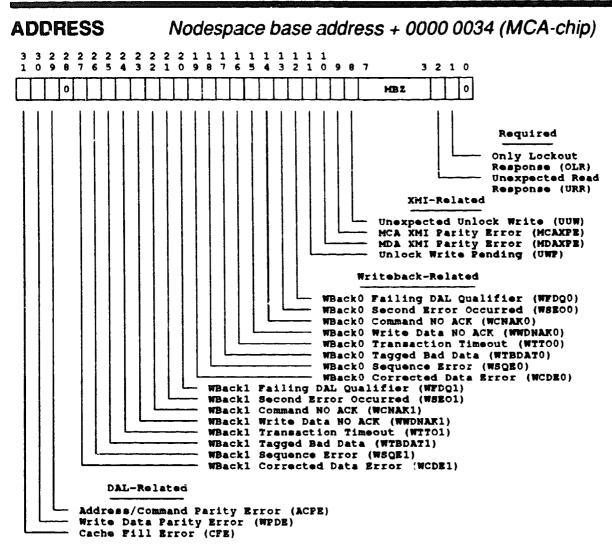

|     |       | CONTROL REGISTER 1 (CREG1)                          | 2-122 |       |

|     |       | CONTROL REGISTER WRITE ENABLE REGISTER              |       |       |

|     |       | (CREGWE)                                            | 2-123 |       |

|     |       | MSSC BASE ADDRESS REGISTER (SSCBAR)                 | 2-124 |       |

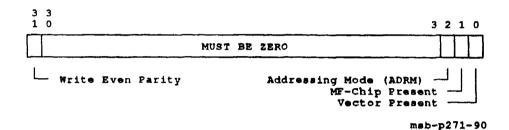

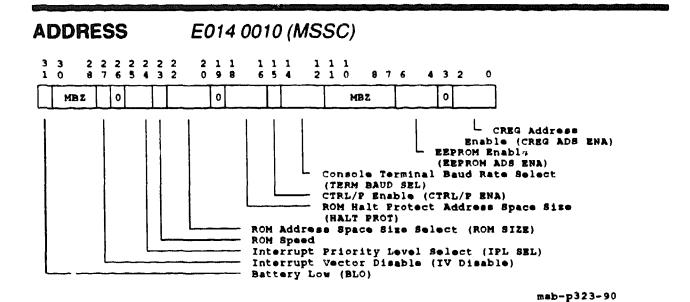

|     |       | MSSC CONFIGURATION REGISTER (SSCCNR)                | 2-125 |       |

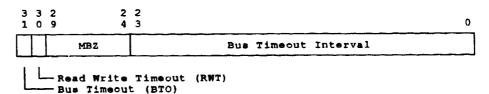

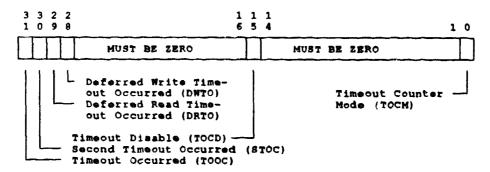

|     |       | MSSC BUS TIMEOUT CONTROL REGISTER                   |       |       |

|     |       | (SSCBTR)                                            | 2–131 |       |

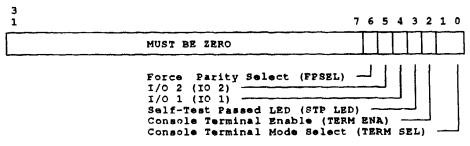

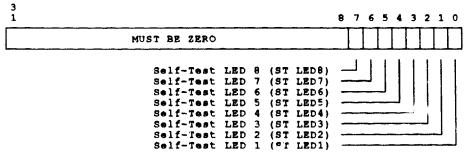

|     |       | MSSC OUTPUT PORT REGISTER (OPORT)                   | 2-133 |       |

|     |       | MSSC INPUT PORT REGISTER (IPORT)                    | 2–135 |       |

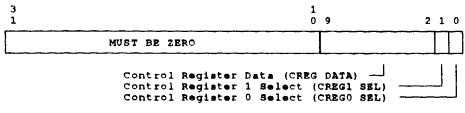

|     |       | CONTROL REGISTER BASE ADDRESS REGISTER              | 0 407 |       |

|     |       | (CRBADR)                                            | 2–137 |       |

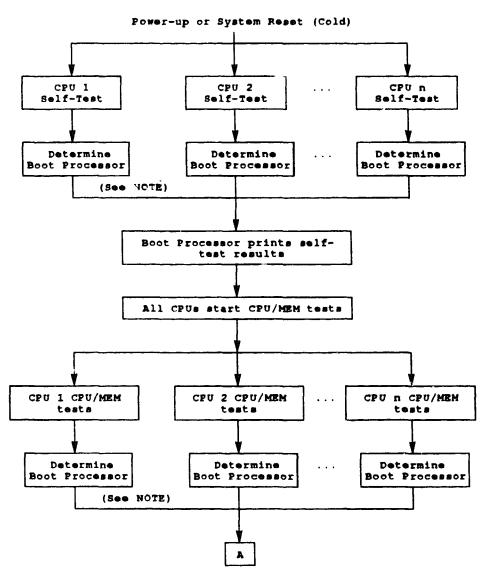

|             |       | 2.9.2.1<br>2.9.2.2<br>2.9.2.3<br>2.9.2.4<br>2.9.2.5<br>2.9.2.6<br>2.9.2.6.1<br>2.9.2.6.2<br>2.9.2.7 | Initialization State Summary • 2–200 Power-Up Initialization • 2–201 Warm Start Initialization • 2–203 Node Reset • 2–203 Boot Processor Determination • 2–204 Memory Configuration • 2–204 Selection of Interleave • 2–204 Memory Testing and the Bitmap • 2–205 DWMBB Configuration • 2–206 |                |                |

|-------------|-------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|

|             | 2.9.2 |                                                                                                     | nitialization Description                                                                                                                                                                                                                                                                     |                | 2–197          |

| <b>5.</b> 4 | 2.9.1 |                                                                                                     | on Overview                                                                                                                                                                                                                                                                                   |                | 2-195<br>2-195 |

| 2.9         | KASSA | CPU MODI                                                                                            | JLE INITIALIZATION, SELF-TEST, AND BO                                                                                                                                                                                                                                                         | OOTING         | 2_105          |

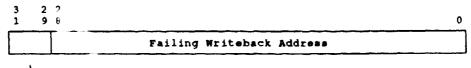

|             |       | (WFADR1)                                                                                            |                                                                                                                                                                                                                                                                                               | 2–194          |                |

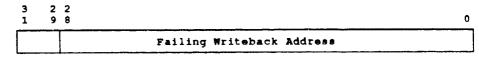

|             |       | (WFADRO)<br>WRITEBAC                                                                                | K 1 FAILING ADDRESS REGISTER                                                                                                                                                                                                                                                                  | 2–193          |                |

|             |       |                                                                                                     | CK O FAILING ADDRESS REGISTER                                                                                                                                                                                                                                                                 |                |                |

|             |       | BUS ERRO                                                                                            | PR EXTENSION REGISTER (XBEER)                                                                                                                                                                                                                                                                 | 2-186          |                |

|             |       |                                                                                                     | DDRESS EXTENSION REGISTER (XFAER)                                                                                                                                                                                                                                                             |                |                |

|             |       | •                                                                                                   | ROL REGISTER (XCR)                                                                                                                                                                                                                                                                            | 2-178          |                |

|             |       | NODE-SPE<br>(NSCSR)                                                                                 | CIFIC CONTROL AND STATUS REGISTER                                                                                                                                                                                                                                                             | 2-176          |                |

|             |       | XMI GENEI                                                                                           | RAL PURPOSE REGISTER (XGPR)                                                                                                                                                                                                                                                                   | 2-175          |                |

|             |       | FAILING A                                                                                           | DDRESS REGISTER (XFADR)                                                                                                                                                                                                                                                                       | 2-171          |                |

|             |       |                                                                                                     | PR REGISTER (XBER)                                                                                                                                                                                                                                                                            | 2-164          |                |

|             |       |                                                                                                     | EGISTER (XDEV)                                                                                                                                                                                                                                                                                | 2-162<br>2-163 |                |

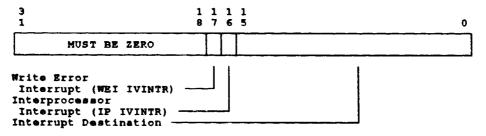

|             |       |                                                                                                     | ROR IMPLIED VECTOR INTERRUPT<br>ON REGISTER (WEIVINTR)                                                                                                                                                                                                                                        | 2-162          |                |

|             |       |                                                                                                     | ON REGISTER (IPIVINTR)                                                                                                                                                                                                                                                                        | 2–161          |                |

|             |       |                                                                                                     | CESSOR IMPLIED VECTOR INTERRUPT                                                                                                                                                                                                                                                               |                |                |

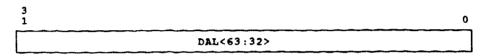

|             |       | FAILING DA                                                                                          | AL REGISTER 3 (FDAL3)                                                                                                                                                                                                                                                                         | 2-160          |                |

|             |       | FAILING DA                                                                                          | ERRUPT VECTOR REGISTER 1 (TIVR1) COUNTER REGISTER (SSCICR) NOSTIC REGISTER (DCSR) RL REGISTER 0 (FDAL0) AL REGISTER 1 (FDAL1) AL REGISTER 2 (FDAL2)                                                                                                                                           | 2-159          |                |

|             |       | FAILING DA                                                                                          | AL REGISTER O (FOALO)                                                                                                                                                                                                                                                                         | 2-157<br>2-158 |                |

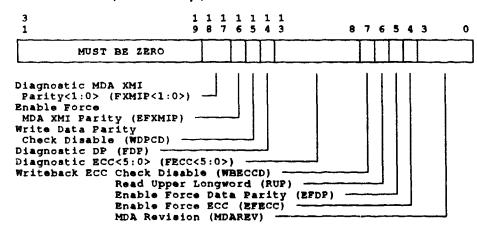

|             |       | EAL DIAGE                                                                                           | NUSTIC REGISTER (DUSH)                                                                                                                                                                                                                                                                        | 2-154<br>2-167 |                |

|             |       | INTERVAL                                                                                            | COUNTER REGISTER (SSCICR)                                                                                                                                                                                                                                                                     | 2-153          |                |

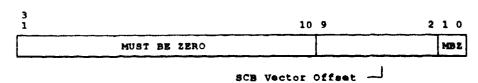

|             |       | TIMER INTI                                                                                          | ERRUPT VECTOR REGISTER 1 (TIVR1)                                                                                                                                                                                                                                                              | 2-152          |                |

|             |       |                                                                                                     | (T INTERVAL REGISTER 1 (TNIR1)                                                                                                                                                                                                                                                                |                |                |

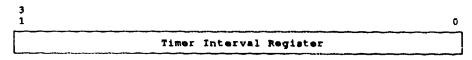

|             |       |                                                                                                     | • • •                                                                                                                                                                                                                                                                                         | 2-150          |                |

|             |       | TIMER CON                                                                                           | NTROL REGISTER 1 (TCR1)                                                                                                                                                                                                                                                                       | 2-147          |                |

|             |       | TIMER INT                                                                                           | T INTERVAL REGISTER 0 (TNIRO)<br>ERRUPT VECTOR REGISTER 0 (TIVRO)                                                                                                                                                                                                                             | 2-146          |                |

|             |       | TIMER NEX                                                                                           | (T INTERVAL REGISTER 0 (TNIRO)                                                                                                                                                                                                                                                                | 2-145          |                |

|             |       |                                                                                                     | ERVAL REGISTER 0 (TIRO)                                                                                                                                                                                                                                                                       | 2–141<br>2–144 |                |

|             |       | (EEADMR)                                                                                            |                                                                                                                                                                                                                                                                                               | 2-140          |                |

|             |       |                                                                                                     | DDRESS DECODE MASK REGISTER                                                                                                                                                                                                                                                                   |                |                |

|             |       |                                                                                                     | ASE ADDRESS REGISTER (EEBADR)                                                                                                                                                                                                                                                                 | 2-139          |                |

|             |       |                                                                                                     | REGISTER ADDRESS DECODE MASK<br>(CRADMR)                                                                                                                                                                                                                                                      | 2–138          |                |

|             |       | CONTROL                                                                                             | DECISTED ADDRESS DECODE MASK                                                                                                                                                                                                                                                                  |                |                |

|      | 2.9.3   | Bootstrapping or Restarting the Operating System |                                                                                                             | 2-206 |  |

|------|---------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------|--|

|      | 2.0.0   | 2.9.3.1                                          | Operating System Restart • 2–207                                                                            |       |  |

|      |         | 2.9.3.2                                          | Failing Restart • 2-208                                                                                     |       |  |

|      |         | 2.9.3.3                                          | Restart Parameters • 2-209                                                                                  |       |  |

|      |         | 2.9.3.4                                          | Operating System Bootstrap • 2-209                                                                          |       |  |

|      |         | 2.9.3.5                                          | Boot Algorithm • 2–210                                                                                      |       |  |

|      |         | 2.9.3.6                                          | Boot Parameters • 2-211                                                                                     |       |  |

| 0.40 | INITEDI | DOOF CO                                          | D COMMUNICATION TUROUCH TUR CONCOLE                                                                         |       |  |

| 2.10 | PROGE   |                                                  | R COMMUNICATION THROUGH THE CONSOLE                                                                         | 2-212 |  |

|      | 2.10.1  | Required                                         | Communications Paths                                                                                        | 2-212 |  |

|      | 2.10.2  | Console (                                        | Communications Area                                                                                         | 2-213 |  |

|      | 2.10.3  | Sending a                                        | Message to Another Processor                                                                                | 2-222 |  |

| 2.11 | ERROF   | R HANDLING                                       | 3                                                                                                           | 2-224 |  |

|      | 2.11.1  | General E                                        | rror Detection and Reporting Characteristics                                                                | 2-227 |  |

|      |         | 2.11.1.1                                         | MAXMI Error Handling • 2-227                                                                                |       |  |

|      |         | 2.11.1.2                                         | Parity Generation and Detection • 2-229                                                                     |       |  |

|      |         | 2.11.1.3                                         | •                                                                                                           |       |  |

|      |         | 2.11.1.4                                         | Self-Test-Detected Errors • 2-231                                                                           |       |  |

|      | 2.11.2  | Operating<br>Recovery                            | System (Macrocode) Error Handling and                                                                       | 2-231 |  |

|      |         | 2.11.2.1                                         |                                                                                                             |       |  |

|      |         | 2.11.2.2                                         | Error Analysis • 2–232                                                                                      |       |  |

|      |         | 2.11.2.3                                         | Error Recovery • 2–233                                                                                      |       |  |

|      |         | 2.11.2.4                                         | Vector Error Recovery • 2–237                                                                               |       |  |

|      |         | 2.11.2.5                                         | Error Retry • 2–238                                                                                         |       |  |

|      | 2.11.3  | Console 1                                        | Halt and Halt Interrupt                                                                                     | 2-238 |  |

|      | 2.11.4  | Machine                                          | Check Exceptions                                                                                            | 2-239 |  |

|      |         | 2.11.4.1                                         | MCHK_FP_PROTOCOL_ERROR • 2-246                                                                              |       |  |

|      |         | 2.11.4.2                                         | MCHK_FP_ILLEGAL_OPCODE • 2-246                                                                              |       |  |

|      |         | 2.11.4.3                                         | MCHK_FP_OPERAND_PARITY • 2-247                                                                              |       |  |

|      |         | 2.11.4.4                                         | MCHK_FP_UNKNOWN_STATUS • 2-247                                                                              |       |  |

|      |         | 2.11.4.5                                         | MCHK_FP_RESULT_PARITY • 2-248                                                                               |       |  |

|      |         | 2.11.4.6                                         | MCHK_TBM_ACV_TNV • 2-248                                                                                    |       |  |

|      |         | 2.11.4.7                                         | MCHK_TBH_ACV_TNV • 2-248                                                                                    |       |  |

|      |         | 2.11.4.8                                         | MCHK_INT_ID_VALUE • 2-249                                                                                   |       |  |

|      |         | 2.11.4.9                                         | MCHK_MOVC_STATUS • 2-249                                                                                    |       |  |

|      |         | 2.11.4.10                                        | <del></del>                                                                                                 |       |  |

|      |         | 2.11.4.11                                        |                                                                                                             |       |  |

|      |         | 2.11.4.12                                        | <del></del>                                                                                                 |       |  |

|      |         |                                                  | 1 PCSTS <p_tag_parity_error> • 2-250 2 PCSTS<p data="" error="" parity=""> • 2-250</p></p_tag_parity_error> |       |  |

|      |         |                                                  | MCHK BUSERR READ DAL • 2-251                                                                                |       |  |

|      |         |                                                  | 1 PCSTS <dal data="" error="" parity=""> • 2-251</dal>                                                      |       |  |

|      |         |                                                  | 2 PCSTS <b_cache hit=""> • 2-251</b_cache>                                                                  |       |  |

|      |         |                                                  | 3 SSCBTR <rwt> • 2-251</rwt>                                                                                |       |  |

|      |         |                                                  | 3.1 BCSTS <ac perr=""> • 2-252</ac>                                                                         |       |  |

|      |         |                                                  | 3.2 XBEER <acpe> • 2-252</acpe>                                                                             |       |  |

|        | 2.11.4.13.4   | SSCBTR <rwt> • 2-253</rwt>                                                                              |            |

|--------|---------------|---------------------------------------------------------------------------------------------------------|------------|

|        | 2.11.4.13.4.1 | XBER <err summary=""> • 2-253</err>                                                                     |            |

|        | 2.11.4.13.4.2 | BCSTS <tp_err> • 2-254</tp_err>                                                                         |            |

|        | 2.11.4.13.4.3 | B BCSTS <bts_vdperr> • 2-255</bts_vdperr>                                                               |            |

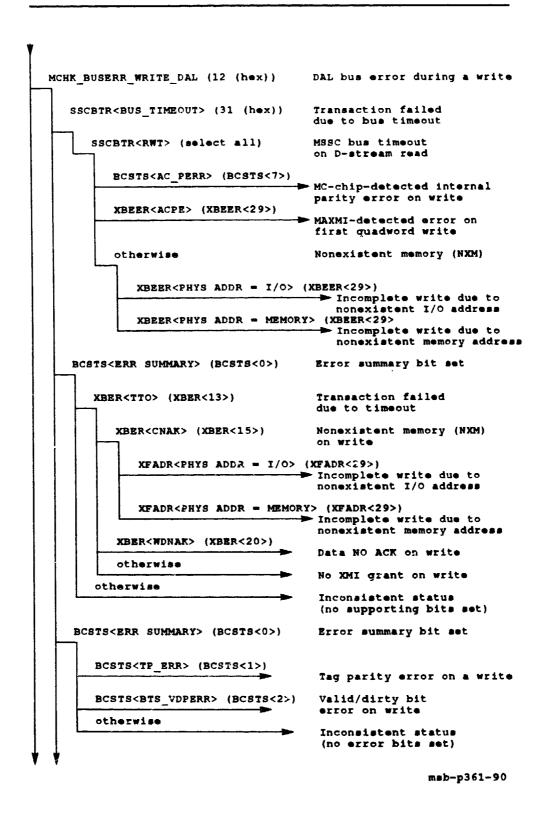

|        | 2.11.4.14     | MCHK BUSERR_WRITE_DAL • 2-255                                                                           |            |

|        | 2.11.4.14.1   | SSCBTR <bus_timeout> • 2-255</bus_timeout>                                                              |            |

|        |               | I SSCBTR <rwt> • 2-256</rwt>                                                                            |            |

|        |               | I.1BCSTS <ac perr=""> • 2-256</ac>                                                                      |            |

|        |               | 1.2XBEER <acpe> • 2-256</acpe>                                                                          |            |

|        |               | BCSTS <err_summary> • 2-257</err_summary>                                                               |            |

|        |               | Other MAXMI-Detected Errors • 2-257                                                                     |            |

|        |               | BCSTS <err summary=""> • 2-258</err>                                                                    |            |

|        |               | 1 BCSTS <tp_err> • 2-258</tp_err>                                                                       |            |

|        |               | 2 BCSTS <bts vdperr=""> • 2-259</bts>                                                                   |            |

|        |               | MCHK_UNKNOWN_BUSERR_TRAP • 2-259                                                                        |            |

|        |               | MCHK_VECTOR_STATUS • 2-259                                                                              |            |

|        | 2.11.4.17.1   | VA MCHK <uncorrectable_vib> • 2-259</uncorrectable_vib>                                                 |            |

|        | 2.11.4.17.1.  | 1 VINTSR <vec absent="" module=""> • 2-260</vec>                                                        |            |

|        | 2.11.4.17.1.  | 2 VINTSR <vectl herr="" vib=""> • 2-260</vectl>                                                         |            |

|        | 2.11.4.18     | VINTSR <cchip herr="" vib=""> • 2-260</cchip>                                                           |            |

|        | 2.11.4.19     | VINTSR <bus timeout=""> • 2-260</bus>                                                                   |            |

|        | 2.11.4.19.1   | VINTSR <vector module="" reset=""> • 2-261</vector>                                                     |            |

|        | 2.11.4.19.2   | NON_VALID VA FIX • 2-261                                                                                |            |

|        | 2.11.4.19.3   | VA MCHK <unexpected_vector_tnv> • 2-262</unexpected_vector_tnv>                                         |            |

|        |               | VA MCHK <unrecoverable_vector_module_er< th=""><th>R&gt; • 2-262</th></unrecoverable_vector_module_er<> | R> • 2-262 |

|        |               | VA MCHK <unexpected_vector_acv> • 2-263</unexpected_vector_acv>                                         |            |

|        |               | MCHK_ERROR_ISTREAM • 2-263                                                                              |            |

|        |               | PCSTS <dal_data_parity_error> • 2-263</dal_data_parity_error>                                           |            |

|        |               | 1 PCSTS <b_cache_hit> · 2-263</b_cache_hit>                                                             |            |

|        |               | 2 Memory Data Parity Error on I-Stream Read • 2-263                                                     |            |

|        |               | PCSTS <bus_error> • 2-264</bus_error>                                                                   |            |

|        |               | 1 SSCBTR <bus_timeout> • 2-264</bus_timeout>                                                            |            |

|        |               | 2 SSCBTR <rwt> • 2-264</rwt>                                                                            |            |

| 2.11.5 | Power Fail    | Interrupt                                                                                               | 2-266      |

| 2.11.6 | Hard Error    | Interrupt                                                                                               | 2-267      |

|        | 2.11.6.1      | XBER <wei> • 2-270</wei>                                                                                |            |

|        | 2.11.6.2      | XBEER <wtbdatax> and XBEER<wsqex> • 2-271</wsqex></wtbdatax>                                            |            |

|        | 2.11.6.3      | XBEER <wttox> • 2-271</wttox>                                                                           |            |

|        | 2.11.6.4      | XBEER <wseox> • 2-272</wseox>                                                                           |            |

|        | 2.11.6.5      | BCSTS <bts tperr=""> • 2-272</bts>                                                                      |            |

|        | 2.11.6.6      | BCSTS <bts vdperr=""> • 2-272</bts>                                                                     |            |

|        | 2.11.6.6.1    | BCSTS <ibus cycle=""> • 2-272</ibus>                                                                    |            |

|        | 2.11.6.6.2    | BCSTS <dal cmd=""> = Cache Fill • 2-273</dal>                                                           |            |

|        | 2.11.6.6.3    | BCSTS <dal cmd=""> = Invalidate or Writeback • 2-273</dal>                                              |            |

|        | 2.11.6.7      | BCSTS <i per<1:0=""> • 2-273</i>                                                                        |            |

|        | 2.11.6.8      | BCSTS <fill abort=""> • 2-274</fill>                                                                    |            |

|        | 2.11.6.9      | BCSTS <ac perr=""> • 2-274</ac>                                                                         |            |

|        | 2.11.6.10     | BCSTS <second err=""> • 2-275</second>                                                                  |            |

|        | 2.11.6.11     | XBER <pe> • 2-275</pe>                                                                                  |            |

|        | 2.11.6.12     | XBER <ipe> • 2-275</ipe>                                                                                |            |

|        |               | XBEER <wdpe> • 2-275</wdpe>                                                                             |            |

|        | 2.11.6.14     | XBEER <acpe> • 2-276</acpe>                                                                             |            |

|        |               |                                                                                                         |            |

|      |       |         | 2.11.6.16<br>2.11.6.17<br>2.11.6.18<br>2.11.6.19<br>2.11.6.20                                                                                                                     | XBEER <urr> • 2-276 VINTSR<vhe> • 2-276 VINTSR<vectl herr="" vib=""> • 2-277 VINTSR<cchip herr="" vib=""> • 2-277 VINTSR<bus timeout=""> • 2-277 XFAER<fcmd> = IDENT • 2-278</fcmd></bus></cchip></vectl></vhe></urr>                                                                                                                                                                 |       |

|------|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|      |       | 2.11.7  | 2.11.7.3<br>2.11.7.4<br>2.11.7.5<br>2.11.7.5.1<br>2.11.7.5.2<br>2.11.7.5.3<br>2.11.7.5.3.2<br>2.11.7.6<br>2.11.7.7<br>2.11.7.8<br>2.11.7.9<br>2.11.7.10<br>2.11.7.11<br>2.11.7.11 | Cache or Memory Errors • 2-279 P-Cache Errors • 2-279 PCSTS <p error="" parity="" tag=""> • 2-279 PCSTS<p data="" error="" parity=""> • 2-282 PCSTS<dal data="" error="" parity=""> • 2-282 PCSTS<b cache="" hit=""> • 2-282 Memory Data Parity Error • 2-282 PCSTS<bus error=""> • 2-283 SSCBTR<rwt> • 2-283 XFAER<fcmd> = ISTREAM_READ • 2-283</fcmd></rwt></bus></b></dal></p></p> | 2-279 |

|      |       | 2.11.8  | Kernel Sta                                                                                                                                                                        | ick Not Valid Exception                                                                                                                                                                                                                                                                                                                                                               | 2-286 |

|      |       | 2.11.9  | 2.11.9.1                                                                                                                                                                          | h No Notification CSR Read Data NO ACK • 2-286 CSR Write Sequence Error • 2-286                                                                                                                                                                                                                                                                                                       | 2286  |

|      |       | 2.11.10 | Error Reco                                                                                                                                                                        | overy Coding Examples                                                                                                                                                                                                                                                                                                                                                                 | 2-287 |

| CHAP | TER 3 | FV64A   | VECTOR                                                                                                                                                                            | PROCESSOR MODULE                                                                                                                                                                                                                                                                                                                                                                      | 3–1   |

|      | 3.1   | OVERV   | IEW                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                       | 3–2   |

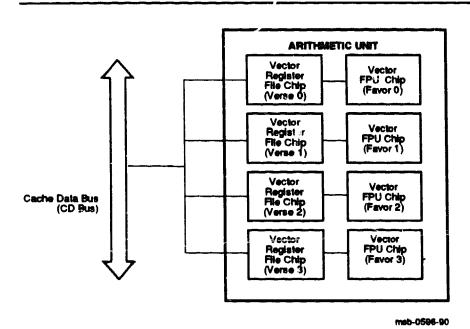

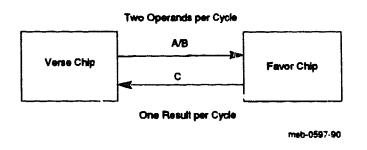

|      | 3.2   | FUNCT   | IONAL UNIT                                                                                                                                                                        | rs                                                                                                                                                                                                                                                                                                                                                                                    | 3-4   |

|      | 3.3   | BLOCK   | DIAGRAM                                                                                                                                                                           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                           | 3–6   |

|      |       | 3.3.1   |                                                                                                                                                                                   | ntrol Chip                                                                                                                                                                                                                                                                                                                                                                            |       |

|      |       | 3.3.2   |                                                                                                                                                                                   | gister File Chip                                                                                                                                                                                                                                                                                                                                                                      |       |

|      |       | 3.3.3   |                                                                                                                                                                                   | U Chip                                                                                                                                                                                                                                                                                                                                                                                |       |

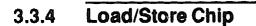

|      |       | 3.3.4   |                                                                                                                                                                                   | e Chip                                                                                                                                                                                                                                                                                                                                                                                |       |

|      |       | 3.3.5   | Clock Chi                                                                                                                                                                         | ρ                                                                                                                                                                                                                                                                                                                                                                                     | _ 3–9 |

| 3.4 | VECTO | R CONTROL UNIT         |                                                       |                                         | 3–10 |  |  |

|-----|-------|------------------------|-------------------------------------------------------|-----------------------------------------|------|--|--|

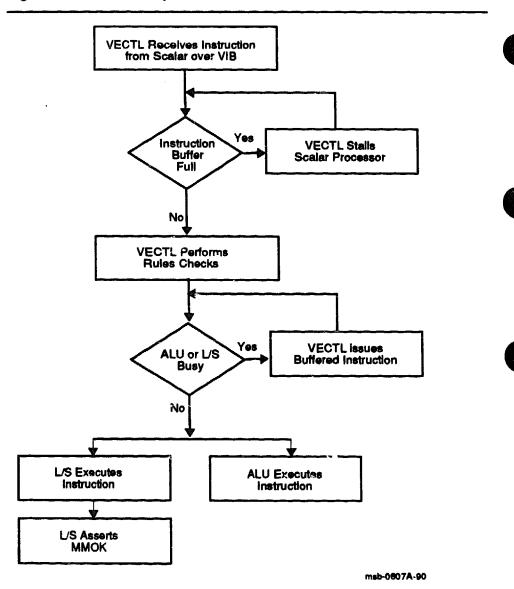

|     | 3.4.1 | Instruction Flow       |                                                       |                                         | 3-11 |  |  |

|     | 3.4.2 | Instruction Issue Rule | s                                                     |                                         | 3-12 |  |  |

|     | 3.4.3 | Data Types             |                                                       |                                         | 3-13 |  |  |

|     | 3.4.4 | Instruction Set        |                                                       |                                         | 3-13 |  |  |

|     |       |                        | ction • 3–13                                          |                                         |      |  |  |

|     |       | 3.4.4.2 Store Instru   | ction • 3-14                                          |                                         |      |  |  |

|     |       | 3.4.4.3 Gather/Sca     | tter Instructions • 3-14                              |                                         |      |  |  |

|     |       | 3.4.4.4 Masked Loa     | Masked Load/Store and Gather/Scatter Instructions • 3 |                                         |      |  |  |

|     |       |                        | ction • 3–14                                          |                                         |      |  |  |

|     |       |                        | ind Arithmetic Instructions • 3-1                     | 4                                       |      |  |  |

|     |       |                        | P Instructions • 3–14                                 |                                         |      |  |  |

|     |       |                        | R Instructions • 3–15                                 |                                         |      |  |  |

|     |       |                        | uction • 3–15                                         |                                         |      |  |  |

|     |       |                        | struction • 3–15                                      |                                         |      |  |  |

|     |       | 3.4.4.11 VSYNC Ins     | truction • 3–15                                       |                                         |      |  |  |

| 3.5 | ARITH | METIC UNIT             |                                                       |                                         | 3–16 |  |  |

|     |       |                        |                                                       |                                         |      |  |  |

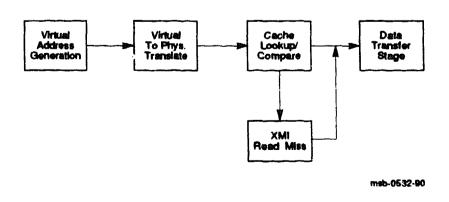

| 3.6 |       | STORE UNIT             |                                                       |                                         | 3–19 |  |  |

|     | 3.6.1 |                        |                                                       | <del></del>                             | 3-22 |  |  |

|     |       | 3.6.1.1 MMOK Sign      |                                                       |                                         |      |  |  |

|     |       | 3.6.1.2 Access Mo      |                                                       | 0.00                                    |      |  |  |

|     |       | •                      | anagement Control Registers •                         |                                         |      |  |  |

|     | 3.6.2 | Translation Butter     |                                                       | <del></del>                             | 3–24 |  |  |

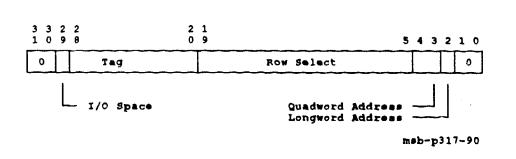

| 3.7 | CACH  | MEMORY                 |                                                       |                                         | 3-25 |  |  |

| ••• | 3.7.1 | _                      |                                                       |                                         | 3-25 |  |  |

|     | 3.7.2 | _                      |                                                       |                                         | 3-28 |  |  |

|     |       |                        | · ·                                                   |                                         |      |  |  |

|     | 3.7.3 |                        | ioned Memory Synchronization • 3                      |                                         | 3-30 |  |  |

|     |       |                        | Memory Synchronization • 3–30                         |                                         |      |  |  |

| 3.8 | VECT  | R PROCESSOR REGIS      | TERS                                                  | *************************************** | 3-31 |  |  |

|     | 3.8.1 | Access to Registers    |                                                       |                                         | 3-32 |  |  |

|     | 3.8.2 | Internal Processor Re  |                                                       |                                         | 3-34 |  |  |

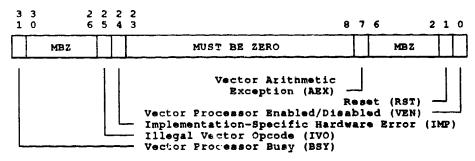

|     | 0.0.2 |                        | STATUS REGISTER (VPSR)                                | 3-36                                    | 0-0- |  |  |

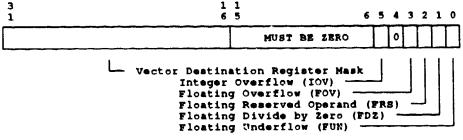

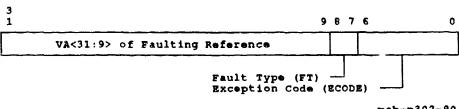

|     |       | (VAER)                 |                                                       | 3-39                                    |      |  |  |

|     |       | •                      | IVITY CHECK REGISTER                                  | -                                       |      |  |  |

|     |       | (VMAC)                 |                                                       | 3-41                                    |      |  |  |

|     |       |                        | BUFFER INVALIDATE ALL                                 |                                         |      |  |  |

|     |       | REGISTER (VTBIA)       |                                                       | 3-42                                    |      |  |  |

|     |       |                        | GISTER ADDRESS REGISTER                               |                                         |      |  |  |

|     |       | (VIADR)                |                                                       | 3-43                                    |      |  |  |

|     |       |                        | A LOW REGISTER (VIDLO)                                | 3-45                                    |      |  |  |

|     |       | VECTOR INDIRECT DAT    | A HIGH REGISTER (VIDHI)                               | 3-46                                    |      |  |  |

3-47

| 3.8.3 | Vector Indirect Registers                             |              |

|-------|-------------------------------------------------------|--------------|

|       | VECTOR REGISTER N (VREGN)                             | 3-49         |

|       | ARITHMETIC INSTRUCTION REGISTER (ALU_OP)              | 3–51         |

|       | SCALAR OPERAND LOW REGISTER                           |              |

|       | (ALU_SCOP_LO)                                         | 3–55         |

|       | SCALAR OPERAND HIGH REGISTER                          | 3–56         |

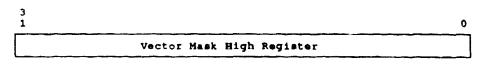

|       | (ALU_SCOP_HI)  VECTOR MASK LOW REGISTER (ALU MASK LO) | 3–56<br>3–57 |

|       | VECTOR MASK HIGH REGISTER (ALU MASK HI)               | 3-57<br>3-58 |

|       | EXCEPTION SUMMARY REGISTER (ALU EXC)                  | 3-59         |

|       | DIAGNOSTIC CONTROL REGISTER (ALU DIAG CTL)            | 3-55<br>3-61 |

|       | CURRENT ALU INSTRUCTION REGISTER                      | <b>3-01</b>  |

|       | (VCTL_CALU)                                           | 3-64         |

|       | DEFERRED ALU INSTRUCTION REGISTER                     |              |

|       | (VCTL_DALU)                                           | 3-67         |

|       | CURRENT ALU OPERAND LOW REGISTER                      |              |

|       | (VCTL_COP_LO)                                         | 3-70         |

|       | CURRENT ALU OPERAND HIGH REGISTER                     |              |

|       | (VCTL_COP_HI)                                         | 3–71         |

|       | DEFERRED ALU OPERAND LOW REGISTER                     |              |

|       | (VCTL_DOP_LO)                                         | 3–72         |

|       | DEFERRED ALU OPERAND HIGH REGISTER                    | 0.70         |

|       | (VCTL_DOP_HI)                                         | 3–73         |

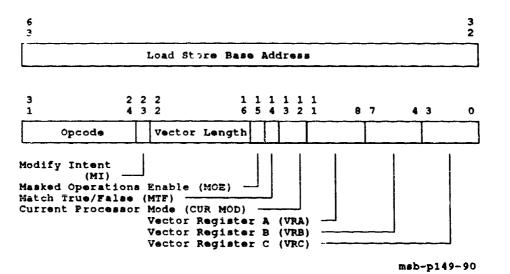

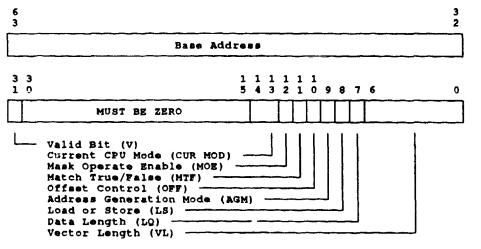

|       | LOAD/STORE INSTRUCTION REGISTER                       | 3–74         |

|       | (VCTL_LDST) LOAD/STORE STRIDE REGISTER (VCTL_STRIDE)  | 3-74<br>3-77 |

|       | ILLEGAL INSTRUCTION REGISTER (VCTL_ILL)               | 3–77<br>3–78 |

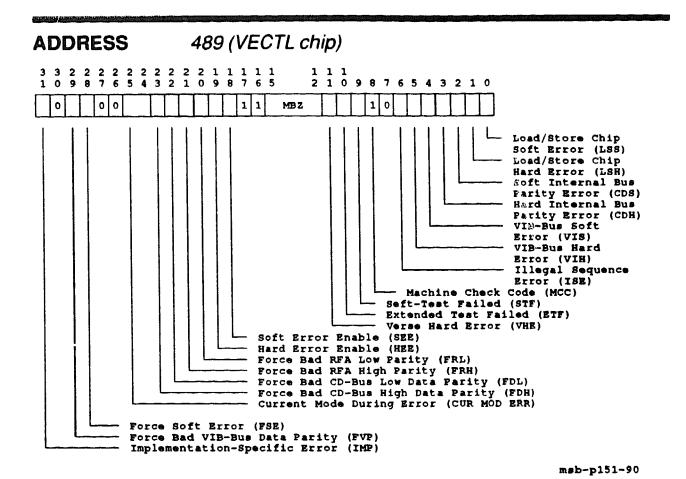

|       | STATUS REGISTER (VCTL_CSR)                            | 3–76<br>3–81 |

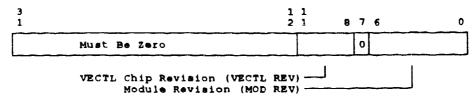

|       | MODULE REVISION REGISTER (MOD REV)                    | 3–88         |

|       | VECTOR COPY-PO BASE REGISTER (LSX POBR)               | 3–89         |

|       | VECTOR COPY-PO BASE REGISTER (LSX_POLR)               | 3–90         |

|       | VECTOR COPY-P1 BASE REGISTER (LSX P1BR)               | 3–90<br>3–91 |

|       | VECTOR COPY-P1 LENGTH REGISTER (LSX_P1LR)             | 3–92         |

|       | VECTOR COPY-SYSTEM BASE REGISTER                      | J 12         |

|       | (LSX SBR)                                             | 3–93         |

|       | VECTOR COPY-SYSTEM LENGTH REGISTER                    |              |

|       | (LSX_SLR)                                             | 3-94         |

|       | LOAD/STORE EXCEPTION REGISTER (LSX_EXC)               | 3~95         |

|       | TRANSLATION BUFFER CONTROL REGISTER                   |              |

|       | (LSX_TBCSR)                                           | 3–97         |

|       | VECTOR COPY-MEMORY MANAGEMENT ENABLE                  |              |

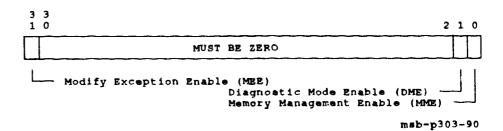

|       | REGISTER (LSX_MAPEN)                                  | 3–98         |

|       | VECTOR COPY-TRANSLATION BUFFER INVALIDATE             |              |

|       | ALL REGISTER (LSX_TBIA)                               | 3–99         |

|       | VECTOR COPY-TRANSLATION BUFFER INVALIDATE             |              |

|       | SINGLE REGISTER (LSX_TBIS)                            | 3-100        |

|       | VECTOR MASK LOW REGISTER (LSX_MASKLO)                 | 3-101        |

|       | VECTOR MASK HIGH REGISTER (LSX_MASKHI)                | 3-102        |

|       | LOAD/STORE STRIDE REGISTER (LSX_STRIDE)               | 3–103        |

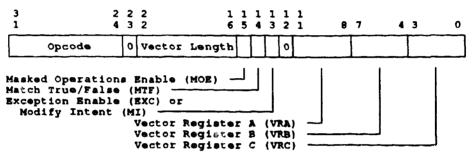

|       | LOAD/STORE INSTRUCTION REGISTER (LSX_INST)            | 3-104        |

|       | CACHE CONTROL REGISTER (LSX_CCSR)                     | 3–107        |

|       | TRANSLATION BUFFER TAG REGISTER                       |              |

|       | (LSX_TBTAG)                                           | 3-113        |

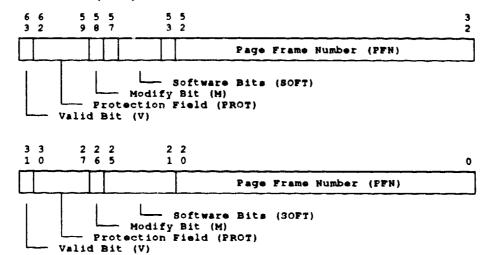

|       | TRANSLATION BUFFER PTE REGISTER (LSX_PTE)             | 3-114        |

| 3   | 3.9    | ERROF                      | HANDLING             |                                       |      | 3-117 |  |

|-----|--------|----------------------------|----------------------|---------------------------------------|------|-------|--|

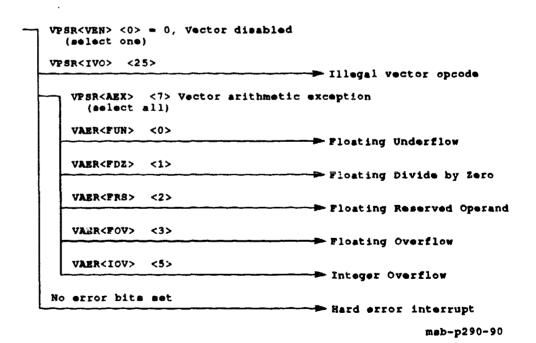

|     |        | 3.9.1                      | Machine Checks       |                                       |      | 3-119 |  |

|     |        | 3.9.2 Hard Error Interrupt |                      |                                       |      | 3-122 |  |

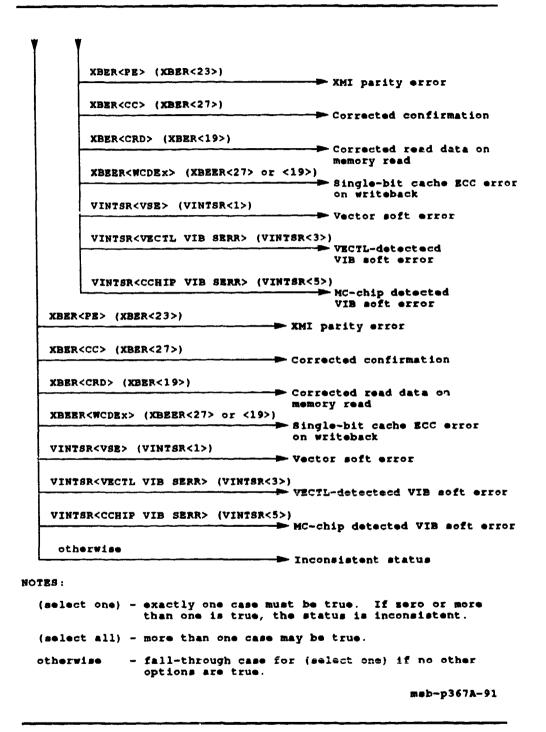

|     |        | 3.9.3                      | Soft Error Interrupt |                                       |      |       |  |

|     |        | 3.9.4                      |                      |                                       |      | 3-125 |  |

|     |        |                            |                      | ory Management Exceptions • 3-125     |      |       |  |

|     |        |                            |                      | r Arithmetic Exceptions • 3–125       |      |       |  |

|     |        |                            | 3.9.4.3 Disab        | le Faults • 3–127                     |      |       |  |

| CHA | PTER 4 | MS65/                      | MEMORY MOI           | DULE                                  |      | 4-1   |  |

|     | 4.1    | MODU                       | E DESCRIPTION        |                                       |      | 4-2   |  |

|     |        |                            |                      |                                       |      |       |  |

|     | 4.2    | = '                        | EST AND INITIAL      |                                       |      | 4-4   |  |

|     |        | 4.2.1                      | -                    | ding Addresses                        |      | 4-5   |  |

|     |        | 4.2.2                      | Interleaving         |                                       |      | 4–5   |  |

|     | 4.3    | CONT                       | ROL AND STATUS       | _                                     |      | 4-6   |  |

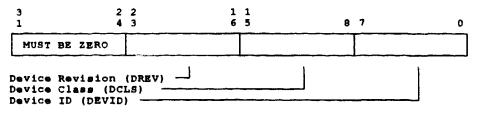

|     |        |                            | DEVICE REGISTE       |                                       | 4-8  |       |  |

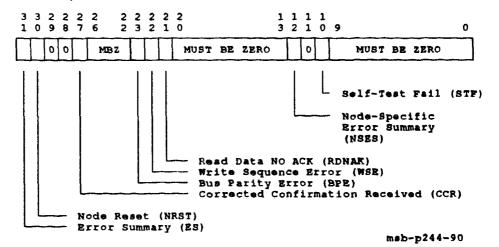

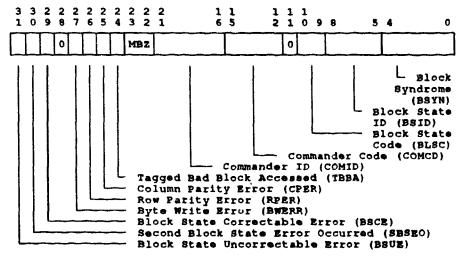

|     |        |                            | BUS ERROR REG        | , ,                                   | 410  |       |  |

|     |        |                            |                      | OL REGISTER 1 (MCTL1)                 | 4–14 |       |  |

|     |        |                            |                      | RROR REGISTER (MECER)                 | 4–17 |       |  |

|     |        |                            | (MECEA)              | RROR ADDRESS REGISTER                 | 4–21 |       |  |

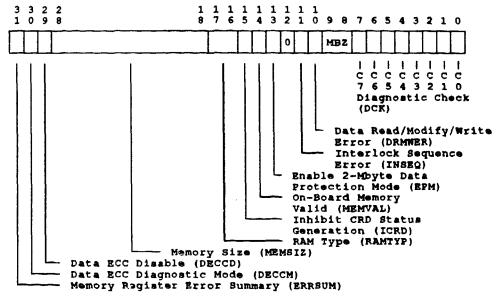

|     |        |                            | •                    | OL REGISTER 2 (MCTL2)                 | 4–22 |       |  |

|     |        |                            | TCY TESTER REC       | · · · · · · · · · · · · · · · · · · · | 4-24 |       |  |

|     |        |                            |                      | CC ERROR REGISTER (BECER)             | 4-25 |       |  |

|     |        |                            |                      | CC ADDRESS REGISTER (BECEA)           | 4-26 |       |  |

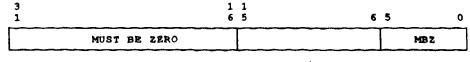

|     |        |                            |                      | ESS REGISTER (STADR)                  | 4-27 |       |  |

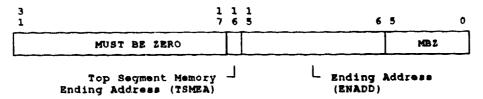

|     |        |                            |                      | S REGISTER (ENADR)                    | 4-28 |       |  |

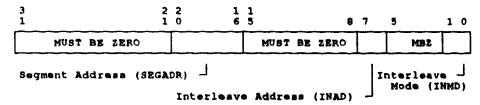

|     |        |                            |                      | LEAVE REGISTER (INTLV)                | 4-30 |       |  |

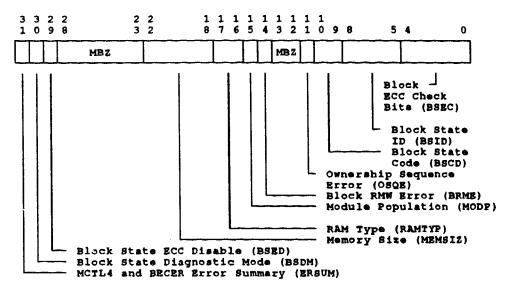

|     |        |                            | MEMORY CONTR         | OL REGISTER 3 (MCTL3)                 | 4-32 |       |  |

|     |        |                            | MEMORY CONTR         | OL REGISTER 4 (MCTL4)                 | 4-34 |       |  |

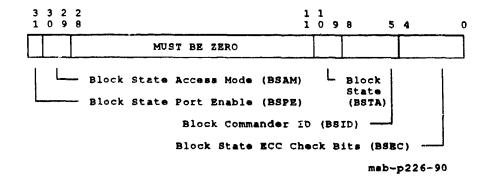

|     |        |                            | BLOCK STATE C        | ONTROL REGISTER (BSCTL)               | 4-37 |       |  |

|     |        |                            |                      | DDRESS REGISTER (BSADR)               | 4-39 |       |  |

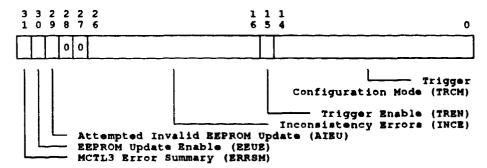

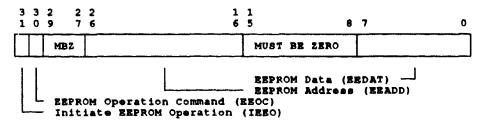

|     |        |                            |                      | OL REGISTER (EECTL)                   | 4-40 |       |  |

|     |        |                            | TIMEOUT CONTR        | IOL/STATUS REGISTER (TMOER)           | 4-42 |       |  |

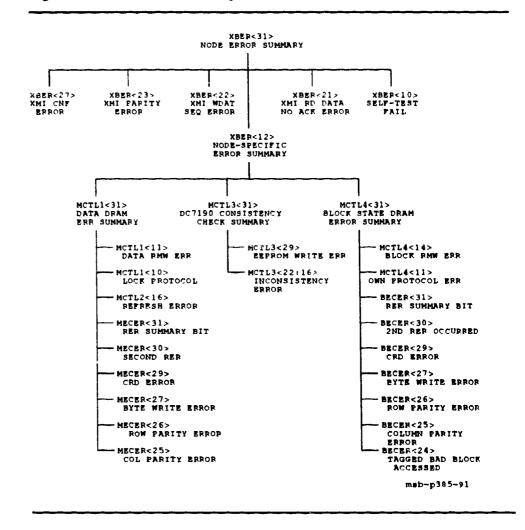

|     | 4.4    | ERRO                       | R HANDLING           |                                       |      | 4-43  |  |

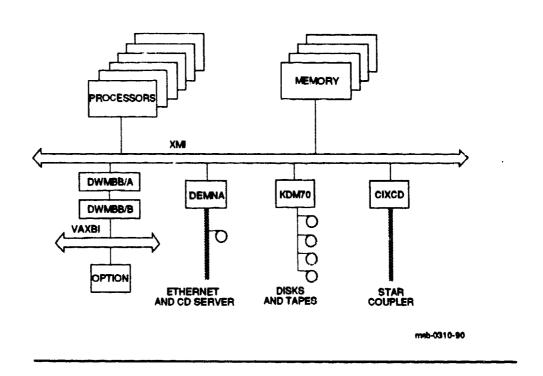

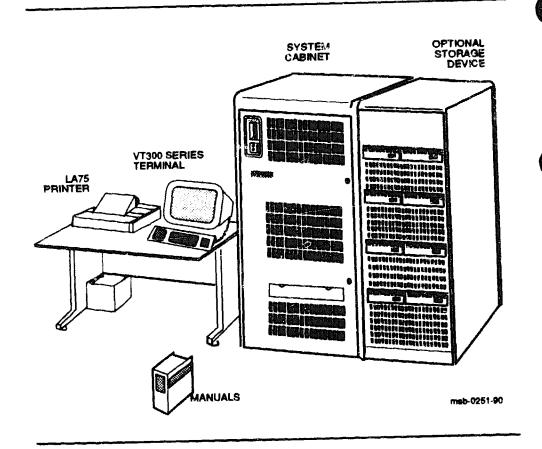

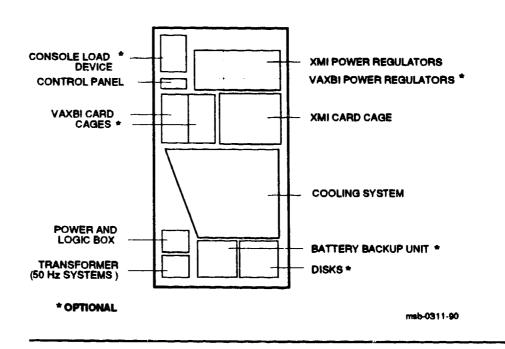

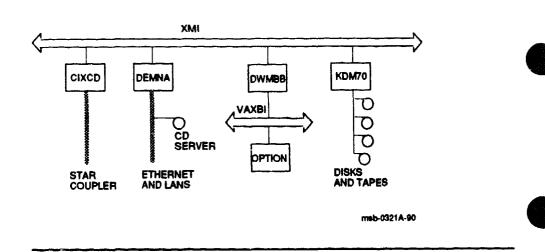

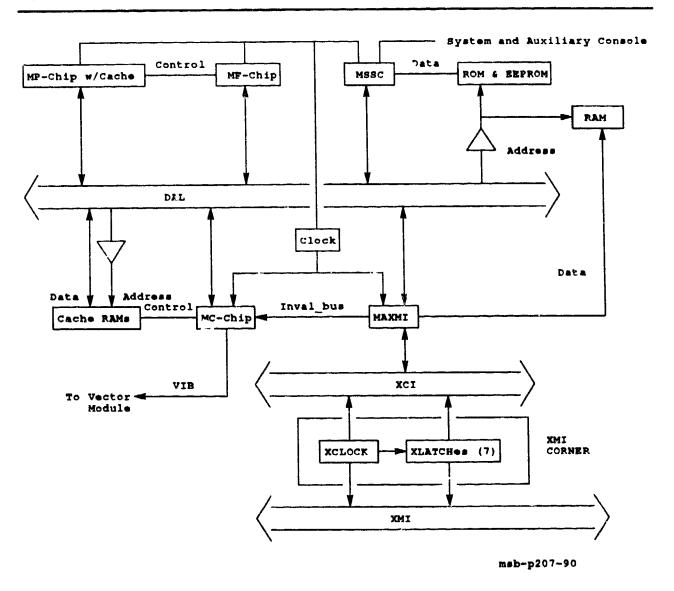

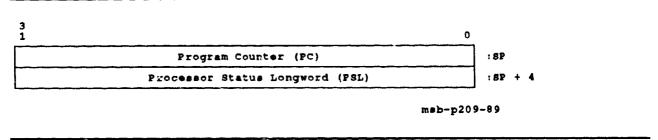

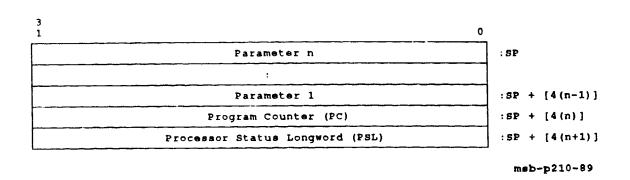

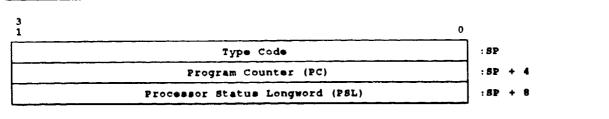

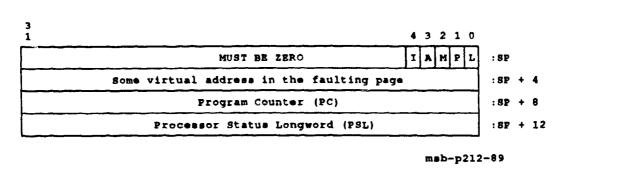

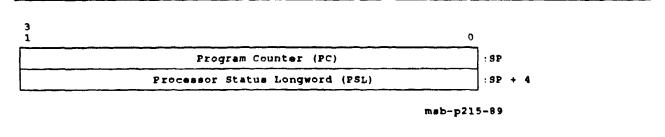

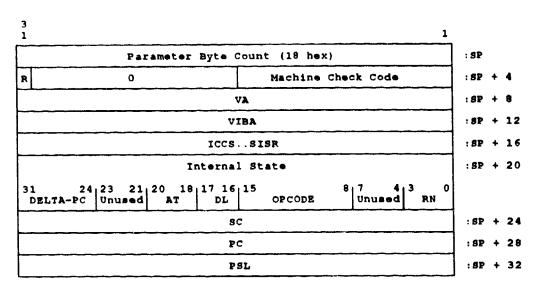

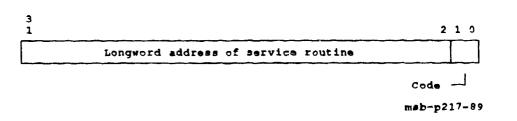

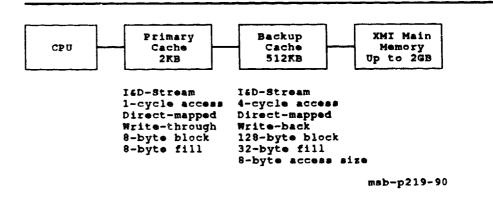

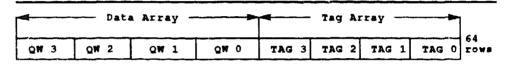

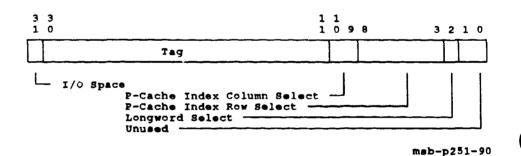

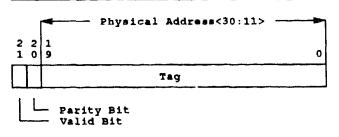

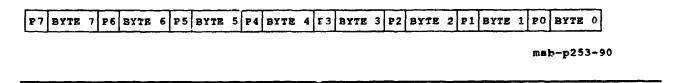

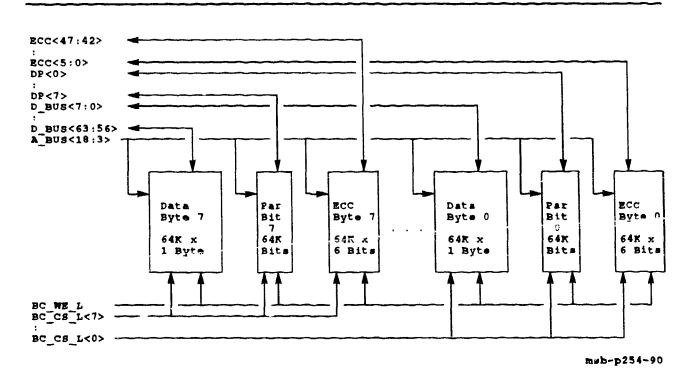

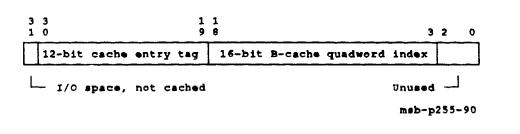

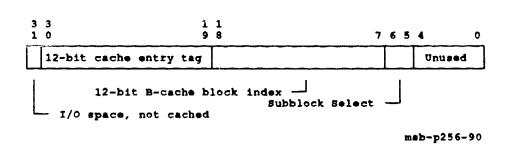

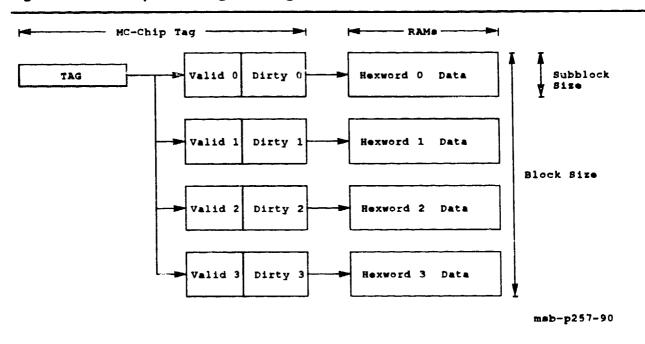

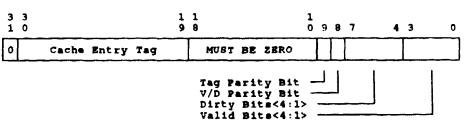

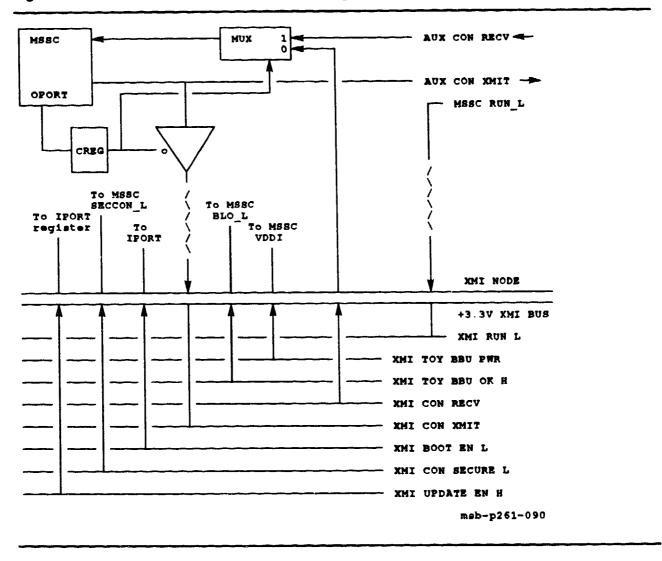

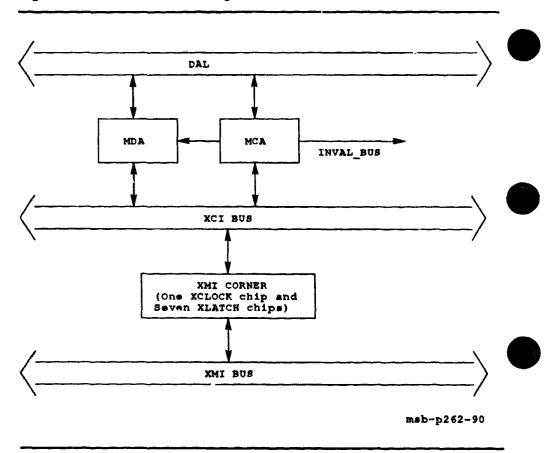

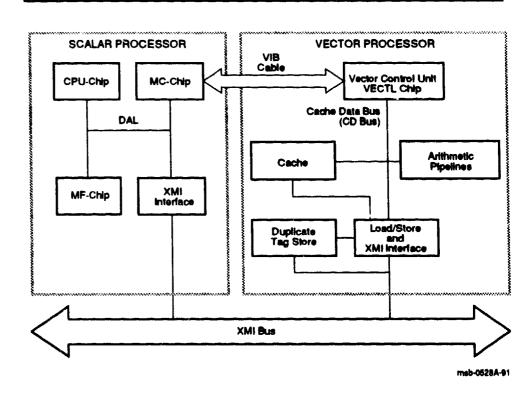

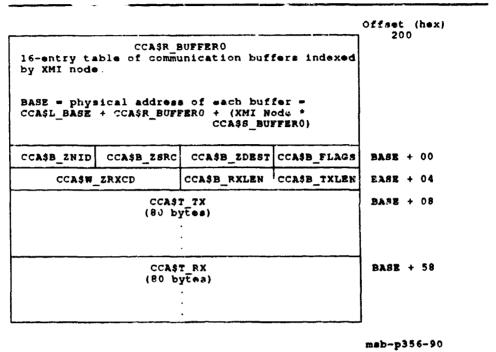

#### INDEX **EXAMPLES** 2-287 2-1 Error Recovery Coding **FIGURES** System Architecture 1-2 1-1 1-2 1-4 Sample System \_\_\_\_\_\_ System Front View \_\_\_\_\_ 1-6 1-3 1-4 System Rear View \_\_\_\_\_\_\_ 1-8 1-5 1-10 Adapters KA65A CPU Module Block Diagram 2-2 2-1 2-2 Minimum Stack Frame 2-11 2-12 2-3 Large Stack Frame \_\_\_\_ Arithmetic Exception Stack Frame 2-16 2-4 2-5 Memory Management Exception Stack Frame 2-17 Emulated Instruction Trap 2-18 2-6 Emulated Instruction Fault 2-7 2-19 2-20 2-8 Machine Check Stack Frame 2-9 System Control Block Vectors 2-25 2-10 Process Control Block 2-28 CPU Module Cache Memory 2-11 2-31 2-12 Primary Cache Organization \_\_\_\_\_ 2-34 2-13 Primary Cache Physical Address 2-34 2-35 2-14 Tag Entry Organization \_\_\_ 2-15 Quadword Data Array Organization of the Primary Cache 2-35 2-37 2-16 Backup Cache Organization 2~38 2-17 Backup Cache RAM Addressing \_\_\_\_\_\_ 2-38 2-18 MC-Chip Tag Store Addressing 2-19 Backup Cache Tag Store Organization 2-39 2-20 2-40 Backup Cache Tag Store Block Diagram 2-21 Backup Cache Tag Store Addressing Using Physical Address \_\_\_\_ 2-41 2-22 D\_BUS Format to Access BCBTS \_\_\_\_ 2-41 2-23 Control Panel Connections Including Console Lines 2-43 2-24 MAXMI Block Diagram 2-46 2-25 KA65A CPU Module Private I/O Address Space Map 2-48 2-26 Scalar/Vector Pair Block Diagram 2-55 2-27 Initialization Flowchart 2-197 2-28 Restart Parameter Block Format 2-207 2-29 **CCA Lavout** 2-215 2-30 Layout of XMI Node Buffers 2-220

| 2-31         | Machine Check Parse Tree                                                                                                                                                                     | 2-6 |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2-32         | Hard Error Interrupt Parse Tree                                                                                                                                                              | 2-2 |

| 2-33         | Soft Error Interrupt Parse Tree                                                                                                                                                              | 2-2 |

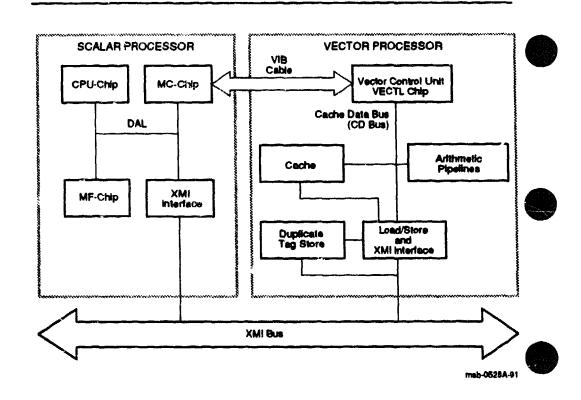

| 3–1          | Scalar/Vector Pair Block Diagram                                                                                                                                                             |     |

| 3–2          | FV64A Vector Processor Functional Units                                                                                                                                                      | 3   |

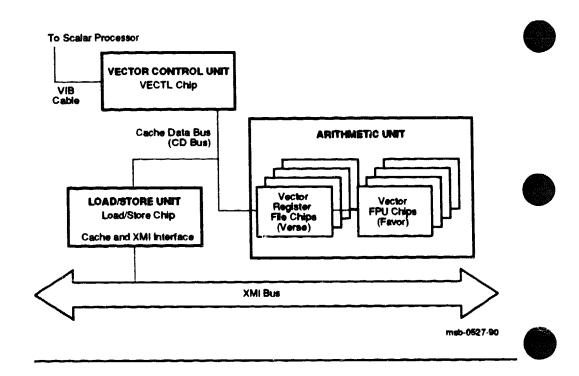

| 3–3          | FV64A Vector Processor Block Diagram                                                                                                                                                         |     |

| 3-4          | VECTL Chip Instruction Flow                                                                                                                                                                  |     |

| 3–5          | Vector Arithmetic Unit                                                                                                                                                                       |     |

| 3–6          | Verse/Favor Chip Bus Operation                                                                                                                                                               |     |

| 37           | Address/Data Flow in Load/Store Pipeline                                                                                                                                                     |     |

| 3–8          | Cache Arrangement                                                                                                                                                                            |     |

| 3-9          | Physical Address                                                                                                                                                                             |     |

| 3–10         | Tag Entry Organization                                                                                                                                                                       |     |

| 3–11         | Cache Data Organization                                                                                                                                                                      |     |

| 3–12         | Vector Length and Vector Count Registers                                                                                                                                                     |     |

| 3–13         | Vector Mask Register                                                                                                                                                                         |     |

| 3–14         | Machine Check Stack Frame                                                                                                                                                                    |     |

| 3–15         | Machine Check Parse Tree                                                                                                                                                                     | _   |

| 3–16         | Hard Error Interrupt Parse Tree                                                                                                                                                              |     |

| 3–17         | Soft Error Interrupt Parse Tree                                                                                                                                                              |     |

| 3–18         | Disable Fault Parse Tree                                                                                                                                                                     |     |

| 4–1          | Error Bit Hierarchy                                                                                                                                                                          | 4   |

| TABLES       |                                                                                                                                                                                              |     |

| 1            | VAX 6000 Series Documentation                                                                                                                                                                |     |

| 2            | VAX 6000 Model Level Documentation                                                                                                                                                           |     |

| 3            | Associated Documents                                                                                                                                                                         |     |

| 1-1          | System Components                                                                                                                                                                            |     |

| 1–2          | Adapters                                                                                                                                                                                     |     |

| 2-1          | KA65A CPU Module Interrupts                                                                                                                                                                  | 2   |

| 2–2          | KA65A CPU Module Exceptions                                                                                                                                                                  |     |

| 2-3          | Arithmetic Exceptions Type Codes                                                                                                                                                             |     |

| 2-4          | Memory Management Exceptions                                                                                                                                                                 |     |

| 2-5          | Emulated Instruction Trap Stack Frame Parameters                                                                                                                                             |     |

| 2–6          | Machine Check Stack Frame Parameters                                                                                                                                                         |     |