# **DECsystem 5500 Technical Manual**

Order Number EK-D5500-TM-001

**Digital Equipment Corporation**

#### January 1991

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license.

No responsibility is assumed for the use or reliability of software on equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Restricted Rights: Use, duplication, or disclosure by the U. S. Government is subject to restrictions as set forth in subparagraph (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

Copyright © Digital Equipment Corporation 1991

All Rights Reserved. Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation:

| DEC          | DIBOL     | UNIBUS     |

|--------------|-----------|------------|

| DEC/CMS      | EduSystem | VAX        |

| DEC/MMS      | IAS       | VAXcluster |

| DECnet       | MASSBUS   | VMS .      |

| DECsystem-10 | PDP       | VT         |

| DECSYSTEM-20 | PDT       |            |

| DECUS        | RSTS      |            |

| DECwriter    | RSX       | digital    |

|              |           | 9,19,1,4   |

Prestoserve is a trademark of Legato Systems, Inc.. The trademark and software are licensed to Digital Equipment Corporation by Legato Systems, Inc.

This document was prepared and published by Educational Services Development and Publishing, Digital Equipment Corporation.

# **Contents**

| Ab | About This Manual              |                                                     | ххі        |  |

|----|--------------------------------|-----------------------------------------------------|------------|--|

| 1  | KN2                            | 20-AA Subsystem Overview                            |            |  |

|    | 1.1                            | Introduction                                        | 1-1        |  |

|    | 1.2                            | Central Processing Subsystem                        | 1–6        |  |

|    | 1.3                            | R3000 RISC Processor                                | 16         |  |

|    | 1.4                            | Floating-Point Accelerator                          | 1-7        |  |

|    | 1.5                            | Cache Memory                                        | 1–7        |  |

|    | 1.6                            | MS220-Ax Memory Modules                             | 1-7        |  |

|    | 1.7                            | Mass Storage Interfaces DSSI/SCSI                   | 1–7        |  |

|    | 1.8                            | Ethernet Interface                                  | 1-8        |  |

|    | 1.9                            | Q22-bus Interface                                   | 1–9        |  |

|    | 1.10                           | Firmware                                            | 1–9        |  |

| 2  | Installation and Configuration |                                                     |            |  |

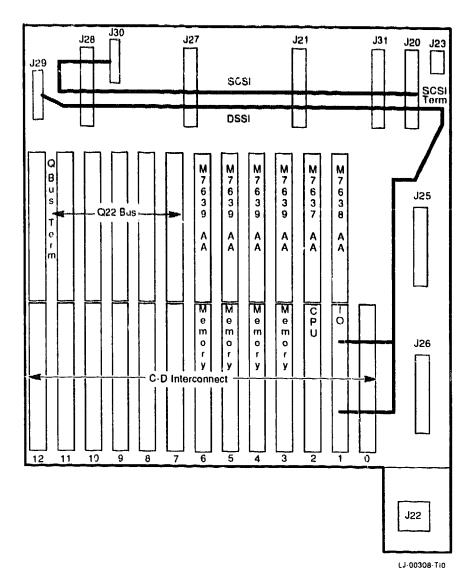

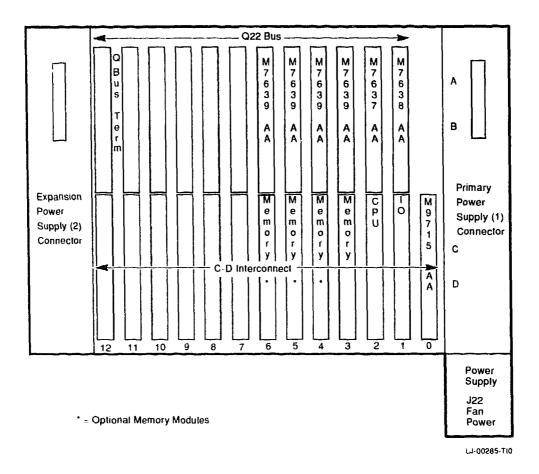

|    | 2.1                            | Installing the KN220-AA and MS220-Ax Memory Modules | 2-1        |  |

|    | 2.2                            | Module Configuration and Naming                     | 2–4        |  |

|    | 2.3                            | Mass Storage Configuration                          | 2–4        |  |

|    | 2.3.1                          | 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6             | 2–5        |  |

|    | 2.3.2                          | Changing the DSSI Unit Number                       | 2–6        |  |

| 3  | KNa                            | 220-AA Architecture                                 |            |  |

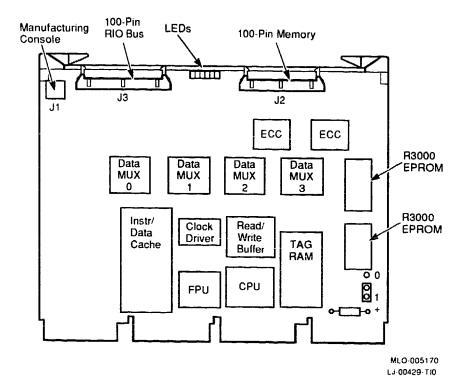

|    | 3.1                            | KN220-AA CPU Module Summary                         | 3-1        |  |

|    | 3.2                            | General Description                                 | 3-1        |  |

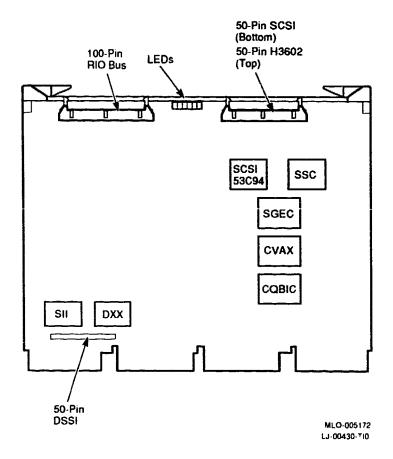

|    | 3.3                            | KN220-AA I/O Module Summary                         | 3-2        |  |

|    | 3.4                            | KN220-AA R3000 RISC Processor                       | 3-3        |  |

|    | 3.4.1                          | Processor Features                                  | 3–3        |  |

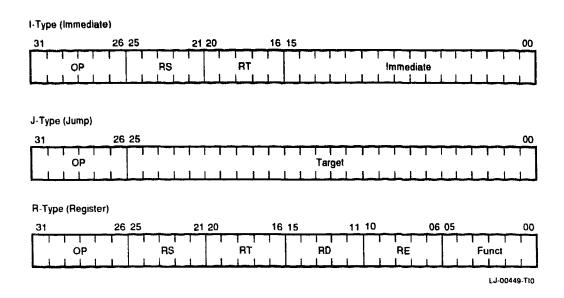

|    | 3.4.1                          |                                                     | 3-3<br>3-4 |  |

| 3.4.2   | Coprocessors                                 | 3–7  |

|---------|----------------------------------------------|------|

| 3.4.2.1 | Coprocessor (0)                              | 3-7  |

| 3.4.2.2 | Coprocessor (1)                              | 3–8  |

| 3.4.2.3 | Coprocessor (2)                              | 3–8  |

| 3.4.2.4 | Coprocessor (3)                              | 3-8  |

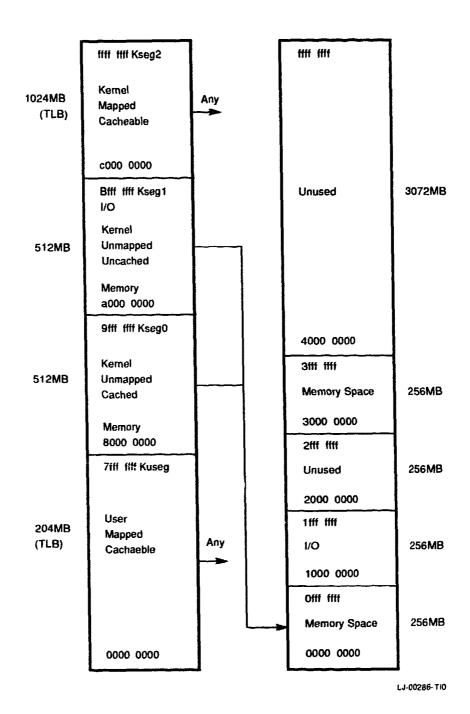

| 3.4.3   | Memory Management                            | 3-8  |

| 3.4.3.1 | Operating Modes                              | 3–9  |

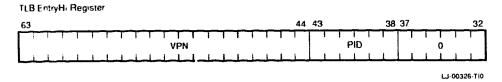

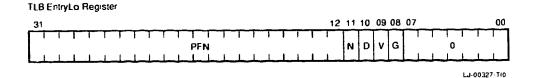

| 3.4.3.2 | EntryHi (EH) and EntryLow (EL) Registers     | 3-10 |

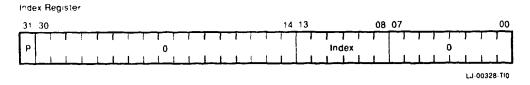

| 3.4.3.3 | The Index Register (IR)                      | 3-11 |

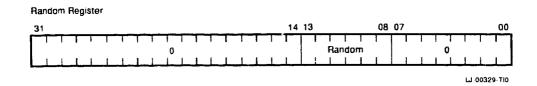

| 3.4.3.4 | The Random Register (RR)                     | 3-11 |

| 3.4.4   | Exception Handling Registers                 | 3-12 |

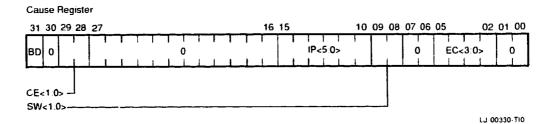

| 3.4.4.1 | The Cause Register (CR)                      | 3-12 |

| 3.4.4.2 | Exception Program Counter (EPC)              | 3-14 |

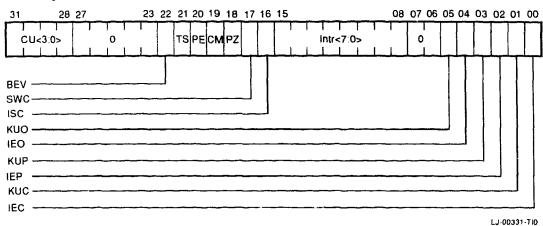

| 3.4.4.3 | The Status Register (SR)                     | 3-14 |

| 3.4.4.4 | BadVaddr Register (BVA)                      | 3-15 |

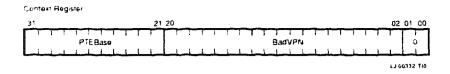

| 3.4.4.5 | Context Register (CR)                        | 3-15 |

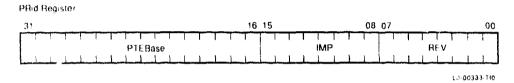

| 3.4.4.6 | Processor Revision Identifier Register (PRR) | 3-16 |

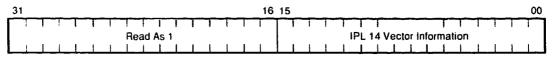

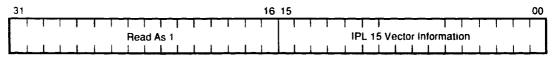

| 3.4.4.7 | Interrupt Service and Interrupt Vectors      | 3-16 |

| 3.4.5   | Exceptions                                   | 3-18 |

| 3.4.5.1 | General Exception Vector                     | 3–19 |

| 3.4.5.2 | Reset Exception Vector                       | 3-19 |

| 3.5 F   | N220-AA Cache Memory                         | 3-19 |

| 3.5.1   | Cache Organization                           | 3-19 |

| 3.5.2   | Cache Isolation                              | 3-19 |

| 3.5.3   | Cache Swapping                               | 3-20 |

| 3.5.4   | Cache Line Format                            | 3–20 |

| 3.6 F   | KN220-AA Main Memory System                  | 3-21 |

| 3.6.1   | Main Memory Error Detection and Correction   | 3-22 |

| 3.6.1.1 | Main Memory Single Bit Errors                | 3–22 |

| 3.6.1.2 | Main Memory Multi-Bit Errors                 | 3-23 |

| 3.6.1.3 | Non-Existent Memory Errors                   | 3-23 |

| 3.6.1.4 | Memory Interrupts during I/O cycles          | 3-23 |

| 3.6.1.5 | MEAR and MESR Updates                        | 3-24 |

| 3.7 I   | KN220-AA Console Serial Line                 | 3-24 |

| 3.7.1   | Console Registers                            | 3-24 |

| 3.8 I   | KN220-AA Boot and Diagnostic Facility        | 3-25 |

| 3.8.1   | R3000 LED Register                           | 3-26 |

| 3.8.2   | ROM Memory                                   | 3-26 |

| 3.8.2.1 | ROM Socket                                   | 3-26 |

| 3.8.2.2 | ROM Address Space                            | 3-26 |

| 3.8.3   | Battery Backed-Up RAM                        | 3-27 |

| 3.8.4 KN220-AA CPU Module Initialization                    | 3–27 |

|-------------------------------------------------------------|------|

| 3.8.4.1 Power Up Initialization                             | 3–27 |

| 3.8.4.2 Hardware Reset                                      | 3–27 |

|                                                             | 3–27 |

| 3.8.4.4 Processor Initialization                            | 3–28 |

| 3.8.5 I/O Presence Register (IOPRE)                         | 3–28 |

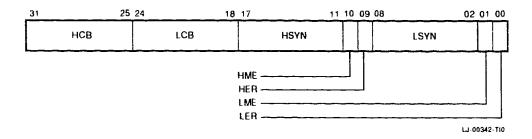

| 3.8.6 Memory Error Syndrome Register (MESR)                 | 3–29 |

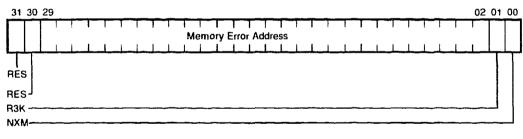

| 3.8.7 Memory Error Address Register (MEAR)                  | 3–30 |

| 3.9 I/O Module Specification                                | 3-31 |

| 3.9.1 KN220-AA I/O Module Summary                           | 3–31 |

| 3.10 KN220-AA CPU Interface                                 | 3–31 |

| 3.10.1 I/O Devices                                          | 3-31 |

| 3.10.2 KN220-AA I/O Initialization                          | 3-32 |

| 3.10.2.1 Power up Initialization                            | 3–32 |

| 3.10.2.2 Hardware Reset                                     | 3-32 |

| 3.10.2.3 I/O Bus Initialization                             | 3–32 |

| 3.10.2.4 Processor Initialization                           | 3–32 |

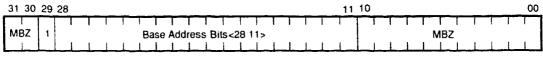

| 3.10.2.5 SSC Base Address Register (SSCBR)                  | 3-33 |

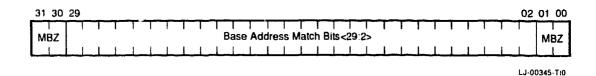

| 3.10.2.6 Address Decode Match Register (ADMTR0)             | 3-33 |

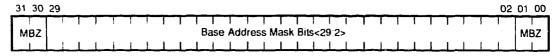

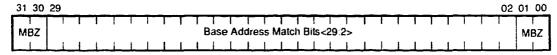

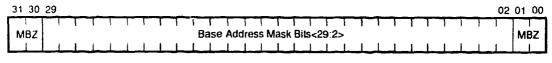

| 3.10.2.7 Address Decode Mask Register (ADMKR0)              | 3-34 |

| 3.10.2.8 Address Decode Match Register (ADMTR1)             | 3-34 |

| 3.10.2.9 Address Decode Mask Register (ADMKR1)              | 3–35 |

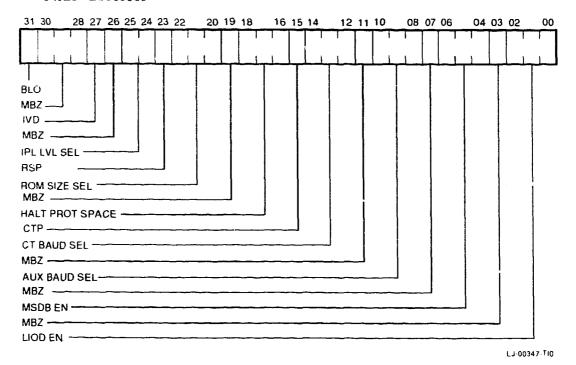

| 3.10.2.10 SSC Configuration Register (SSCCR)                | 3-35 |

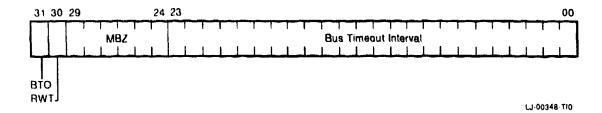

| 3.10.3 CDAL Bus Timeout Control Register (CBTCR)            | 3-37 |

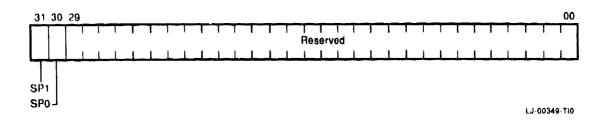

| 3.10.4 Select Processor Register (SPR)                      | 3-38 |

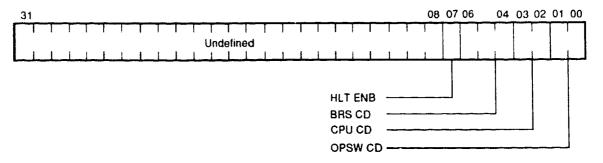

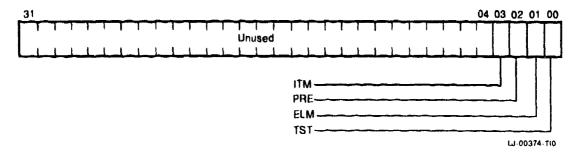

| 3.10.5 Boot and Diagnostic Register (BDR)                   | 3-39 |

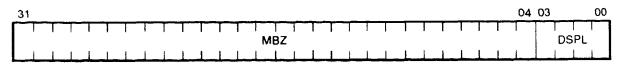

| 3.10.6 Diagnostic LED Register (DLEDR)                      | 3-41 |

| 3.11 I/O Device Interrupts                                  | 3-42 |

| 3.12 KN220-AA Console Serial Line                           | 3-42 |

| 3.12.1 Console Registers                                    | 3-42 |

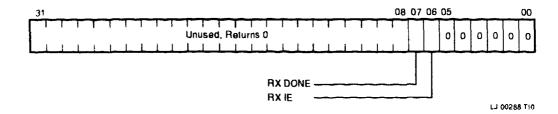

| 3.12.1.1 Console Receiver Control/Status Register (RXCS)    | 3-42 |

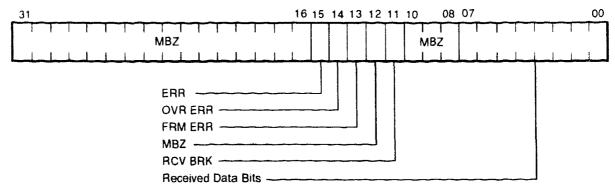

| 3.12.1.2 Console Receiver Data Buffer (RXDB)                | 3-43 |

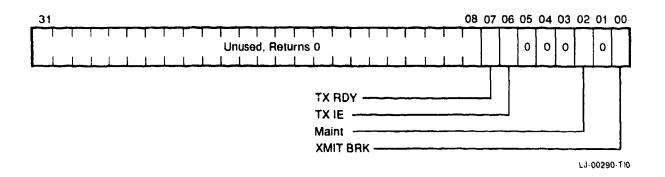

| 3.12.1.3 Console Transmitter Control/Status Register (TXCS) | 3-44 |

| 3.12.1.4 Console Transmitter Data Buffer (TXDB)             | 3-45 |

| 3.12.2 Break Response                                       | 3-46 |

| 3.12.3 Baud Rate                                            | 3-46 |

| 3.12.4 Console Interrupt Specifications                     | 3-47 |

| 3.13 KN220-AA TODR Clock and Timers                         | 3-47 |

| 3.13.1 R3000 Interval Timer Register (ITR)                  | 3-47 |

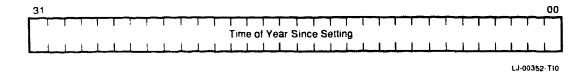

| 3.13.2 Time-of-Year Clock                                   | 3-48 |

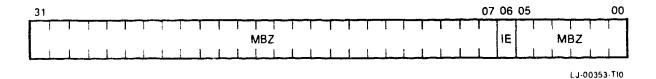

| 3.13.3 Interval Timer (ICCS)                                |      |

| 3.13.4 Programmable Timers                                 | 3-49 |

|------------------------------------------------------------|------|

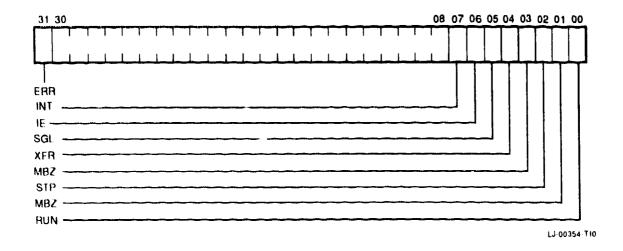

| 3.13.4.1 Timer Control Registers (TCR0-TCR1)               | 3-49 |

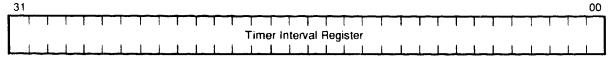

| 3.13.4.2 Timer Interval Registers (TIR0-TIR1)              | 3-51 |

| 3.13.4.3 Timer Next Interval Registers (TNIR0-TNIR1)       | 3-51 |

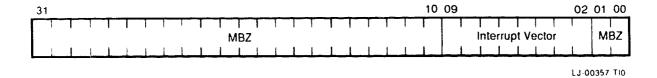

| 3.13.4.4 Timer Interrupt Vector Registers (TIVR0-TIVR1)    | 3-52 |

| 3.14 KN220-AA Network Interface                            | 3-52 |

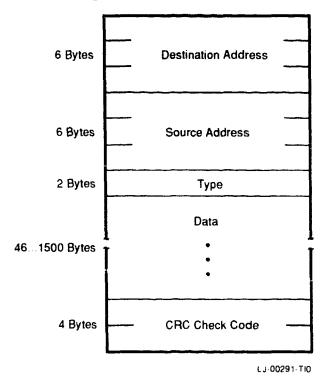

| 3.14.1 Ethernet Overview                                   | 3-53 |

| 3.14.2 NI Station Address ROM (NISA ROM)                   | 3–54 |

| 3.15 Programming                                           | 3-55 |

| 3 16 Programming Overview                                  | 3-55 |

| 3.17 Command and Status Registers                          | 3-56 |

| 3.17.1 Host access to CSRs                                 | 3-56 |

| 3.17.1.1 Physical CSRs                                     | 3-57 |

| 3.17.1.2 Virtual CSRs                                      | 3-57 |

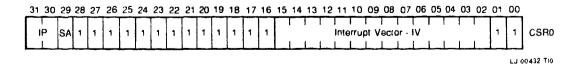

| 3.17.2 Vector Address, IPL, Sync/Asynch (CSR0)             | 3-57 |

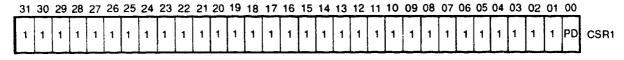

| 3.17.3 Transmit Polling Demand (CSR1)                      | 3-59 |

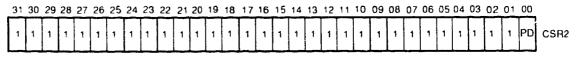

| 3.17.4 Receive Polling Demand (CSR2)                       | 3-59 |

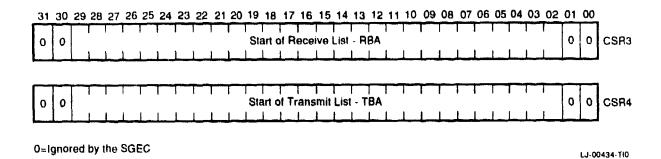

| 3.17.5 Descriptor List addresses (CSR3, CSR4)              | 3-60 |

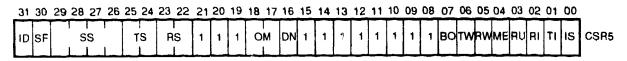

| 3.17.6 Status Register (CSR5)                              | 3-62 |

| 3.17.6.1 CSR5 Status Report                                | 3-66 |

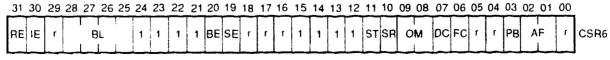

| 3.17.7 Command and Mode Register (CSR6)                    | 3-66 |

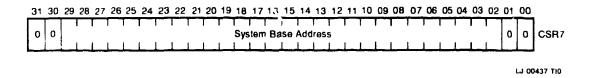

| 3.17.8 System Base Register (CSR7)                         | 3-71 |

| 3.17.9 Reserved Register (CSR8)                            | 3-72 |

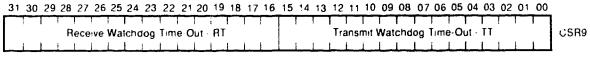

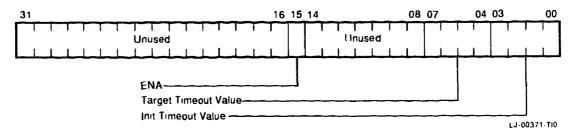

| 3.17.10 Watchdog Timers (CSR9)                             | 3-72 |

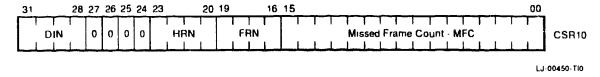

| 3.17.11 SGEC Identification and Missed Frame Count (CSR10) | 3-74 |

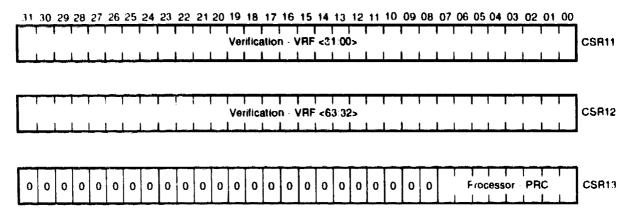

| 3.17.12 Boot Message (CSR11, 12, 13)                       | 3-75 |

| 3.17.13 Diagnostic Registers (CSR14, 15)                   | 3-75 |

| 3.18 Descriptors and Buffers Format                        | 3-76 |

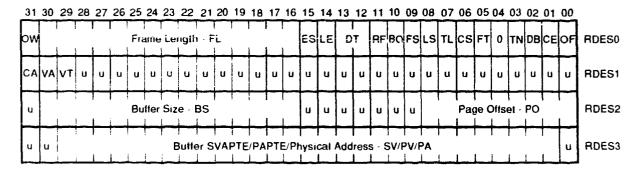

| 3.18.1 Receive Descriptors                                 | 3-76 |

| 3.18.1.1 RDES0 Word                                        | 3-77 |

| 3.18.1.2 RDES1 Word                                        | 3-79 |

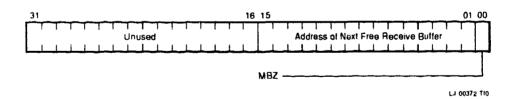

| 3.18.1.3 RDES2 Word                                        | 3-79 |

| 3.18.1.4 RDES3 Word                                        | 3-80 |

| 3.18.1.5 Receive Descriptor Status Validity                | 3-80 |

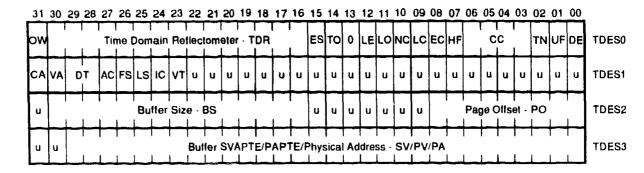

| 3.18.2 Transmit Descriptors                                | 3-81 |

| 3.18.2.1 TDES0 Word                                        | 3-81 |

| 3.18.2.2 TDES1 Word                                        | 3-83 |

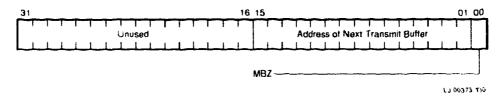

| 3.18.2.3 TDES2 Word                                        | 3-84 |

| 3.18.2.4 TDES3 Word                                        | 3-85 |

| 3.18.2.5 Transmit Descriptor Status Validity               | 3-85 |

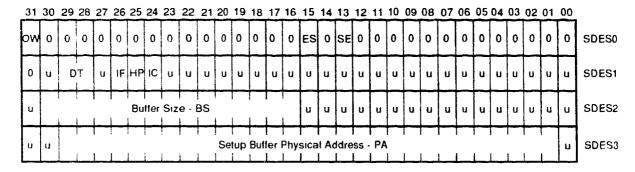

| 3.18.3               | Setup Frame                                  | 3-86         |

|----------------------|----------------------------------------------|--------------|

| 3.18.3.1             | First Setup Frame                            | 3–86         |

| 3.18.3.2             | Subsequent Setup Frame                       | 3–86         |

| 3,18,3,3<br>3,18,3,4 | Setup Frame Descriptor                       | 3-86         |

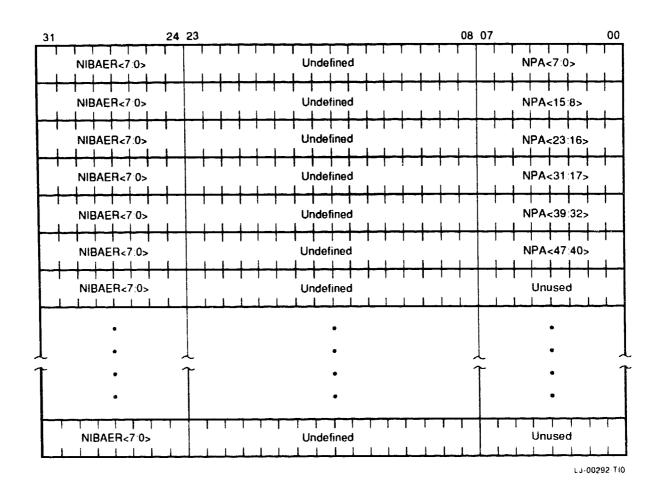

| 3.18.3.5             | Imperfect Filtering Setup Frame Buffer       | 3–87         |

|                      |                                              | 3–89         |

|                      | GEC Operation                                | 3–91         |

| 3.19.1               | Hardware and Software Reset                  | 3-91         |

| 3.19.2<br>3.19.3     | Interrupts                                   | 3–92         |

| 3.19.4               | Startup Procedure                            | 3-93         |

| 3.19.5               | Reception Process                            | 3-93         |

| 3.19.6               | Loopback Operations                          | 3–95<br>3–97 |

|                      |                                              |              |

|                      | NA CSMA/CD Counters and Events Support       | 3–98         |

| 3.21 K               | N220-AA Q22-bus Interface                    |              |

| 3.21.1               | Q22-bus to Main Memory Address Translation   |              |

| 3.21.1.1             | Q22-bus Map Registers (QMRs)                 |              |

| 3.21.1.2             | Accessing the Q22-bus Map Registers          |              |

| 3.21.1.3             | The Q22-bus Map Cache                        |              |

| 3.21.2               | CDAL Bus to Q22-bus Address Translation      |              |

| 3.21.3               | Interprocessor Communications Facility       |              |

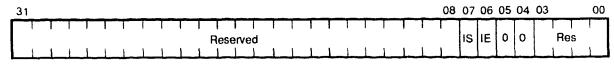

| 3.21.3.1             | Interprocessor Communication Register (IPCR) |              |

| 3.21.3.2             |                                              |              |

| 3.21.4               | Q22-bus Interrupt Handling                   |              |

| 3.21.5 $3.21.5.1$    | Configuring the Q22-bus Map                  |              |

| 3.21.6.1 $3.21.6$    | Q22-bus Map Base Address Register (QBMBR)    |              |

| 3.21.0 $3.21.7$      | System Configuration Register (SCR)          |              |

| 3.21.7               | Q22-bus Error Address Register (QBEAR)       |              |

| 3.21.9               | DMA Error Address Register (DEAR)            |              |

| 3.21.10              | Error Handling                               |              |

|                      |                                              |              |

| 3.22 K<br>3.22.1     | N220-AA Diagnostic Processor                 |              |

| 3.22.1.1             | Interrupts And Exceptions                    |              |

| 3.22.1.1             |                                              |              |

|                      |                                              |              |

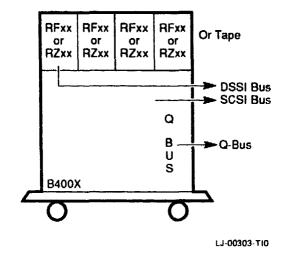

|                      | N220-AA Mass Storage Interfaces              |              |

| 3.23.1               | DSSI Bus Interface                           |              |

| J.23.1.1             |                                              |              |

| 3.23.1.2             | 8 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 -      |              |

| 3.23.1.3             | •                                            |              |

| 3.23.1.4             |                                              |              |

| 3.23.1.5             | , . , . , . , . , . , . , . , . , .          |              |

| -3.23.1.6            | DSSI Registers                               | 3 - 127      |

|   | 3.23.2 SCSI Bus Interface                       | 3141 |

|---|-------------------------------------------------|------|

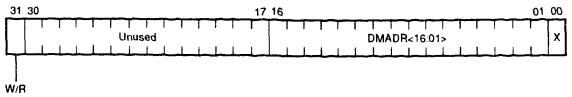

|   | 3.23.2.1 DMA Address Register - DMAAR           |      |

|   | 3.23.2.2 DMA Buffer RAM - DMABR                 |      |

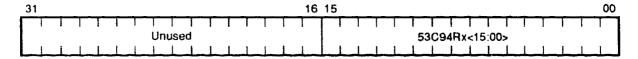

|   | 3.23.2.3 53C94 Registers - 53C94Rx              |      |

|   |                                                 |      |

| 4 | Firmware Specification                          |      |

|   | 4.1 Environment                                 | 4–1  |

|   | 4.1.1 Users                                     | 4-1  |

|   | 4.1.2 Hardware                                  | 4-1  |

|   | 4.1.3 Software                                  | 4-2  |

|   | 4.1.4 Services                                  | 4-2  |

|   | 4.2 Firmware Capabilities                       | 4-2  |

|   | 4.3 Power up                                    | 4-2  |

|   | 4.3.1 Processor Select                          | 4–2  |

|   | 4.3.2 CVAX Initial Power-Up Test                | 4-3  |

|   | 4.3.3 Locating a Console Device                 | 4-4  |

|   | 4.3.4 CVAX Operation and Function Switches      | 4-4  |

|   | 4.3.4.1 Operation Switch Set to Normal          | 4-4  |

|   | 4.3.4.2 Operation Switch Set to Maintenance     | 4-5  |

|   | 4.3.4.3 Operation Switch Set to Action          | 4-5  |

|   | 4.3.4.4 LED Codes                               | 46   |

|   | 4.3.5 R3000 Initial Power-Up Test               | 4_7  |

|   | 4.3.6 R3000 Operation and Function Switches     | 4-7  |

|   | 4.3.6.1 Operation Switch Set to Normal/Secure   | 4-7  |

|   | 4.3.6.2 Operation Switch Set to Maintenance     | 4-8  |

|   | 4.3.6.3 Operation Switch Set to Action          | 4-8  |

|   | 4.3.7 Interprocessor Interaction                | 4-8  |

|   | 4.3.7.1 Select Processor Register (SPR)         | 4-8  |

|   | 4.3.8 Power-Up Sequence                         | 48   |

|   | 4.3.8.1 Normal Power-Up Operation               | 4-9  |

|   | 4.3.8.2 Maintenance Power-Up Operation          | 4_9  |

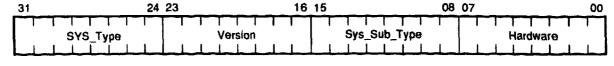

|   | 4.3.9 Processor Identification                  | 4-9  |

|   | 4.3.9.1 R3000 Sys_Type Environment Variable     | 4-9  |

|   | 4.3.9.2 CVAX Sys_Type Register Layout           | 4-10 |

|   | 4.4 Operating System Bootstrap                  | 4-10 |

|   | 4.4.1 MDM Bootstrap                             | 4-10 |

|   | 4.4.2 Operating System Bootstrap                | 4-11 |

|   | 4.4.3 Boot Process                              | 4–11 |

|   | 4.4.4 Bootstrap Support Routines in the Console | 4-12 |

|   | 4.4.5 Console Use of Memory Space               | 4-13 |

|   | 4.4.6 Boot Devices                              | 4-13 |

|   | 4.4.6.1 Disk                                    | 4-14 |

|   | 4.4.6.2 Tape                                    | 4-14 |

|   | 4.4.6.3 Ethernet                                | 4–14 |

|   | 4.4.7 Halta                                     | 1_14 |

|   | 4.5 KN220-AA Console Language and Security Features                           | 4-15       |

|---|-------------------------------------------------------------------------------|------------|

|   | 4.5.1 Console Security Features                                               | 4-15       |

|   | 4.5.2 Console Security Commands                                               | 4-16       |

|   | 4.5.2.1 Password Command                                                      | 4-17       |

|   | 4.5.3 Maintenance Mode Console Command Language                               | 4-17       |

|   | 4.5.4 Normal Mode Console Command Language                                    | 4-17       |

|   | 4.5.4.1 Control Characters                                                    | 4-17       |

|   | 4.5.4.2 Lexical Conventions                                                   | 4-18       |

|   | 4.5.4.3 Environment Variables                                                 | 4-18       |

|   | 4.5.4.4 Commands                                                              | 4–19       |

|   | 4.6 Diagnostics                                                               | 4-22       |

|   | 4.6.1 Error Reporting                                                         | 4-22       |

|   | 4.6.2 Diagnostic Interdependencies                                            | 4–24       |

| 5 | System Specification                                                          |            |

|   | 5.1 Introduction                                                              | 5–1        |

|   |                                                                               |            |

|   | 5.2 General Description                                                       | 5-1<br>5-1 |

|   | •                                                                             |            |

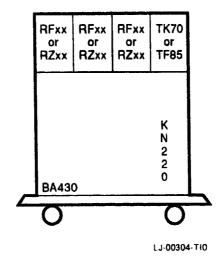

|   | 5.2.1.1 Pedestal Systems                                                      | 5–2<br>5–2 |

|   |                                                                               |            |

|   | 5.3 220QH System Base Components                                              | 5–2        |

|   | 5.3.1 220QH System Building Block                                             | 5–2        |

|   | 5.3.1.1 Hardware Support Kits                                                 | 5-4        |

|   | 5.3.1.2 Power Cords                                                           | 55         |

|   | 5.3.2 220QH Physical Specifications                                           | 5-5        |

|   | 5.3.3 220QH Electrical Specifications                                         | 5–6        |

|   | 5.3.4 220QH Environmental Specifications                                      | 56         |

|   | 5.3.4.1 220QH Temperature/Humidity Specifications                             | 56         |

|   | 5.4 220QF System Base Components                                              | 56         |

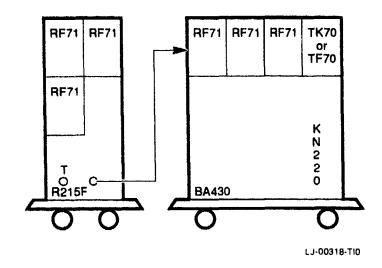

|   | 5.4.1 220QF System Upgrade                                                    | 56         |

|   | 5.4.1.1 Hardware Support Kits                                                 | 5–8        |

|   | 5.4.1.2 220QF Power Cords                                                     | 5–9        |

|   | 5.4.2 220QF Physical Specifications                                           | 5-9        |

|   | 5.4.3 220QF Electrical Specifications                                         | 5–9        |

|   | 5.4.3.1 220QF DC Output Specifications                                        | 5-9        |

|   | 5.4.3.2 220QF AC Input Specifications                                         | 5–9        |

|   | 5.4.3.3 Power Supplies and Power Controller                                   | 5-12       |

|   | 5.4.4 220QF Environmental Specifications                                      | 5–13       |

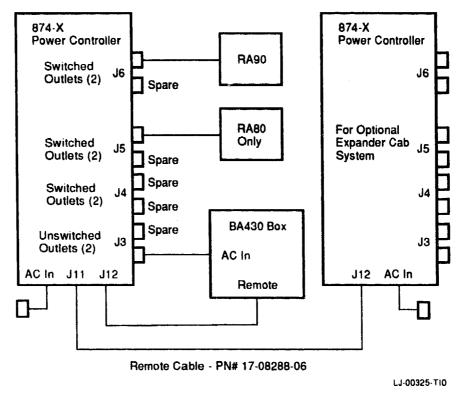

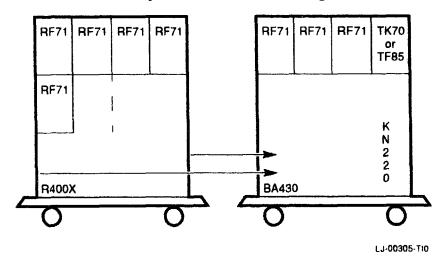

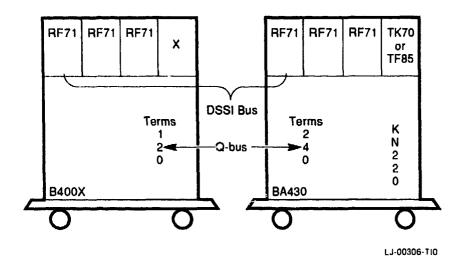

|   | 5.5 Expansion Cabinet Systems                                                 |            |

|   | 5.5.1 DSSI Expansion Enclosures                                               | 5-14       |

|   | 5.5.2 DSSI Based DU-55xxx Configurations and Possible Expanded Configurations | 5-15       |

|   | 5.5.3 DU-55xxx RA Based Cabinet Systems and Expansion Paths                   |            |

|   | 5.5.4 Expansion Cabinet Specifications                                        |            |

### x Contents

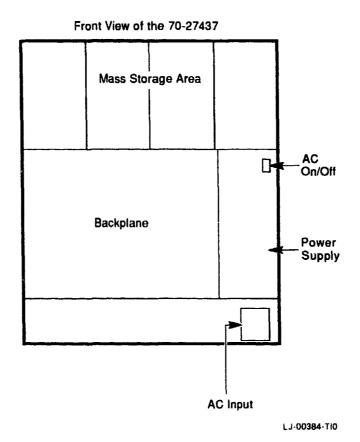

|   | 5.6 BA430 Enclosure Specifications             | 5-20         |

|---|------------------------------------------------|--------------|

|   | 5.6.1 General Description                      | 5-20         |

|   | 5.6.1.1 Mass Storage                           | 5-21         |

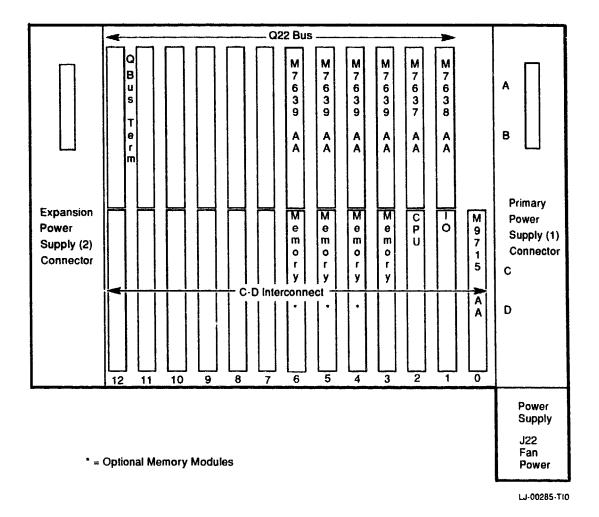

|   | 5.6.1.2 Backplane Specifications               | 5-22         |

|   | 5.6.1.3 Power Supply Specifications            | 5-24         |

|   | 5.6.1.4 DC Power Supply Specification          | 5-24         |

|   | 5.6.1.5 AC Input Specification                 | 5-25         |

|   | 5.7 BA213 Enclosure Specifications             | 5-29         |

|   | 5.7.1 General Description                      | 5-29         |

|   | 5.7.1.1 Mass Storage                           | 5-30         |

|   | 5.7.1.2 Backplane Specifications               | 5-31         |

|   | 5.7.1.3 Power Supply Specifications            | 5-33         |

|   | 5.7.1.4 DC Power Supply Specification          | 5-33         |

|   | 5.7.1.5 AC Input Specification                 | 5-35         |

|   | 5.8 KN220 Processor Specifications             | 5-40         |

|   | 5.9 MS220-AA Memory Module Specifications      | 5-44         |

|   | 5.9.1 MS220-AA                                 | 5-44         |

|   | 5.10 Disk Drive Specifications                 | 5-46         |

|   | 5.10.1 RF71-A Fixed Disk Drive Specifications  | 5-46         |

|   | 5.10.2 RZ56-FA Fixed Disk Drive Specifications | 5-47         |

|   | 5.11 Tape Drive Specifications                 |              |

|   | 5.11.1 TK70-A Tape Drive Specifications        | 5–50<br>5–50 |

|   |                                                |              |

|   | 5.12 Mass Storage Controller Specifications    | 5–52         |

|   |                                                |              |

|   | 5.13 Communication Device Specifications       | 5–54         |

|   | 5.13.1 Asynchronous Communication Devices      | 5–54         |

|   | 5.13.1.1 CXA16-AA                              | 5–54         |

|   | 5.13.1.2 CXB16-AA                              | 5–56         |

|   |                                                | 5–59         |

|   | 5.14 Line Printer Interface Specifications     |              |

|   | 5.14.1 SCSI Bus Interface                      | 5–64         |

|   |                                                |              |

| 1 | Q22-bus Specification                          |              |

|   | A.1 Introduction                               | A-1          |

|   | A.1.1 Master/Slave Relationship                | A-2          |

|   | A.2 Q22-bus Signal Assignments                 | A-2          |

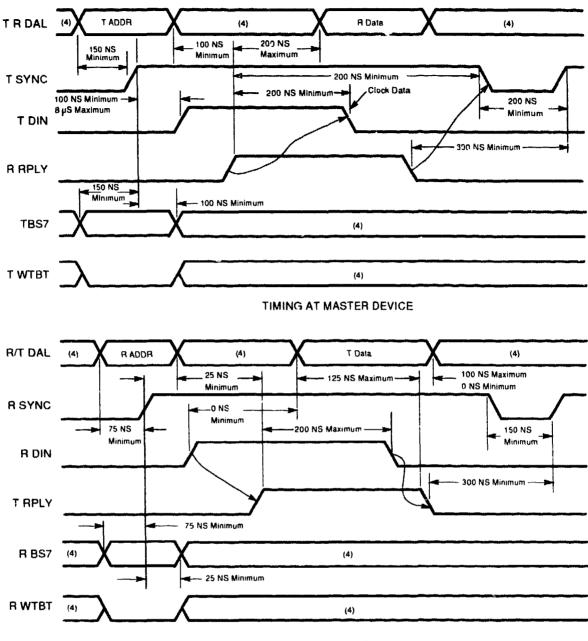

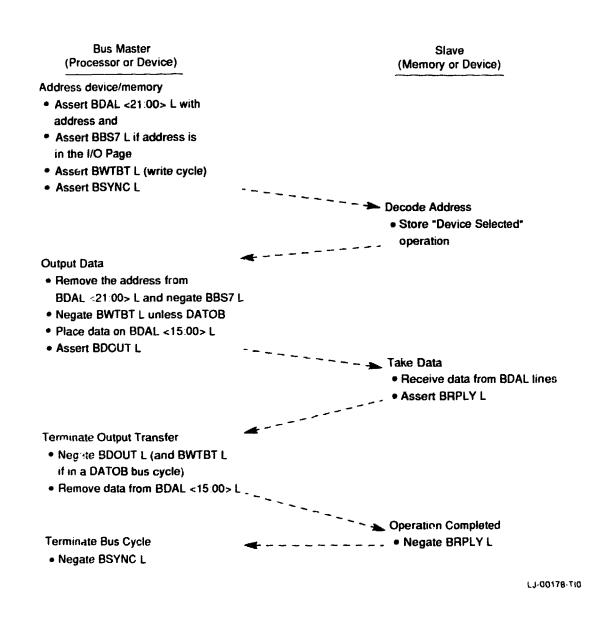

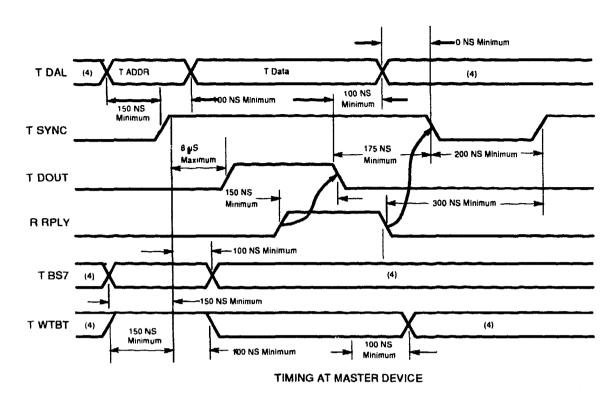

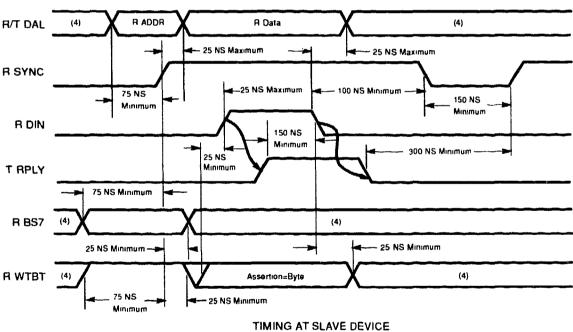

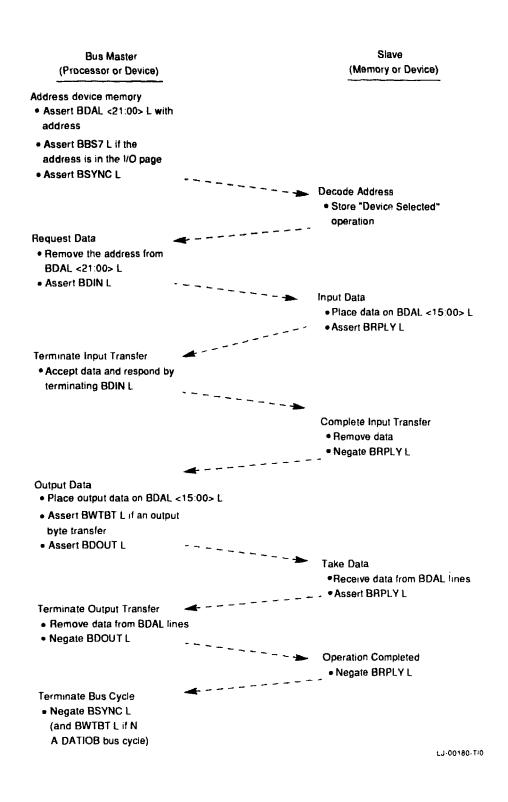

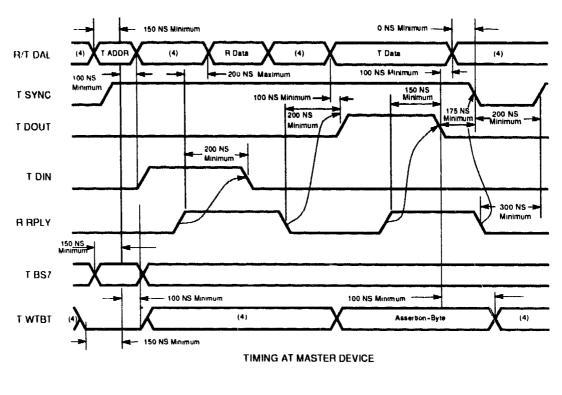

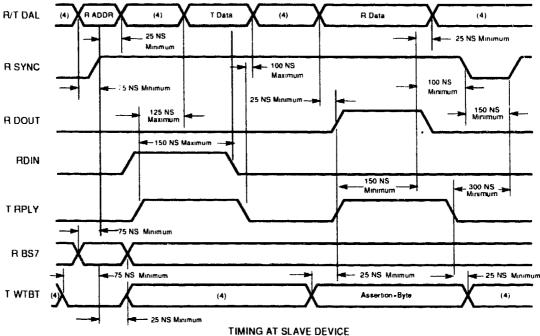

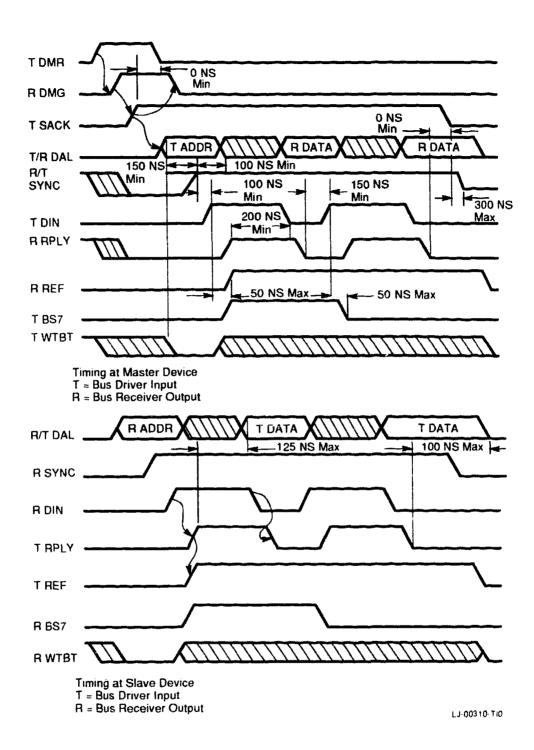

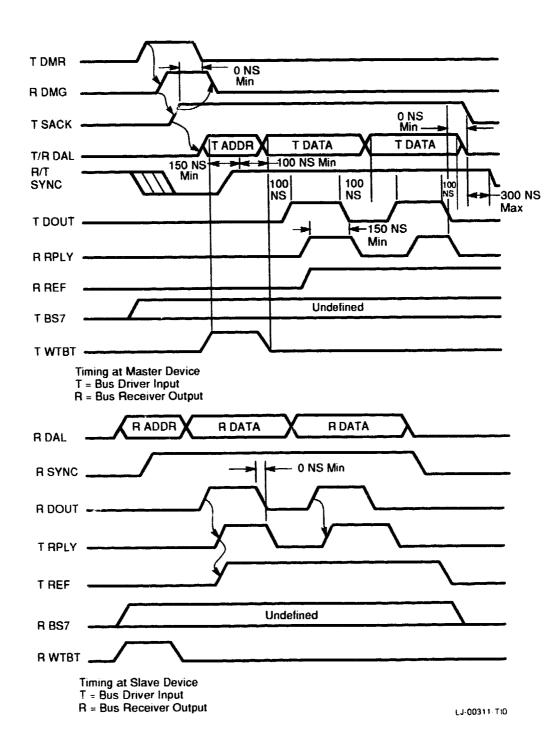

|   | A.3 Data Transfer Bus Cycles                   | A-5          |

|   | A.3.1 Bus Cycle Protocol                       | A-6          |

|   | A.3.2 Device Addressing                        | A-6          |

|   |                                                |              |

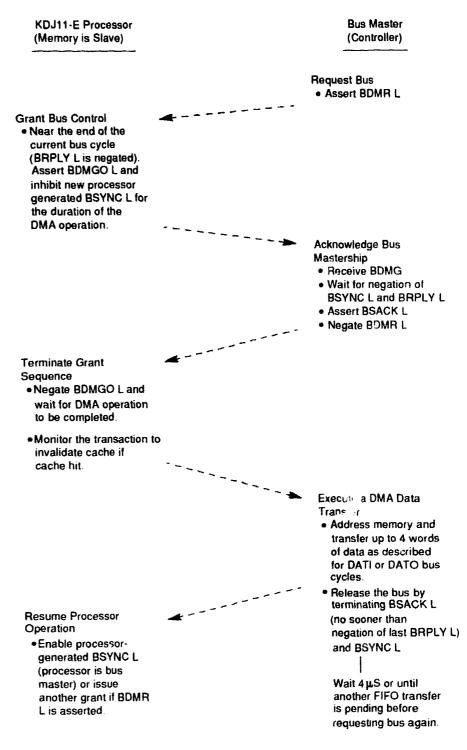

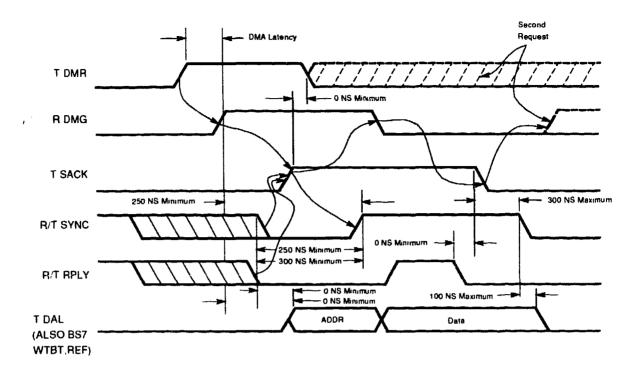

|   | A.4.1 DMA Protocol                             | A-16         |

|   | A. A.A. DAMA I IVIUCUI                         | A-16         |

|   | A.4.2.<br>A.4.2.<br>A.4.3                                                                       |                                                                                              | A-22<br>A-23                                                 |

|---|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------|

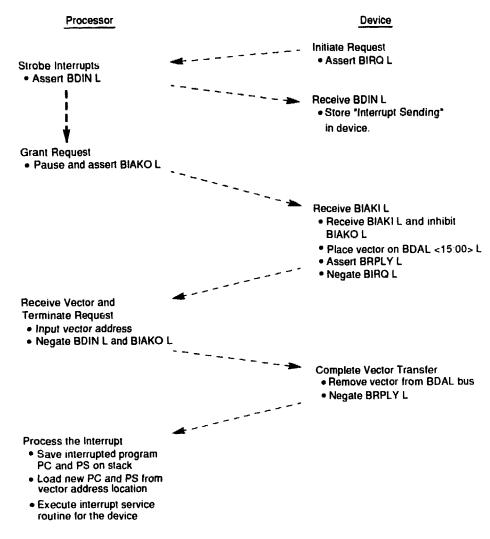

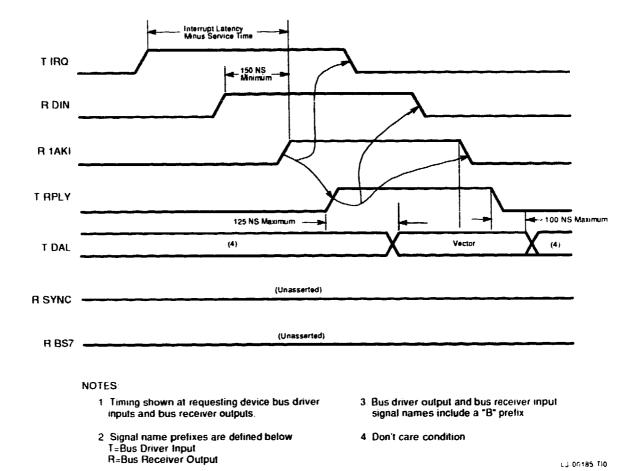

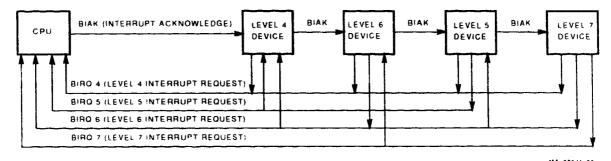

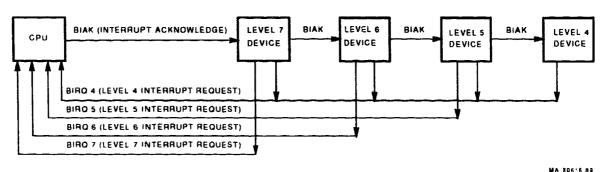

|   | A.5.1<br>A.5.2<br>A.5.3                                                                         | Interrupts  Device Priority  Interrupt Protocol  Q22-bus Four-Level Interrupt Configurations | A-26<br>A-26                                                 |

|   | A.6.1<br>A.6.2<br>A.6.3                                                                         | Control Functions                                                                            | A-31<br>A-32                                                 |

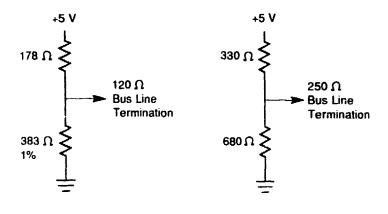

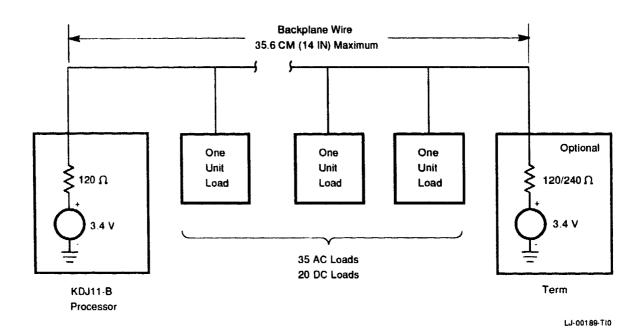

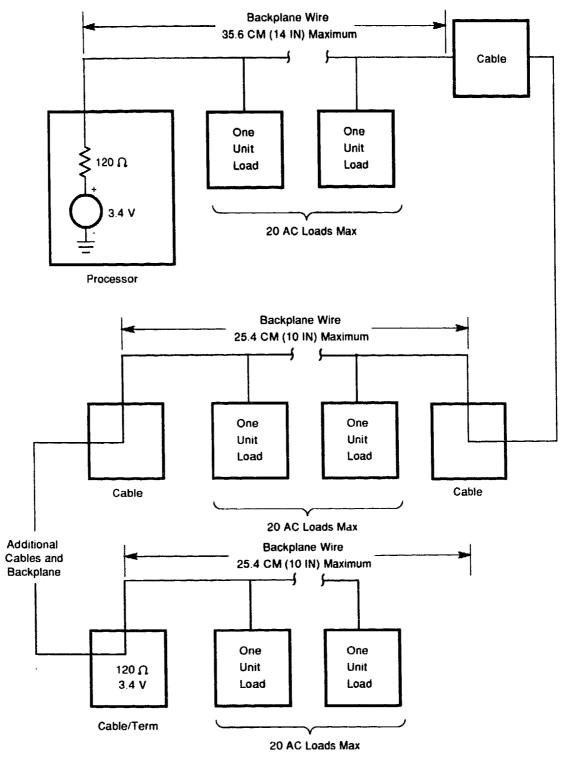

|   | A.7<br>A.7.1<br>A.7.2<br>A.7.3<br>A.7.4<br>A.7.5<br>A.7.6<br>A.7.7<br>A.7.7<br>A.7.7.<br>A.7.7. | 2 Intrabackplane Bus Wiring                                                                  | A-32<br>A-32<br>A-33<br>A-33<br>A-34<br>A-35<br>A-35<br>A-35 |

|   | A.8.1<br>A.9                                                                                    | Power Supply Loading                                                                         | A-40                                                         |

| В | •                                                                                               | cifications                                                                                  |                                                              |

|   | B.1                                                                                             | KN220-AA Physical Specifications (pinouts/connectors)                                        | B-1                                                          |

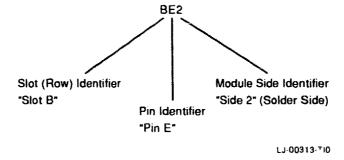

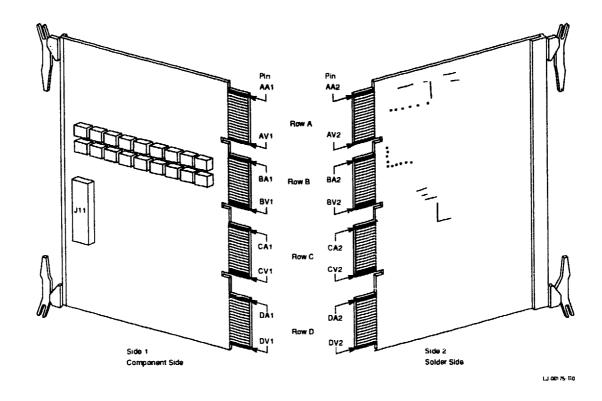

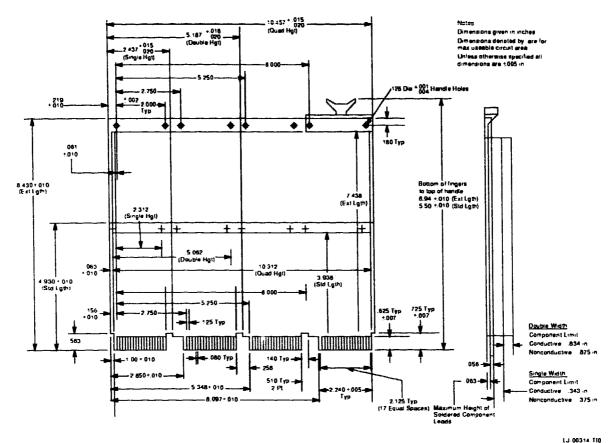

|   | B.2<br>B.3<br>B.3.1<br>B.3.2<br>B.3.3                                                           | KN220-AA C/D Row Fingers and RIO Connector                                                   | B-1<br>B-1<br>B-1<br>B-2<br>B-4                              |

|   | <b>B</b> .4                                                                                     | KN220-AA Environmental and Reliability Specifications                                        | B-6                                                          |

|   | <b>B.5</b>                                                                                      | Operating Conditions                                                                         | B-6                                                          |

|   | B.6                                                                                             | Non-Operating Conditions (Less than 60 days)                                                 | B-7                                                          |

|   | <b>B</b> .7                                                                                     | Non-Operating Conditions (Greater than 60 days)                                              | B-7                                                          |

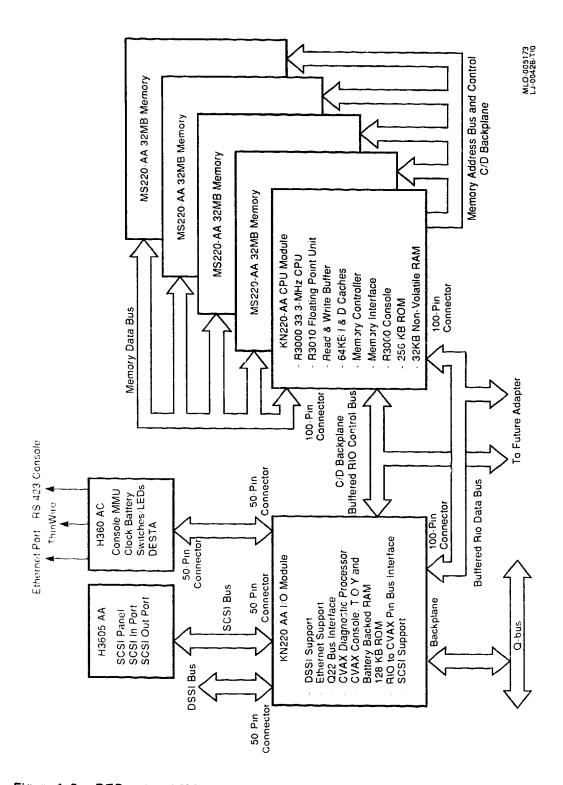

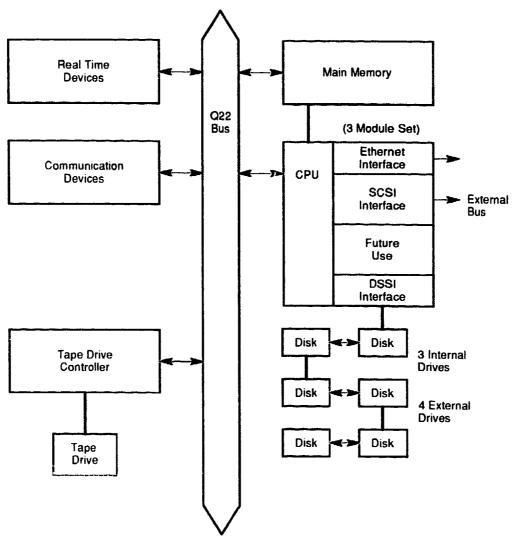

| C | Sys         | tem Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|---|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | C.1         | System Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | C-1 |

| _ | Dua         | m Futur Deinte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| D |             | m Entry Points                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|   | D.1         | Prom Entry Points                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | D-1 |

|   | <b>D.2</b>  | Argvize                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | D-1 |

|   | <b>D.3</b>  | Atob                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | D-1 |

|   | D.4         | Autoboot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | D-1 |

|   | <b>D</b> .5 | Bevexcept                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | D-2 |

|   | D.6         | Bevutlb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | D-2 |

|   | <b>D</b> .7 | Close                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | D-2 |

|   | <b>D</b> .8 | Dumpemd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | D-2 |

|   | D.9         | Exec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | D-2 |

|   | D.10        | Getchar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | D-2 |

|   | D.11        | Getenv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | D-3 |

|   | D.12        | 2 Gets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | D-3 |

|   | D.13        | Halt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | D-3 |

|   | D.14        | Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | D-3 |

|   | D.18        | 5 loctl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | D-3 |

|   | D.16        | 6 Longjump                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D-3 |

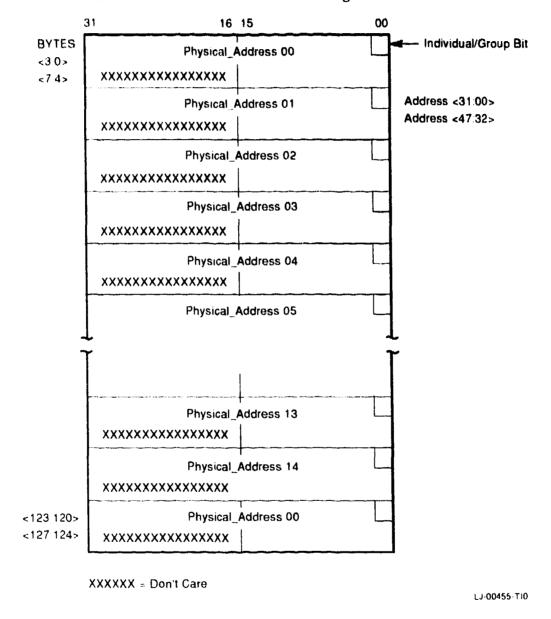

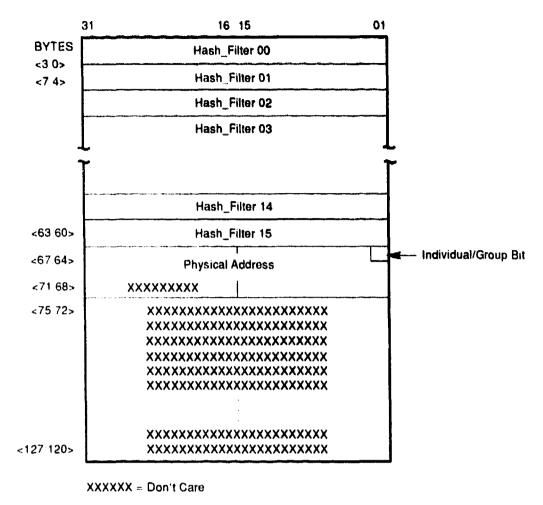

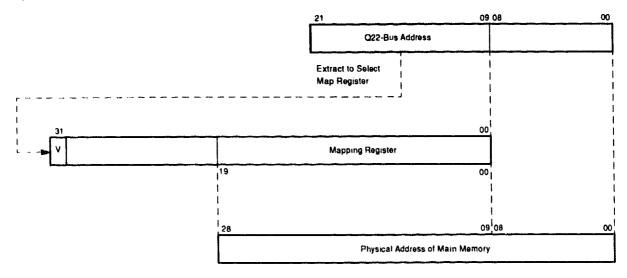

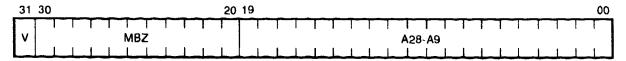

|   | D.1         | 7 Lseek                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | D-4 |