## CITCA

# Installation and Operating Information

Order Number: EK-CITCA-OM. 001

#### August 1992

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

No responsibility is assumed for the use or reliability of software on equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Restricted Rights: Use, duplication, or disclosure by the U.S. Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

© Digital Equipment Corporation 1992.

All Rights Reserved.

DEC, DEC<br/>station, DECsystem, TURBOchannel, ULTRIX, and the Digital logo are trade<br/>marks of Digital Equipment Corporation.

This document was prepared using VAX DOCUMENT, Version 2.0.

## Contents

| Αl | bout Th | out This Manual             |      |

|----|---------|-----------------------------|------|

| 1  | Introd  | uction                      |      |

|    | 1.1     | General Description         | 1–1  |

|    | 1.2     | Physical Description        | 1–2  |

|    | 1.2.1   | Components                  | 1–2  |

|    | 1.2.2   | Logic Components            | 1–3  |

|    | 1.3     | Features                    | 1–4  |

|    | 1.4     | Specifications              | 1–5  |

| 2  | Site P  | reparation and Installation |      |

|    | 2.1     | Site Preparation            | 2–1  |

|    | 2.2     | Module Setup                | 2–2  |

|    | 2.2.1   | Switchpack 1                | 2–4  |

|    | 2.2.2   | Switchpack 2                | 2–7  |

|    | 2.2.3   | Switchpack 3                | 2–8  |

|    | 2.2.4   | CI Cable Routing            | 2–11 |

|    | 2.3     | Installation                | 2–12 |

|    | 2.3.1   | Removing a CITCA            | 2–16 |

| 3  | Verific | ation and Acceptance        |      |

|    | 3.1     | Verification Procedure      | 3–1  |

|    | 3.2     | Troubleshooting             | 3–5  |

|    | 3.3     | Booting from CITCA          | 3–9  |

|    | 331     | Boot Errors                 | 3–9  |

#### Diagnostics TCAST 4.1 4-1 4.1.1 4-2 4.1.2 Running TCAST..... 4-2 4.1.3 Interpreting Error Information ...... 4-3 PST ..... 4.2 4-4 4.2.1 4-4 4.2.2 Running the CITCA Subtest ..... 4-5 4.2.3 Interpreting Error Information ...... 4-5 4.3 4-6 4.3.1 CI External Loopback Test..... 4-6 4.3.1.1 Connecting the CI Attenuator/Loopback Connectors . . . . 4-6 4.3.1.2 Program Execution..... 4-7 4.3.2 4-9 4.4 FLASH\_CITCA ..... 4-10 4.4.1 FLASH\_CITCA Tests and Utilities ...... 4-10 4.4.1.1 4-11 4.4.1.2 4-12 4.4.2 Loading FLASH\_CITCA..... 4-14 4.4.2.1 Booting the FLASH\_CITCA Program Image . . . . . . . . . 4-14 4.4.2.2 Booting the System Console Program Image . . . . . . . . . 4-15 4.4.2.3 4-16 4.4.3 4-16 Running FLASH\_CITCA ..... 4.4.4 4-18 4.4.5 4-19 4.4.6 4-19 4.4.7 4-19 4.4.8 4-20 5 Functional Description 5.1 5-15.2 5-4 5.2.1 Sending a Packet to a CI Node ...... 5-4 5.2.2 5-6

| A Reg      | isters                             |

|------------|------------------------------------|

| A.1<br>A.2 | Register Addressing                |

| В Вос      | t Errors                           |

| B.1<br>B.2 | What to Do                         |

| C Par      | Numbers                            |

| Index      |                                    |

| Examp      | les                                |

| 3–1        | Using the cnfg Command             |

| 3–2        | Boot n/l                           |

| 3–3        | Using the <i>cnfg n</i> Command    |

| 4–1        | Running the pdflt Subtest          |

| 4-2        | CI External Loopback Test — Passed |

| 4–3        | CI External Loopback Test — Failed |

| 4–4        | CI Node Configuration Test         |

| 4–5        | Loading FLASH_CITCA Program Image  |

| 4–6        | Loading the System Program Image   |

| 4–7        | Overlay ROM Objects                |

| 4–8        | Running FLASH_CITCA                |

| 4–9        | Selecting the TURBOchannel Slot    |

| 4–1        | 0 Running Test 3                   |

| 4–1        |                                    |

| 4–1        | 2 Updating the FLASH PROM          |

| A-1        | 88                                 |

| B-′        | Console Output of a Boot Failure   |

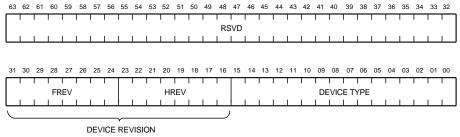

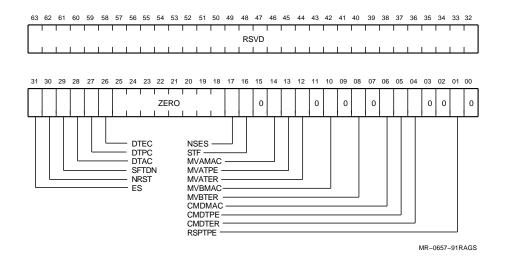

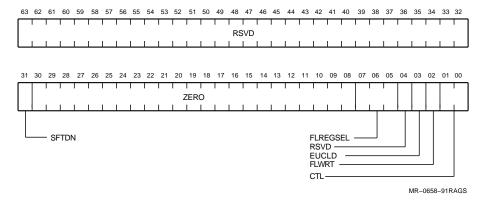

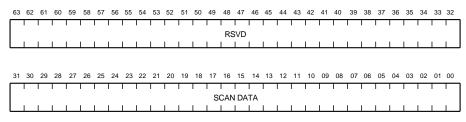

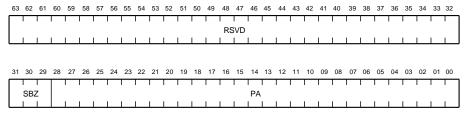

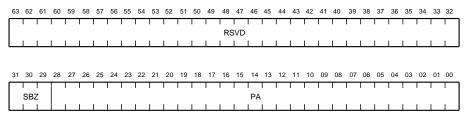

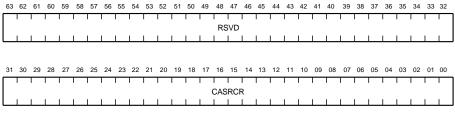

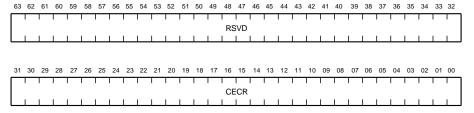

#### **Figures** 1-1 Simplified CITCA Connection ..... 1-2 1-2 Hardware Components..... 1-3 2-1 2-4 2-2 2-12 2-3 2 - 142-4 2 - 152-5 Module Removal..... 2 - 173-1 3-2 3-2 3-4 3-3 Installation Verification/Troubleshooting Flowchart (Part 1 of 3-6 Installation Verification/Troubleshooting Flowchart (Part 2 of 3 - 43-7 4-1 Location of CITCA Self-Test Passed LED..... 4-3 4-2 4-7 Connecting the CI Attenuator/Loopback Connectors . . . . . . 5-1 CITCA Simplified Block Diagram ...... 5-2 5-2 5-2 A-1 TURBOchannel Device Register (TDEV) ...... A-3 A-2TURBOchannel Bus Error Register (TBER) ...... A-6 A-3 8-A Port Scan Control Register (PSCR) ...... A-4A-10 A-5Port Diagnostic Control/Status Register (PDCSR) . . . . . . . . A - 11A-6 Channel/Adapter Status Register (CASR) ...... A-13 A-7 Channel/Adapter Failing Address Register (CAFAR) . . . . . . . A-15 8-A Adapter Serial Number Register (ASNR)...... A-16 A-9 Adapter Block Base Register (ABBR)....... A - 17A-10 Channel Command Queue 2 Insertion Register (CCQ2IR)... A-18 A-11 Channel Command Queue 1 Insertion Register (CCQ1IR)... A-19 A-12 Channel Command Queue 0 Insertion Register (CCQ0IR)... A-20 A - 13Adapter Datagram Free Queue Insertion Register A-21 (ADFQIR)...... A - 14Adapter Message Free Queue Insertion Register A - 22A-15 Channel/Adapter Status Release Control Register A-23

A - 23

A-16

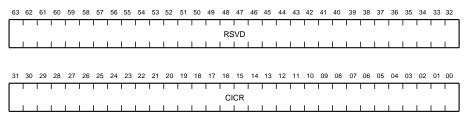

| A-17          | Port Initialize Control Register (CICR)                                        | A-2      |

|---------------|--------------------------------------------------------------------------------|----------|

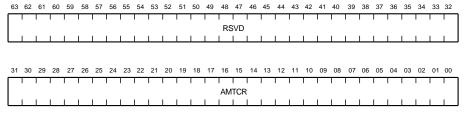

| A-18          | Adapter Maintenance/Sanity Timer Control Register (AMTCR)                      | A-2      |

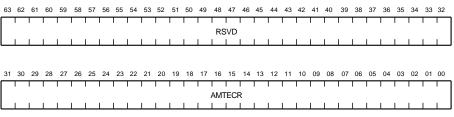

| A-19          | Adapter Maintenance/Sanity Timer Expiration Control Register (AMTECR)          | A-2      |

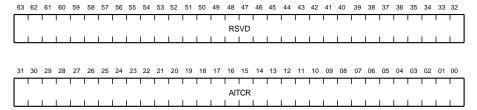

| A-20          | Adapter Interrupt Holdoff Timer Control Register (AITCR)                       | A-2      |

| A-21          | Adapter Maintenance Control/Status Register (AMCSR)                            | A-2      |

| <b>Tables</b> |                                                                                |          |

| 1             | Related Documents                                                              |          |

| 1–1           | CITCA Hardware Components                                                      | 1-       |

| 1–2           | Environmental Specifications                                                   | 1-       |

| 1–3           | Electrical Specifications                                                      | 1-       |

| 2–1           | Summary of Switch Settings                                                     | 2-       |

| 2–2           | Switchpack 1 - Switch 1                                                        | 2-       |

| 2–3           | Switchpack 1 - Switch 2                                                        | 2-       |

| 2–4           | Switchpack 1 - Switches 3 through 10 and Switchpack 2 -                        |          |

|               | Switches 3 through 10                                                          | 2-       |

| 2–5           | Switchpack 2 - Switch 1                                                        | 2-       |

| 2–6           | Switchpack 2 - Switch 2                                                        | 2-       |

| 2–7           | Switchpack 3 - Switches 1 through 3, Quiet Slot Time<br>Configuration Switches | 2-       |

| 2–8           | Switchpack 3 - Switches 4 through 6                                            | 2-       |

| 2–9           | Switchpack 3 - Switches 4 through 10                                           | 2-       |

| 3–1           | PDFLT Codes                                                                    | 3-       |

| 4–1           | TCAST Pass/Fail Information                                                    | 4-       |

| 4–2           | PDFLT Codes                                                                    | 4-       |

| 4–3           | FLASH_CITCA Event Flags                                                        | 4-       |

| A–1           | CITCA Register List                                                            | -т<br>А- |

| A-2           | TDEV Bit Description                                                           | A-       |

| A-4           | TBER Bit Description                                                           | A-       |

| A-5           | PCSR Bit Description                                                           | A-       |

| A–7           | PSDR Bit Description                                                           | A-       |

| A–8           | PDCSR Bit Description                                                          | A-       |

| A-9           | CASR Bit Description                                                           | A-       |

| A-10          | CAFAR Bit Description                                                          | A-       |

|               |                                                                                |          |

| A-11 | ASNR Bit Description    | A-16 |

|------|-------------------------|------|

| A-12 | ABBR Bit Description    | A-17 |

| A-13 | CCQ2IR Bit Description  | A-18 |

| A-14 | CCQ1IR Bit Description  | A-19 |

| A-15 | CCQ0IR Bit Description  | A-20 |

| A-16 | ADFQIR Bit Description  | A-21 |

| A-17 | AMFQIR Bit Description  | A-22 |

| A-18 | AMCSR Bit Description   | A-27 |

| B-1  | Boot Error/Status Codes | B-2  |

| C-1  | CITCA Part Numbers      | C-1  |

### **About This Manual**

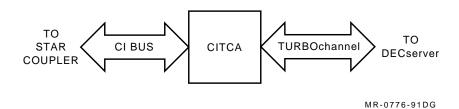

This manual describes the CITCA option, which provides an interface between the Computer Interconnect (CI) bus and the TURBOchannel bus.

#### **Intended Audience**

This manual is intended for Digital Customer Service engineers, or licensed customers who install and/or maintain this option.

#### **Manual Structure**

This manual contains five chapters:

- Chapter 1, Introduction

- Chapter 2, Site Preparation and Installation

- Chapter 3, Verification and Acceptance

- Chapter 4, Diagnostics

- Chapter 5, Functional Description

An appendix section contains three appendixes:

- Appendix A, Registers

- Appendix B, Boot Errors

- Appendix C, Part Numbers

#### **Related Documentation**

The following documentation can provide additional information about subjects relating to the  $\operatorname{CITCA}$ .

**Table 1 Related Documents**

| Order Number |

|--------------|

| EK-D590A-OG  |

| EK-CSEPG-MA  |

| EK-D590A-PS  |

| EK-D590A-SP  |

| EK-PM38C-MG  |

| EK-SC008-UG  |

| EK-TRBOC-MG  |

|              |

### Introduction

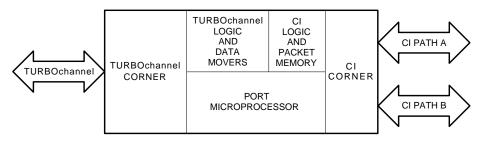

This chapter introduces the Computer Interconnect to TURBOchannel Adapter (CITCA). The CITCA option provides the hardware interface between the Computer Interconnect (CI) bus and the TURBOchannel bus in a TURBOchannel based system.

This chapter includes:

- General Description

- Physical Description

- Features

- Specifications

#### 1.1 General Description

The CITCA is an intelligent controller, residing on a triple-slot module, that connects the TURBOchannel bus to the CI bus. Figure 1–1 is a simplified diagram of the bus connection.

Figure 1-1 Simplified CITCA Connection

The CITCA uses a microprocessor and a control store FLASH PROM/RAM to communicate with the operating system and control the CI interface. The CITCA processes commands found on the command queues and packets received from the CI bus. The CITCA supports independent dual CI paths.

#### 1.2 Physical Description

#### 1.2.1 Components

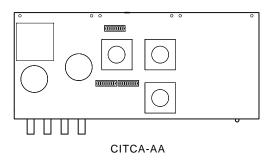

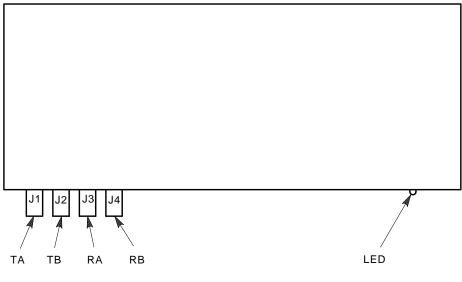

The CITCA-AA option consists of a single CITCA module. It is installed with four ThinWire CI cables that are ordered separately. Table 1–1 lists the part numbers for the hardware components shown in Figure 1–2. A list of related parts can be found in Appendix C.

Table 1-1 CITCA Hardware Components

| Component                   | Part Number                          |

|-----------------------------|--------------------------------------|

| CITCA module                | 54-20253-01                          |

| Set of four ThinWire cables | $\mathrm{BNCIA}	ext{-}\mathrm{xx}^1$ |

Figure 1-2 Hardware Components

BNCIA-xx

MR-0781-91DG

#### 1.2.2 Logic Components

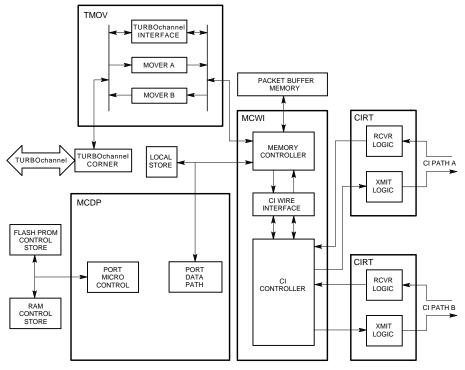

The CITCA module contains the following logical parts:

- TURBOchannel interface logic

- Packet Buffer (PB) RAMs

- Control Store RAMs

- Control Store FLASH PROMs

- Local Store RAMs

- Five gate arrays:

- TMOV: TURBOchannel interface control and data movers

- MCWI: PB memory control

- MCDP: Microprocessor and sequencer

- CIRT (2): CI receive/transmit logic, including Manchester encode/decode logic, byte framer and shift register

See Chapter 5 for details on the function of the module.

#### 1.3 Features

The following list describes the features of the CITCA option.

- Resequencing dual path operation

- 62.5 Mbyte/second packet buffer

- 2 data movers

- 32-bit internal data paths

- 64-nanosecond microcycle

- Parity on all internal buses and control stores

- Field updateable control store

- Simultaneous writes to multiple HSCs capability

- Diagnostic loopback capability (both internal and external)

- Data integrity through Cyclic Redundancy Checking (CRC)

- Round-robin arbitration at heavy loading, for each path

- Contention arbitration at light loading, for each path

- Packet-oriented data transmission

- Immediate acknowledgment of packet reception

- Operational modes:

- Uninitialized

- Disabled

- Enabled

### 1.4 Specifications

#### Table 1-2 Environmental Specifications

| Temperature       |                                                                                                                                                                                               |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating         | $10^{\circ}\text{C}$ to $40^{\circ}\text{C}$ ( $50^{\circ}\text{F}$ to $104^{\circ}\text{F}$ ) ambient temperature with a gradient of $10^{\circ}\text{C}$ ( $18^{\circ}\text{F}$ ) per hour. |

| Storage/shipping  | -40°C to $66$ °C (-40°F to $151$ °F) ambient temperature with a gradient of 20°C (36°F) per hour.                                                                                             |

| Relative humidity |                                                                                                                                                                                               |

| Operating         | 10% to 90% with a maximum wet bulb temperature of 28°C (82°F) and a minimum dew point of 2°C (36°F) with no condensation                                                                      |

| Storage/shipping  | 10% to 95% with no condensation                                                                                                                                                               |

| Altitude          |                                                                                                                                                                                               |

| Operating         | Sea level to 2.4 km (8000 ft)                                                                                                                                                                 |

|                   | Maximum operating temperatures decrease by a factor of 1°C/1000 ft (1.8°F/1000 ft) for operation above sea level                                                                              |

| Shipping/storage  | Up to 9.1 km (30,000 ft) above sea level (actual or effective by means of cabin pressurization)                                                                                               |

| Shock             | 10 Gs peak at 10 ms duration in three mutually perpendicular axes (maximum)                                                                                                                   |

#### Table 1-3 Electrical Specifications

Power consumption

$+5.0~\mathrm{V}$  at  $6.6~\mathrm{A}$  nominal

+12.0 V at less than 1 A nominal

### Site Preparation and Installation

| Caution                                                                 |

|-------------------------------------------------------------------------|

| Electrostatic discharge (ESD) can damage the module components.         |

| Always use an antistatic wrist strap and mat when handling the          |

| module. Place the wrist strap on your wrist, and attach the wrist strap |

| and antistatic mat to the system chassis. Do not touch the gate arrays  |

### 2.1 Site Preparation

Before you begin, take the following steps to ensure a smooth installation and minimize system downtime.

- The CITCA option requires three adjacent TURBOchannel option slots make sure they are available in the system.

- Discuss the switch settings with your customer. See Section 2.2.

- Ask the system manager to configure the ULTRIX operating system to include the CITCA and CI devices. The ULTRIX Guide to Configuration File Maintenance (AA-ME90C-TE) describes how to include devices into the operating system configuration.

- Label and route the CI cables. See Section 2.2.4.

- Refer to the Site Environmental Preparation Guide to make sure that you are installing the CITCA in the proper environment.

- Know the current version of microcode so you will know if an update is necessary. This information may be found in the CITCA section of the Revision Matrix document.

- Be prepared make sure that the following items are available on site.

- An antistatic kit

- CITCA-AA

- 4 ThinWire cables

- 12 1/4-inch screws (6 are shipped with the module, and 6 more are available after you remove the blank bulkhead panels)

- This document

#### 2.2 Module Setup

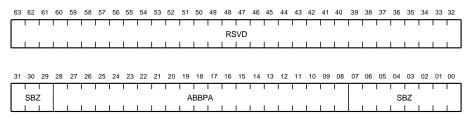

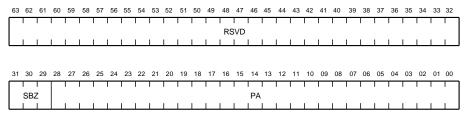

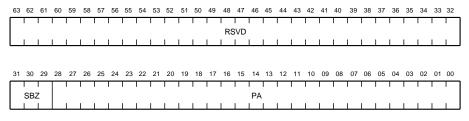

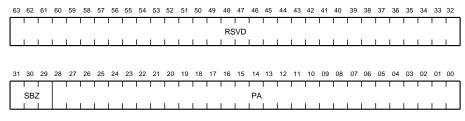

Before installing or replacing a CITCA module, set the switches to the proper position. Table 2-1 provides a summary of the switch settings, and Figure 2-1 shows their location on the module. It also shows the orientation of the switches on switchpack 3. The orientation of the switches on the other two switchpacks is the same as switchpack 3. Tables 2-2 through 2-9 list the individual switch settings.

Table 2-1 Summary of Switch Settings

| Switches     | Description                      | Default           | Refer to  |

|--------------|----------------------------------|-------------------|-----------|

| Switchpack 1 | Switchpack 1                     |                   |           |

| SW1          | FLASH PROM write control         | Off               | Table 2–2 |

| SW2          | Arbitration mode                 | Off               | Table 2–3 |

| SW3 - SW10   | CI node address                  | 1,2               | Table 2–4 |

| Switchpack 2 |                                  |                   |           |

| SW1          | Extend header                    | Off               | Table 2–5 |

| SW2          | Extend ACK timeout               | Off               | Table 2–6 |

| SW3 - SW10   | CI node address - duplicate      | $-^{1,2}$         | Table 2–4 |

| Switchpack 3 |                                  |                   |           |

| SW1 - SW3    | Quiet slot time                  | 1 & 2 Off<br>3 On | Table 2–7 |

| SW4 - SW6    | Arbitration modulus (node count) | All Off           | Table 2–8 |

| SW7 - SW10   | Boot time                        | All Off           | Table 2–9 |

$<sup>^{1}</sup>$ The system manager should determine the value of the CI node address based on the system configuration.

$<sup>^2</sup> The\ CI$  node address (switchpack 1, SW3 - SW10) and its duplicate (switchpack 2, SW3 - SW10)  $\underline{must}$  be configured exactly the same.

OFF ON SW3 (100000000) SW1

Figure 2–1 CITCA Module Switches and Connectors

MR-0778-91DG

### 2.2.1 Switchpack 1

Table 2-2 Switchpack 1 - Switch 1

| SW1                                                             | Description                    |

|-----------------------------------------------------------------|--------------------------------|

| Off *                                                           | FLASH PROM writes are enabled  |

| On                                                              | FLASH PROM writes are disabled |

| * = Default position<br>Off = switch open<br>On = switch closed |                                |

Table 2-3 Switchpack 1 - Switch 2

| SW2                                                             | Description                                                            |

|-----------------------------------------------------------------|------------------------------------------------------------------------|

| Off *                                                           | Allow normal CI star coupler arbitration.                              |

| On                                                              | Disable normal CI star coupler arbitration — Do not use this position. |

| * = Default position<br>Off = switch open<br>On = switch closed |                                                                        |

#### **Setting the CI Node Address Switches**

Your customer will determine what the CI node address should be. Each switch represents a bit weight  $2^n$  as shown below. To interpret a CI node address, add the bit weight values of each switch that is set. For example, to set CI node address 100, set SW4, SW5 and SW8 (64 + 32 + 4 = 100).

| Switch | Bit Weight |

|--------|------------|

| 3      | 128        |

| 4      | 64         |

| 5      | 32         |

| 6      | 16         |

| 7      | 8          |

| 8      | 4          |

| 9      | 2          |

| 10     | 1          |

|        |            |

Table 2-4 Switchpack 1 - Switches 3 through 10 and Switchpack 2 - Switches 3 through 10

| CI Node<br>Address<br>(Decimal) | SW3 | SW4 | SW5 | SW6 | SW7 | SW8 | SW9 | SW10 |

|---------------------------------|-----|-----|-----|-----|-----|-----|-----|------|

| 0                               | Off  |

| 1                               | Off | On   |

| 2                               | Off | Off | Off | Off | Off | Off | On  | Off  |

|                                 |     |     |     |     |     |     |     |      |

|                                 |     |     |     |     |     |     |     |      |

|                                 |     |     |     |     |     |     |     |      |

| 223                             | On  | On  | Off | On  | On  | On  | On  | On   |

| 224                             | On  | On  | On  | Off | Off | Off | Off | Off  |

|                                 |     |     |     |     |     |     |     |      |

|                                 |     |     |     |     |     |     |     |      |

|                                 |     |     |     |     |     |     |     |      |

| 255                             | On   |

|                                 |     |     |     |     |     |     |     |      |

See the previous page for an explanation on the switch settings. Off = switch open

On = switch closed

\_\_\_\_ Note \_

The CI node address (switchpack 1, SW3 - SW10) and its duplicate (switchpack 2, SW3 - SW10) must be configured exactly the same.

CI Node addresses 224 through 255 are reserved.

#### 2.2.2 Switchpack 2

Table 2-5 Switchpack 2 - Switch 1

|                                                                 | -                                           |

|-----------------------------------------------------------------|---------------------------------------------|

| SW1                                                             | Description                                 |

| Off *                                                           | Normal header                               |

| On                                                              | Extended header — Do not use this position. |

| * = Default position<br>Off = switch open<br>On = switch closed |                                             |

Table 2-6 Switchpack 2 - Switch 2

| SW2                                                             | Description                                      |

|-----------------------------------------------------------------|--------------------------------------------------|

| Off *                                                           | Normal ACK timeout                               |

| On                                                              | Extended ACK timeout — Do not use this position. |

| * = Default position<br>Off = switch open<br>On = switch closed |                                                  |

#### Switchpack 2 — Switches 3 through 10

The CI node address duplicate switches (Switchpack 2 — switches 3 through 10) are set exactly the same as the CI node address switches (Switchpack 1 switches 3 through 10). Refer to Table 2–4 to see how these switches are set.

#### 2.2.3 Switchpack 3

Table 2-7 Switchpack 3 - Switches 1 through 3, Quiet Slot Time Configuration Switches

| Quiet        |     |     |     |

|--------------|-----|-----|-----|

| Slot Count   | SW1 | SW2 | SW3 |

| 7            | Off | Off | Off |

| $10^{1} *$   | Off | Off | On  |

| Reserved     | Off | On  | Off |

| Reserved     | Off | On  | On  |

| Reserved     | On  | Off | Off |

| Reserved     | On  | Off | On  |

| Reserved     | On  | On  | Off |

| Programmable | On  | On  | On  |

$<sup>^1\</sup>mathrm{See}$  note below

Note \_

The quiet slot time configuration switches  $\underline{\text{must}}$  be set to 10.

<sup>\* =</sup> Default position Off = switch open On = switch closed

Table 2-8 Switchpack 3 - Switches 4 through 6

| (Decimal) SW | 4 SW5 | SW6 |  |

|--------------|-------|-----|--|

|              |       |     |  |

| 16 * Off     | Off   | Off |  |

| 32 Off       | Off   | On  |  |

| 64 Off       | On    | Off |  |

| 128 Off      | On    | On  |  |

| 224 On       | Off   | Off |  |

| Reserved On  | Off   | On  |  |

| Reserved On  | On    | Off |  |

| Reserved On  | On    | On  |  |

\* = Default position Off = switch open On = switch closed

Table 2-9 Switchpack 3 - Switches 7 through 10

| Time      |     |     |     |      |  |

|-----------|-----|-----|-----|------|--|

| (seconds) | SW7 | SW8 | SW9 | SW10 |  |

| 1500 *    | Off | Off | Off | Off  |  |

| 1400      | Off | Off | Off | On   |  |

| 1300      | Off | Off | On  | Off  |  |

| 1200      | Off | Off | On  | On   |  |

| 1100      | Off | On  | Off | Off  |  |

| 1000      | Off | On  | Off | On   |  |

| 900       | Off | On  | On  | Off  |  |

| 800       | Off | On  | On  | On   |  |

| 700       | On  | Off | Off | Off  |  |

| 600       | On  | Off | Off | On   |  |

| 500       | On  | Off | On  | Off  |  |

| 400       | On  | Off | On  | On   |  |

| 300       | On  | On  | Off | Off  |  |

| 200       | On  | On  | Off | On   |  |

| 100       | On  | On  | On  | Off  |  |

| 0         | On  | On  | On  | On   |  |

<sup>\* =</sup> Default position Off = switch open On = switch closed

#### 2.2.4 CI Cable Routing

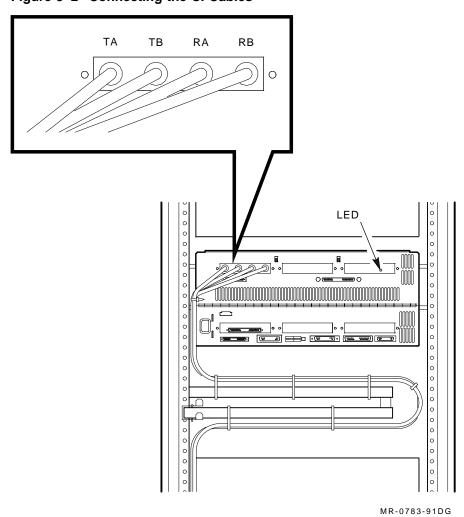

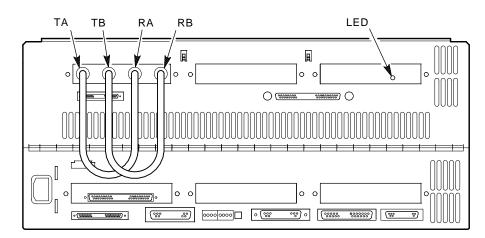

Take the following steps to label and route the ThinWire CI cables (BNCIA-10/20).

1. Label both ends of the 4 ThinWire cables as follows:

Cable 1 - TA (transmit path A)

Cable 2 - TB (transmit path B)

Cable 3 - RA (receive path A)

Cable 4 - RB (receive path B)

- 2. Connect one end of the cables to the star coupler. Refer to the *SC008 Star Coupler User Guide* for more information.

- 3. Route the cables from the star coupler to the system where you are installing the CITCA module.

- 4. Route the cables up the back of the system cabinet as shown in Figure 2-2.

- 5. Use one or two tie wraps to loosely hold the cables in place for now. They will be tightened after the CITCA is installed.

Figure 2-2 Cable Routing

MR-0306-92DG

#### 2.3 Installation

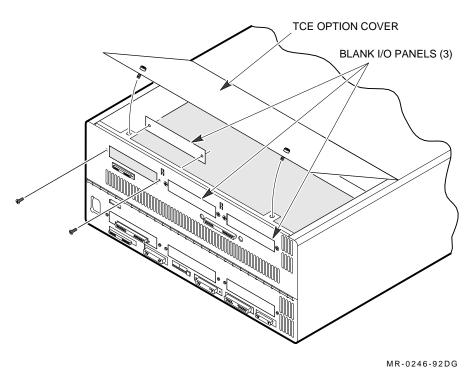

This section describes how to install a CITCA module into a TURBOchannel based system. To illustrate the procedure, we described the installation of a CITCA module into a TURBOchannel extender (TCE) on a DECsystem 5900 system. The installation procedure is similar in other systems. Refer to your system documentation for system-specific details.

#### Caution \_\_

Electrostatic discharge (ESD) can damage the module components. Always use an antistatic wrist strap and mat when handling the module. Place the wrist strap on your wrist, and attach the wrist strap and antistatic mat to the system chassis. Do not touch the gate arrays.

To install a CITCA option, perform the following steps.

- 1. Perform the tasks described earlier, which include:

- Set the switches on the CITCA module. See Sections 2.2.1 through 2.2.3.

- Label and route the CI cables. See Section 2.2.4.

- Ask the system manager to configure the ULTRIX operating system to include the CITCA and CI devices.

| 2. | Ask the system manager or operator to shut down the operating system.                                                                                                                                                |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | Note                                                                                                                                                                                                                 |

|    | The console commands are case sensitive. Be sure to type commands <i>exactly</i> as shown in the examples that are provided. Refer to your system documentation for detailed information about the console commands. |

3. Use the console command *printenv* to see if the system has autoboot enabled. If the halt action field shown on the console printout equals b (for boot), disable the autoboot with the following command.

setenv haltaction h

- 4. Open the front door of the system cabinet.

- 5. Power down the system by placing the system power switch on the CPU drawer in the O (off) position.

- 6. Pull out the stabilizer foot from the front of the cabinet.

- 7. Pull out the CPU drawer until you hear the safety locks click. This will allow you to install the CITCA into the system drawer from the front of the cabinet.

#### OR

Pull out the mass storage drawer that is located directly above the CPU drawer until you hear the safety locks click. This will allow you to install the CITCA into the CPU drawer from the back of the cabinet.

8. Open the rear door of the cabinet.

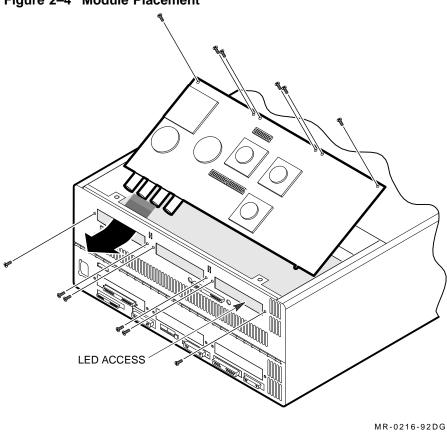

Figure 2-3 CPU Drawer — Rear View

- 9. Release the two TCE option cover screws by turning them to the left until they release, and remove the option cover. See Figure 2-3.

- 10. Make sure that the TCE is empty. The CITCA uses all three TCE slots. If a module is already installed in the TCE, move it to an unused TURBOchannel slot.

- 11. Remove the three blank I/O panels, and save the screws. See Figure 2-3.

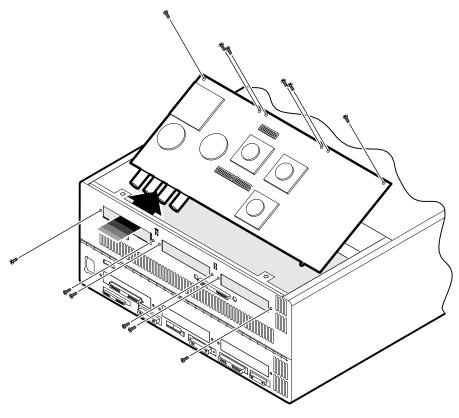

- 12. Put the CITCA in place by first aligning the back of the module with the I/O panel cutouts, then aligning the front of the module with the three TURBOchannel connectors. Next apply backward and downward pressure to the front of the module using care to avoid bending the connector pins until the module pops into place. See Figure 2-4.

Figure 2–4 Module Placement

- 13. Secure the module in place with 12 screws as shown in Figure 2-4. If the CPU drawer was pulled out in step 7, you may want to push it in before securing the screws on the bulkhead.

- 14. Verify the operation of the CITCA by performing the acceptance procedures listed in Chapter 3.

#### 2.3.1 Removing a CITCA

| O+:-   |   |  |

|--------|---|--|

| Cautio | n |  |

Electrostatic discharge (ESD) can damage the module components. Always use an antistatic wrist strap and mat when handling the module. Place the wrist strap on your wrist, and attach the wrist strap and antistatic mat to the system chassis. Do not touch the gate arrays.

The procedure to remove a CITCA module from a DECsystem 5900 system is described in the following steps. The removal procedure for other systems is similar.

- 1. Ask the system manager or operator to shut down the operating system.

- 2. Power down the system by placing the system power switch in the O (off) position.

- 3. Pull out the stabilizer foot from the front of the cabinet.

- 4. Verify that the CI cables are labeled correctly (Figure 3-2), and label them if necessary.

- 5. Disconnect the CI cables.

- 6. Go to the front of the cabinet and pull out the CPU drawer until you hear the safety locks click.

- 7. Release the two TCE option cover screws by turning them to the left until they release, and remove the option cover. See Figure 2–3.

- 8. Remove the 12 screws shown in Figure 2-5.

- Gently lift the front of the module up until the TURBOchannel connectors release from the expander module, then pull the module forward and away. See Figure 2–5.

- 10. If you are not replacing the CITCA, replace the three I/O panel covers. See Figure 2-3.

Figure 2–5 Module Removal

MR-0217-92DG

### **Verification and Acceptance**

#### 3.1 Verification Procedure

The following list describes all the steps required to verify the installation and operation of the CITCA option. This procedure begins with:

- The operating system down

- The system power off

- The CI cables disconnected from the CITCA

- 1. Attach two CI attenuator/loopback connectors (PN 12-19907) as follows: At the back of the system, attach one end of the first CI attenuator cable to J1 (labeled TA) and the other end to J3 (labeled RA).

- Connect one end of the second CI attenuator cable to J2 (labeled TB) and the other end to J4 (labeled RB). See Figure 3-1.

- 2. Power up the system by placing the system power switch in the | (on) position.

- 3. Check to see if the self-test LED is on (Figure 3-1). TCAST lights the selftest LED on the CITCA module to show that it has completed successfully. TCAST verifies the operation of the CITCA option, and is run automatically when the system is powered up. See Chapter 4 for details about TCAST.

TΑ RΒ LED RA » oooo oooo 🗆 o 端

Figure 3-1 Connecting the Attenuator/Loopback Cables

MR-0779-91DG

- 4. Type *cnfg* at the console prompt to verify that the system sees the CITCA, and the microcode is up to date. Example 3-1 shows the console output that you can expect to see, although the output on your system console may differ slightly to show specific features of your system. The cnfg command provides the following information:

- The first column lists the TURBOchannel slot into which the device is installed.

- The next column lists the device type and manufacturer.

- The next column lists the diagnostic microcode version.

- The next column lists the device architecture.

- The last column lists important information about the device. For CITCA it lists the CI node address and the contents of the failing test code (PDFLT) field of the port diagnostic control/status register (PDCSR).

| No                                | ote                        |

|-----------------------------------|----------------------------|

| PDFLT code e0 indicates that TCAS | ST completed successfully. |

## Example 3-1 Using the cnfg Command

```

>>cnfg

TCF0 (128 MB, 1 MB NVRAM)

3: KN03-AA DEC

V5.1b

(enet: 08-00-2b-1c-1d-07)

(SCSI = 7)

0: CITCA-AA DEC

0x.01

TCF0[OPTION ROM]

(CI node address: 014{d}, PDFLT = e0)

```

- 5. Use the *boot slot/l* command to verify the ability of the CITCA to send and receive packets. See Section 4.3.1 for more details about this command.

- If the loopback test fails, refer to Section 3.2, Troubleshooting. Appendix B describes the error codes.

- If the loopback test passes, continue on to the next step.

- 6. Power down the system by placing the system power switch in the O (off) position.

- 7. Remove the CI attenuator/loopback cables.

- 8. Attach the CI cables as shown in Figure 3-2. If the cables have not been routed in the cabinet, see Section 2.2.4.

- 9. Power up the system by placing the system power switch in the | (on) position.

- 10. Verify that the self-test LED is on. See Figure 3–2.

- 11. Use the Revision Matrix Document and the *cnfg* console command to verify the revision level of the CITCA FLASH PROM. Example 3-1 shows the console output from the cnfg command. Refer to Section 4.4.8 if you need to update the FLASH PROM.

- 12. Use the boot slot/c console command to verify the CI path connections, and also to make sure there are no duplicate CI node numbers in the CI environment. See Section 4.3.2 for details about this command.

- 13. Use a tie wrap to hold the CI cables on the cable arm as shown in Figure 3–2.

Figure 3-2 Connecting the CI Cables

- 14. Replace the drawer cover, push in the drawer, and close the system doors.

- 15. Enable auto-boot if you disabled it earlier.

- 16. Ask the system manager or operator to boot the operating system.

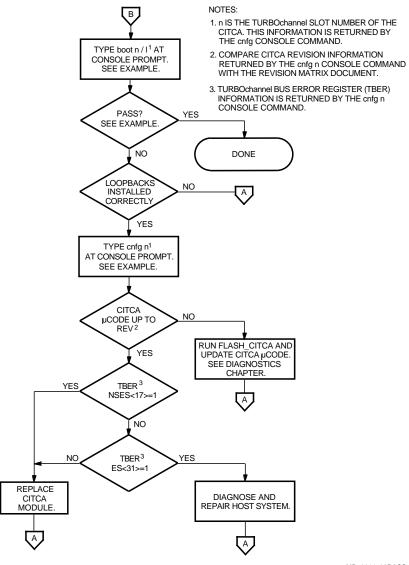

# 3.2 Troubleshooting

This section contains a flowchart to be used to diagnose and repair problems that may occur during the installation of a CITCA module into a system. It also contains information to help you recognize error conditions described in the flowchart.

Table 3-1 lists the PDFLT codes that may be corrected in the field. PDFLT codes not listed in Table 3–1 require module replacement.

Table 3-1 PDFLT Codes

| Code       | Description                                                           | Required Action                                                                                                                                                              |

|------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D1         | Node and duplicate node addresses differ                              | Set SP1, SW3 - 10 and SP2, SW3 - 10 to the same value.                                                                                                                       |

| <b>E</b> 0 | TCAST completed successfully                                          | None                                                                                                                                                                         |

| F1         | Illegal arbitration modulus (cluster size)                            | Set SP3, SW4 - 6 to a value of 16 or 32.                                                                                                                                     |

| F2         | Invalid node number -<br>Node number is higher<br>than the node count | Set the node address value (SP1, SW3 - 10 and SP2, SW3 - 10) lower than the node count value (SP3, SW4 - 6); or set the node count value higher than the node address value. |

| F3         | Quiet slot time is illegal                                            | Verify SP3, SW1 - 3 is set to a value of 10.                                                                                                                                 |

| F4         | Node and duplicate node addresses differ                              | Set SP1, SW3 - 10 and SP2, SW3 - 10 to the same value.                                                                                                                       |

START Α ATTACH LOOPBACK CONNECTORS. POWER UP TYPE cnfg AT CONSOLE PROMPT. SEE EXAMPLE. CITCA PRESENT IN cnfg TABLE YES NO NO YES LED LIT LED B NO YES SYSTEM DIAGNOSTICS PASS PDFLT<sup>1</sup> = EO PDFLT<sup>1</sup> = D1, F1, F2, YES NO NO F3 OR F4 REPLACE CITCA MODULE. REPLACE CITCA MODULE. YES CITCA SWITCH SETTINGS ARE INCORRECT. VERIFY THAT THE HOST SYSTEM IS FUNCTIONAL. Α CHECK AND RESET CITCA SWITCHES. SEE PDFLT CODE TABLE. 1. THE PDFLT FIELD OF THE PDCSR REGISTER IS RETURNED BY THE cnfg CONSOLE COMMAND. MR-0313-92RAGS

Figure 3–3 Installation Verification/Troubleshooting Flowchart (Part 1 of 2)

Figure 3-4 Installation Verification/Troubleshooting Flowchart (Part 2 of 2)

MR-0314-92RAGS

Example 3–2 shows a sample of the console output from the boot  $n/l^1$ command. The output on your system console may differ slightly to reflect specific features of your system. In this example, a CITCA is installed in TURBOchannel slot 0.

#### Example 3-2 Boot n/l

```

>>boot 0/1

TCA Slot Number = 0, Mips Address = be000000

[TCA Boot Code Version: V1]

[Functional ucode version is :ae]

*** Adapter Max PGRP before reading cnfg jumpers: 0.

*** Adapter Max PGRP after the reading : 15.

CITCA CI own Node number is: 5.

*** CI path A loopback test: OK

*** CI path B loopback test: OK

```

Example 3–3 shows the console output from the cnfg  $n^1$  console command. The output on your system console may differ slightly to reflect specific features of your system. In this example, a CITCA is installed in TURBOchannel slot 0.

#### Example 3-3 Using the cnfg n Command

```

>>cnfg 0

0: CITCA-AA DEC

0x.01

TCF0[OPTION ROM]

(CI node address: 001\{d\}, PDFLT = e0\{x\})

The Slot Base Address = be800000 of TURBOchannel Slot 0

TDEV = 80ff00ca

TBER = 1c000000

PDCSR = 800000e0

ASNR = 7fffffff

CITCA Module Serial Number = AS268435455

CITCA Module H/W revision- = S15

CITCA Diagnostic Microcode revision

CITCA Functional Microcode revision

CITCA MIPS_resp Microcode revision

CITCA External Switch Enable Register value:

SWCHENR: [ 00200101 ]

```

n is the TURBOchannel slot number where the CITCA is installed.

# 3.3 Booting from CITCA

To boot the system software from an MSCP disk drive on the CI bus, use the format boot slot/CI node ra drive/file where:

- boot specifies the boot command.

- slot specifies the CITCA slot number.

- CI node specifies the node number of the HSC drive controller.

- ra specifies the type of disk drive that performs the boot operation.

- drive specifies the MSCP drive number.

- file specifies the name of the file that you want to boot.

See your system user guide for optional arguments for the boot command.

The command boot 0/12ra3/vmunix shows what the boot command would look like if you were trying to boot a system disk through the CITCA under the following conditions:

- The CITCA is installed in TURBOchannel slot 0

- The CI node number of the HSC disk controller is 12

- You are booting from disk number 3

- You wish to boot the file named vmunix

#### 3.3.1 Boot Errors

If the system fails to boot the operating software from an MSCP disk drive on the CI bus, perform the following steps:

- 1. Use the troubleshooting flowchart shown in Figure 3–3.

- 2. Use the boot slot/c console command to verify the CI path connections, and also to make sure there are no duplicate CI node numbers in the CI environment. See Section 4.3.2 for details about this command.

- 3. Make sure that the ULTRIX configuration file includes the CITCA and CI devices. Refer to the ULTRIX Guide to Configuration File Maintenance.

- 4. Refer to Appendix B for information about troubleshooting boot errors.

# **Diagnostics**

The following diagnostic tools may be used to verify correct operation of the CITCA.

- TCAST CITCA power-up self-test

- PST CITCA MIPS-based power-up self-test, CITCA subtest

- CI verification CI functional testing

- FLASH\_CITCA<sup>1</sup> CITCA standalone diagnostic and FLASH PROM update utility

## 4.1 TCAST

TCAST verifies the operation of the CITCA. Located in FLASH PROM on the CITCA module, the TCAST uses a bottom-up approach in testing; each test executes only after all preceding tests have successfully completed.

The CD ROM that contains the FLASH\_CITCA diagnostic is not available to the field except in the case of a field-upgradable microcode update.

#### 4.1.1 TCAST Tests

The tests that are performed by TCAST are as follows:

- Test 1 MCDP Processor ALU Status and Branch Test

- Test 2 ALU Arithmetic/Logical Function Test

- Test 3 General Purpose Register Test

- Test 4 Microsequencer Stack Test

- Test 5 Internal Bus Loopback Test

- Test 6 Interval Timer Test

- Test 7 Local Store Test

- Test 8 Memory Control and Wire Interface Test

- Test 9 Data Mover A Test

- Test 10 Data Mover B Test

- Test 11 TURBOchannel Commander Test

- Test 12 TURBOchannel Responder Test

- Test 13 Data Mover Loopback Test

- Test 14 MCWI Error Detection Logic Test

- Test 15 TMOV Error Detection Logic Test

- Test 16 Interrupt Control Registers Test

- Test 17 CI Maintenance Loopback Test

## 4.1.2 Running TCAST

TCAST runs automatically when the system is powered up or the CITCA is reset. Alternately, it may be run as test 4 from FLASH\_CITCA. It takes less than 1 second to complete. Pass/fail information is provided as shown in Table 4–1. Figure 4–1 shows the location of the self-test passed LED on the CITCA module. It can be seen through an access hole in the rear bulkhead shield.

Table 4-1 TCAST Pass/Fail Information

| Location of Error Indicator                                                         | If TCAST<br>Passed | If TCAST<br>Failed |

|-------------------------------------------------------------------------------------|--------------------|--------------------|

| Self-test Passed LED on the CITCA <sup>1</sup>                                      | LED on             | LED off            |

| Self-test Failed (STF) bit in the TURBO<br>channel Bus Error Register (TBER) $^{2}$ | Bit cleared        | Bit set            |

<sup>&</sup>lt;sup>1</sup>See Figure 4–1

<sup>&</sup>lt;sup>2</sup>TBER (BB + 08), bit 16

MR-0777-91DG

# 4.1.3 Interpreting Error Information

In most cases, a TCAST failure requires the replacement of the CITCA module, however an incorrect switch setting could cause a failure that may be corrected in the field. Use the *cnfg* console command to determine the port diagnostic failing test code (PDFLT). Table 4–2 describes the PDFLT codes that may be corrected in the field. PDFLT codes not listed in Table 4–2 require module replacement.

Table 4-2 PDFLT Codes

| Code | Description                                                           | Required Action                                                                                                                                                              |

|------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D1   | Node and duplicate node addresses differ                              | Set SP1, SW3 - 10 and SP2, SW3 - 10 to the same value.                                                                                                                       |

| E0   | TCAST completed successfully                                          | None.                                                                                                                                                                        |

| F1   | Illegal arbitration modulus (cluster size)                            | Set SP3, SW4 - 6 to a value of 16 or 32.                                                                                                                                     |

| F2   | Invalid node number -<br>Node number is higher<br>than the node count | Set the node address value (SP1, SW3 - 10 and SP2, SW3 - 10) lower than the node count value (SP3, SW4 - 6); or set the node count value higher than the node address value. |

| F3   | Quiet slot time is illegal                                            | Verify SP3, SW1 - 3 is set to a value of 10.                                                                                                                                 |

| F4   | Node and duplicate node addresses differ                              | Set SP1, SW3 - 10 and SP2, SW3 - 10 to the same value.                                                                                                                       |

## **4.2 PST**

The MIPS-based PST runs a comprehensive test of the system hardware. This section describes the subtest that verifies the ability of the host system to communicate successfully with the CITCA.

Refer to your system documentation for details about the PST.

#### 4.2.1 PST CITCA Subtests

The PST subtest that tests the CITCA contains the following two tests:

- pdflt Checks the contents of the PDFLT field in the port diagnostic control and status register (PDCSR) and reports error conditions if they exist.

- ROM Checks the CITCA option ROM header information and reports error conditions if they exist.

## 4.2.2 Running the CITCA Subtest

PST runs automatically when the system is powered up or reset. Error information is reported through the system console terminal and self-test LED on the module.

To run an individual test on the CITCA, use the format *t slot/test\_name* where:

- *t* specifies the test command.

- *slot* specifies the TURBOchannel slot where the CITCA is installed.

- *test\_name* specifies the individual test that you wish to run.

Example 4–1 shows the command that you would type if you wished to run the pdflt test on a CITCA that is installed in slot 0. This example also shows how the console reports error information. User input is underlined.

A successful pass of the test does not return a status message.

#### Example 4-1 Running the pdflt Subtest

```

>>t 0/pdflt

?TFL: 0/pdflt (The CITCA in slot 0 has a self-test error = D1.) [CITCA]

```

#### 4.2.3 Interpreting Error Information

Error information is reported on the system console terminal in the format *?TFL slot/test (error\_code: description) [module]* where:

- *?TFL* indicates that an error occurred.

- *slot* specifies the TURBOchannel slot number where the module that reported the error is installed.

- test specifies the individual test that failed.

- *error\_code: description* specifies which part of the test failed. and provides a brief description of the failure.

- *module* identifies the failing module number.

The error message shown in Example 4–1 states that the CITCA module in slot 0 failed the pdflt test, and the error code is D1. Table 4–2 describes the PDFLT codes that may be corrected in the field. PDFLT codes not listed in Table 4–2 require module replacement.

## 4.3 CI Verification

The CI verification tests ensure that CITCA is correctly connected to the CI bus and is able to communicate with other nodes in the CI environment. These tests are CITCA specific and use the boot command to execute. The following tests make up the CI verification tests:

CI External Loopback Test

CI Node Configuration Test

## 4.3.1 CI External Loopback Test

The CI external loopback test allows you to verify the operation of the CITCA module and the CI cables. During this test, the CITCA sends a datagram to its own CI node address — with or without CI attenuator/loopback connectors attached. A successful pass of this test verifies the CITCA send and receive logic and, optionally, the CI cables as well.

If you suspect a problem with the CI bus, first run the CI external loopback test with CI attenuator/loopback connectors attached to the CITCA. This will verify the operation of the CITCA module. Next, remove the CI attenuator /loopback connectors, attach the CI cables, and run the loopback test a second time. This will verify the operation of the CI cables.

#### 4.3.1.1 Connecting the CI Attenuator/Loopback Connectors

Attach two CI attenuator/loopback connectors as follows:

- 1. Power down the system by placing the system power switch in the O (off) position.

- 2. At the back of the system, attach one end of the first CI attenuator/loopback connector to J1 (labeled TA) and the other end to J3 (labeled RA). Connect one end of the second CI attenuator/loopback connector to J2 (labeled TB) and the other end to J4 (labeled RB). See Figure 4-2.

- 3. Power up the system by placing the system power switch in the | (on) position.

Figure 4–2 Connecting the CI Attenuator/Loopback Connectors

MR-0779-91DG

## 4.3.1.2 Program Execution

To execute the loopback test, use the format  $boot \ slot/l$  where:

- boot specifies the boot command.

- *slot* specifies the CITCA slot number.

- *l* specifies that you wish to run the loopback test.

Example 4–2 shows the console output from a successful loopback test. In this example, the CITCA is installed in TURBOchannel slot 0, and the attenuator/loopback connectors are installed. User input is underlined.

#### Example 4-2 CI External Loopback Test — Passed

```

>>boot 0/1

TCA Slot Number = 0, Mips Address = be000000

[TCA Boot Code Version: V1]

[Functional ucode version is :ae]

*** Adapter Max PGRP before reading cnfg jumpers: 0.

*** Adapter Max PGRP after the reading : 15.

CITCA CI own Node number is: 5.

*** CI path A loopback test: OK

*** CI path B loopback test: OK

```

If the loopback test fails, error information is output to the console terminal. The last line of the console message contains an error code. Appendix B describes the error codes.

Example 4-3 shows the console output from a loopback test that failed because of a bad connection on CI path B. In this example, the CITCA is installed in TURBOchannel slot 0, and the CI cables are connected to the CITCA. User input is underlined.

#### Example 4-3 CI External Loopback Test — Failed

```

>>boot 0/1

TCA Slot Number = 0, Mips Address = be000000

[TCA Boot Code Version: V1]

[Functional ucode version is :ae]

*** Adapter Max PGRP before reading cnfg jumpers: 0.

*** Adapter Max PGRP after the reading : 15.

CITCA CI own Node number is: 5.

*** CI path A loopback test: OK

*** Time-out - No response

*** Please, check CI cable connection

*** CI path B test: FAILED

error/status code is: 2f

```

## 4.3.2 CI Node Configuration Test

The CI node configuration test allows you to verify that the CITCA is able to communicate with the other nodes in the CI environment. During this test, the CITCA issues a request for information to all nodes in the CI environment. The other nodes respond with their node number and hardware type.

If the CI node configuration test fails, error information including an error code is output to the console terminal. Appendix B describes the error codes.

To show the CI node configuration, use the format *boot slot/c* where:

- boot specifies the boot command.

- *slot* specifies the CITCA slot number.

- c specifies that you wish to check the CI node configuration.

Example 4–4 shows the console output from the CI node configuration test. In this example, the CITCA is installed in TURBOchannel slot 0. User input is underlined.

#### Example 4-4 Cl Node Configuration Test

```

>>boot 0/c

[TCA Slot Number = 0, Mips Address = be000000]

[TCA Boot Code Version: V1]

[Functional ucode version is : ae]

*** Adapter Max PGRP before reading cnfg jumpers: 0.

*** Adapter Max PGRP after reading cnfg jumpers: 15.

CITCA CI own Node number is: 5.

Node: 2

HSCXX

Node: 3

HSCXX

Node: 5

CITCA

Node: 7

CITCA

Node: 9

HSCXX

Node: 13

HSCXX

Node: 14

CITCA

>>

```

## 4.4 FLASH\_CITCA

FLASH\_CITCA contains 7 tests and 8 utility programs for a total of 15 standalone images. It is used in the manufacturing environment to test the module logic and function of the CITCA. Although it extensively tests the CITCA, this diagnostic is not required to verify the operation of the CITCA at the customer site. Field use of FLASH\_CITCA is intended to be limited to microcode updates.

FLASH\_CITCA runs in standalone mode under the control of the system console executive (REX). It resides on CD ROM, but is not available to the field except as a microcode update. See Section 4.4.2 for examples of loading FLASH\_CITCA.

FLASH\_CITCA does not support power fail/restart. If a power failure occurs while it is running, FLASH\_CITCA must be reloaded and restarted.

### 4.4.1 FLASH CITCA Tests and Utilities

FLASH CITCA contains the following tests:

- Test 0: Execute tests 1 through 7

- Test 1: TURBOchannel scan path

- Test 2: FLASH PROM region checksums

- Subtest 1: Self test microcode region checksum

- Subtest 2: Functional microcode region checksum

- Subtest 3: Responder microcode region checksum

- Subtest 4: Responder microcode data 1 region checksum

- Subtest 5: Responder microcode data 2 region checksum

- Subtest 6: Responder microcode data 3 region checksum

- Subtest 7: Responder microcode data 4 region checksum

- Test 3: RAM memory

- Test 4: TCAST self-test via node reset

- Test 5: TURBOchannel contained registers

- Test 6: TURBOchannel served registers

- Test 7: TURBOchannel host memory DMA data exchange

In addition to the above tests, FLASH\_CITCA contains the following utility programs:

- Test 8: Clear FLASH PROM regions

- Test 9: Clear and erase FLASH PROM regions

- Test a: Update all FLASH PROM regions

- Test b: Verify all FLASH PROM regions

- Test c: INIT\_CB Initialize the FLASH PROM control block

- Test d: EXAM\_CB Examine the FLASH PROM control block

Test e: EXAM\_PG - Examine the program control block Test f: Operator - Change flags and TURBOchannel slot

Typing h or ? at the flash\_citca> prompt lists all the FLASH\_CITCA tests on the console terminal.

#### 4.4.1.1 Test Description

**Test 0: Execute tests 1 - 7** — Executes tests 1 - 7 without operator intervention.

**Test 1: TURBOchannel scan path** — Verifies the data integrity and addressability of the scan path from the TURBOchannel bus to the port scan data register (PSDR).

**Test 2: FLASH PROM region checksums** — Verifies that the seven regions in FLASH PROM contain valid data. A separate checksum subtest is run for each region.

- Subtest 1: Self-test microcode region checksum A failure produces a self-test microcode checksum error.

- Subtest 2: Functional microcode region checksum A failure produces a functional microcode checksum error.

- Subtest 3: Responder microcode region checksum A failure produces a responder microcode checksum error.

- Subtest 4: Responder microcode data 1 region checksum A failure produces a responder data 1 checksum error.

- Subtest 5: Responder microcode data 2 region checksum A failure produces a responder data 2 checksum error.

- Subtest 6: Responder microcode data 3 region checksum A failure produces a responder data 3 checksum error.

- Subtest 7: Responder microcode data 4 region checksum A failure produces a responder data 4 checksum error.

**Test 3: RAM Memory** — Verifies the data integrity and addressability of the RAM.

**Test 4: TCAST self-test via node reset** — Initiates a complete node reset by writing a 1 to the node reset (NRST) bit in the TURBOchannel Bus Error Register (TBER). The reset causes the TCAST diagnostic to execute.

**Test 5: TURBOchannel contained registers** — Ensures that the TURBOchannel contained register addresses can be read.

**Test 6: TURBOchannel served registers** — Ensures that the TURBOchannel served register addresses can be read.

**Test 7: TURBOchannel host memory DMA data exchange** — Ensures that the CITCA is able to execute read and write DMA commands to the host system memory.

#### 4.4.1.2 Utility Description

**Test 8: Clear FLASH PROM regions** — Writes 0s in all regions in the FLASH PROM to clear the data. This utility is normally not run; if it is, you must update the FLASH PROM to replace the microcode that was cleared.

**Test 9: Clear and erase FLASH PROM regions** — Writes 0s in all regions in the FLASH PROM to clear the data, then writes 1s in all regions to erase the data regions. This utility is normally not run; if it is, you must update the FLASH PROM to replace the microcode that was cleared.

**Test a: Update all FLASH PROM regions** — Allows the user to update the option ROM, functional, diagnostic, and responder firmware stored in the FLASH PROM. This utility includes a copy of the firmware, which it uses to update the FLASH PROM. First, this utility clears and erases the FLASH PROM, then it loads the FLASH PROM with the updated information. Next, the program verifies the success of the update by reading the code from FLASH PROM and comparing it to the copy that is included in FLASH CITCA.

**Test b: Verify all FLASH PROM regions** — Allows the user to verify that the FLASH PROM contains the current version of the option ROM, functional, diagnostic, and responder microcode. This utility includes a copy of the firmware, which it compares with the firmware stored in FLASH PROM.

**Test c: INIT\_CB - Initialize the Control Block** — Allows the user to use the operator console terminal to initialize the module serial number and module revision information stored in the control block section of the FLASH PROM. This utility is normally not run.

**Test d: EXAM\_CB - Examine the Control Block** - Displays the following information from the control block section of the FLASH PROM.

- Module serial number

- Module revision level

- Functional microcode revision level

- Diagnostic microcode revision level

- Responder microcode revision level

- Option ROM firmware revision level

- Functional microcode region checksum

- Diagnostic microcode region checksum

- Responder microcode region checksum

- Responder data 1 region checksum

- Responder data 2 region checksum

- Responder data 3 region checksum

- Responder data 4 region checksum

**Test e: EXAM\_PG - Examine the Program control block** — Displays the following information from the program control block section of the FLASH\_CITCA program image.

- Diagnostic microcode revision level

- Functional microcode revision level

- Responder microcode revision level

- Option ROM firmware revision level

**Test f: Operator - Change flags and TURBOchannel slot** — Allows the user to change program event flags and the TURBOchannel address pointer. This utility is menu driven. The following list shows the program event flags and their default values.

Table 4-3 FLASH CITCA Event Flags

| Event Flag              | Description (When Set)                                 | Default Value          |

|-------------------------|--------------------------------------------------------|------------------------|

| Halt                    | Halt on error                                          | Cleared                |

| Loop                    | Loop on error                                          | Cleared                |

| Inhibit                 | Inhibit error message reporting                        | Cleared                |

| Quick                   | Runs an abbreviated version of the diagnostic          | Set                    |

| TURBOchannel<br>Address | Where the diagnostic expects the CITCA to be installed | TURBOchannel<br>slot 1 |

## 4.4.2 Loading FLASH\_CITCA

The load procedure consists of the following four steps:

- 1. Booting the FLASH\_CITCA program image (Section 4.4.2.1).

- 2. Resetting the system.

- 3. Booting the system console program image (Section 4.4.2.2).

- 4. Overlaying the existing ROM objects with a pointer to the FLASH\_CITCA image (Section 4.4.2.3).

#### 4.4.2.1 Booting the FLASH\_CITCA Program Image

To boot the standalone diagnostic image, use the format >>> boot slot/device /flash\_citca where:

- *boot* specifies the boot command.

- *slot* specifies the TURBOchannel slot number of the boot device controller.

- device specifies the type and number of the device from which you wish to hoot

- *flash\_citca* indicates that you wish to boot the FLASH\_CITCA program image.

Example 4–5 shows the command that you would type when:

- The controller for the drive you wish to boot is in option slot 3.

- You are booting an RZ-series drive, disk number 0.

- The file you wish to boot is called flash\_citca.

Example 4–5 also shows an example of what you can expect to see as a system response. User input is underlined.

## Example 4-5 Loading FLASH\_CITCA Program Image

```

>>boot 3/rz0/flash_citca

Ultrixboot - V4.2 Tue Mar 19 06:15:25 EST 1991

Loading 3/rz0/flash_citca ...

Sizes:

text = 0

data = 736224

bss = 0

Starting at 0xa0330000

Enter image name:

```

#### 4.4.2.2 Booting the System Console Program Image

After the FLASH\_CITCA program image has been loaded, **reset the system** by pressing the system reset button. (On the DECsystem 5900, this button is located on the back of the system box.) Then boot the system console program image using the format >>> boot slot/device/file\_name where:

- boot specifies the boot command.

- *slot* specifies the slot number of the boot device controller.

- device specifies the type and number of the device from which you wish to boot.

- *file name* specifies the name of the file you wish to boot.

Example 4–6 shows the command that you would type when:

- The controller for the drive you wish to boot is in option slot 3.

- You are booting an RZ-series drive, disk number 0.

- The file you wish to boot is called bigmax.

Example 4–6 also shows an example of what you can expect to see as a system response. User input is underlined.

#### Example 4-6 Loading the System Program Image

```

>>boot 3/rz0/bigmax

Ultrixboot - V4.2 Tue mar 19 06:15:25 EST 1991

Loading 3/rz0/bigmax ...

Sizes:

text = 64288

data = 107408

bss = 22048

Starting at 0xa0240100

KN03-AA V5.0a [11/14/91 10:15:36 ferguson]

```

## 4.4.2.3 Overlaying the Existing ROM Objects

After both program images have been loaded, type the three commands shown in Example 4–7. This is a patch to overlay the existing ROM objects for the boot device with a pointer to the FLASH\_CITCA image.

#### Example 4-7 Overlay ROM Objects

## 4.4.3 Running FLASH\_CITCA

The FLASH\_CITCA program may be executed after the load procedure described in Section 4.4.2 is complete. To run FLASH\_CITCA, use the command t slot/flash where:

- *t* specifies the test command.

- *slot* specifies the TURBOchannel slot where the CITCA is installed.

- *flash* specifies that you wish to run the FLASH\_CITCA program.

Example 4-8 shows an example of the command and console output. User input is underlined.

Note

FLASH\_CITCA uses the default value of 1 for the TURBOchannel slot number. If the CITCA is not installed in slot 1, use the operator utility (menu item f) to direct FLASH\_CITCA to the correct value. See Section 4.4.4.

In the DECsystem 5900, the CITCA is typically installed in the TURBOchannel extender - slot 0.

#### Example 4-8 Running FLASH\_CITCA

>>t 0/flash

flash citca 1.00 {CITCA Utility} Modified 03/20/92

Using CITCA in TURBOchannel address = be800000

TURBOchannel slot # = 01

Select one for program execution:

- 0, Execute Tests 1-7 without Operator input

- 1, Test the TURBOchannel Scan Path

- 2, Test the Flashprom region checksums

- 3, Test the RAM Memory

- 4, Test the TCAST Selftest via Node Reset

- 5, Test the TURBOchannel Contained Registers

- 6, Test the TURBOchannel Served Registers

- 7, Test the TURBOchannel Host Memory DMA data exchange

- 8, Utility Clear Flashprom regions (write 0) 9, Utility - Clear and Erase of Flashprom Memory

- a, Utility UPDATE all Flashprom regions

- b, Utility VERIFY all Flashprom regions

- c, Utility INIT\_CB Init Flashprom Control Block

d, Utility EXAM\_CB Examine Flashprom Control Block

e, Utility EXAM\_PG Examine program Control Block

f, Utility OPERATOR Change flags and TURBOchannel slot

- h, or ? retype this header

| W |  |  |

|---|--|--|

|   |  |  |

Menu items 8 and 9 destroy the contents of the FLASH PROM. These utilities should never be run.

## 4.4.4 Selecting the TURBOchannel Slot Number

If the CITCA is not installed in TURBOchannel slot 1 (the default), use the Operator utility (FLASH\_CITCA test f) to change the TURBOchannel slot value. This utility is menu driven, and the procedure consists of four steps.

- 1. Select *f* at the flash\_citca > prompt.

- 2. Respond to the four event flag prompts.

- Type y in response to the following line.

Change to a different TURBOchannel address (N/y)

- 4. Select the correct slot number from the lists of choices.

Example 4–9 shows how the Operator utility is used to change the TURBOchannel value to 0. User input is underlined.

#### Example 4-9 Selecting the TURBOchannel Slot

```

flash_citca 1.00 > f

Using CITCA in TURBOchannel address = be800000

TURBOchannel slot # = 01

Event flag HALT

is = CLEARED - Change flag state (N/y)?

Event flag LOOP is = CLEARED - Change flag state (N/y)?

Event flag INHIBIT is = CLEARED - Change flag state (N/y)?

Event flag QUICK is =

SET

- Change flag state (N/y)?

Change to a different TURBOchannel address (N/y)? y

Enter 0: DS5900/DS5240, TURBOchannel slot 0, address be000000

Enter 1: DS5900/DS5240, TURBOchannel slot 1, address be800000

Enter 2: DS5900/DS5240, TURBOchannel slot 2, address bf000000

Enter 3: [Reserved for MFG!] TURBOchannel slot 0, address be000000

Enter 4: [Reserved for MFG!] TURBOchannel slot 1, address be400000

Enter 5: [Reserved for MFG!] TURBOchannel slot 2, address be800000

Enter TURBOchannel address menu selection: 0

Using CITCA in TURBOchannel address = be000000

TURBOchannel slot # = 00

Event flag HALT is = CLEARED

Event flag LOOP is = CLEARED

Event flag INHIBIT is = CLEARED

Event flag QUICK is =

SET

flash_citca 1.00 >

```

## 4.4.5 Running Individual FLASH\_CITCA Tests

The FLASH\_CITCA program is menu driven. At the flash\_citca > prompt, select a single character to execute any one of the FLASH\_CITCA tests. Example 4–10 shows how to run test 3, the RAM memory test.

#### Example 4-10 Running Test 3

```

flash_citca V1.00 > \frac{3}{2}

Test 3 - RAM Memory (15 seconds) flash citca V1.00 >

```

## 4.4.6 Exiting from FLASH\_CITCA

To exit from the FLASH\_CITCA program, type q at the flash\_citca > prompt. This will return control to the console executive.

When you have finished using the FLASH\_CITCA program, power down the system to reset the ROM objects. Failure to do so will cause a failure when you try to boot the operating system because the ROM objects have been set to point to the FLASH\_CITCA image. Refer to Section 4.4.2.3.

#### 4.4.7 Fault Isolation

When FLASH\_CITCA detects a failure, it isolates the source of the problem to the failing function and reports error information to the console. The error information and register contents are written in hexadecimal notation. Example 4–11 shows an error report. In this example, the failing RAM location is provided (address), along with the expected and received data.

#### Example 4-11 FLASH CITCA Error Report

```

flash_citca V1.00 > 3

Test 3 - RAM Memory (15 seconds)

pmcs ram data (555555) error

Address - 0000

Expected

00155555

55555555

5555555

Received

0015d555

55555555

5555555

pmcs ram data (AAAAAA) error

Address - 0000

Expected

002aaaaa

aaaaaaaa

aaaaaaaa

Received

002aefaa

aaaaaaaa

aaaaaad5

```

## 4.4.8 Updating the FLASH PROM

To update the microcode in the FLASH PROM:

- 1. Set the FLASH PROM write enable switch on the CITCA module (hardware switchpack 1, switch 1) to off.

- 2. Load the FLASH\_CITCA program (Section 4.4.2).

- 3. Run the FLASH\_CITCA program (Section 4.4.3).

- 4. Select menu item a at the flash\_citca > prompt.

- 5. Exit the FLASH\_CITCA program by typing q at the flash\_citca > prompt.

- 6. Reset the system power by placing the system power switch in the off (O) position, then the on (I) position. See the system documentation for the location of this switch.

- 7. Verify the success of the update by checking the version of the microcode with the *cnfg* command.

- 8. Boot the operating system.

Example 4–12 shows the console output from steps 4 through 7. User input is underlined.

#### Example 4-12 Updating the FLASH PROM

```

flash_citca V1.00 > \underline{a}

Flashprom clear operation started

Clearing region 0...

Clearing region 1...

Clearing region 2...

Clearing region 3...

Clearing region 4...

Clearing region 5...

Clearing region 6...

Clearing region 7...

Flashprom erase operation started

```

(continued on next page)

## Example 4-12 (Cont.) Updating the FLASH PROM

```

Erasing region 0...

Erasing region 1...

Erasing region 2...

Erasing region 3...

Erasing region 4...

Erasing region 5...

Erasing region 6...

Erasing region 7...

Starting to write the DIAGNOSTIC Microcode (Flashprom region 0)

Starting to write the FUNCTIONAL Microcode (Flashprom region 1)

Starting to write the RESPONDER Microcode (Flashprom region 2)

(Flashprom region 4)

Starting to write the RESPONDER

data1

Starting to write the RESPONDER \,

(Flashprom region 5)

data2

Starting to write the RESPONDER

data3

(Flashprom region 6)

Starting to write the RESPONDER

data4

(Flashprom region 7)

Flashprom UPDATE operation completed

Starting to VERIFY the DIAGNOSTIC Microcode (Flashprom region 0)

Starting to VERIFY the FUNCTIONAL Microcode (Flashprom region 1)

Starting to VERIFY the RESPONDER Microcode (Flashprom region 2)

Starting to VERIFY the RESPONDER

data1

(Flashprom region 4)

Starting to VERIFY the RESPONDER

data2

(Flashprom region 5)

Starting to VERIFY the RESPONDER

data3

(Flashprom region 6)

Starting to VERIFY the RESPONDER

data4

(Flashprom region 7)

Flashprom VERIFY operation completed

flash_citca V1.00> q

! Reset the system power

V5.3a

7:

KN02-AA

DEC

TCF0

( 32 MB)

PMAD AA

DEC

V5.3a

TCF0

(enet: 08-00-2b-1c-1d-07)

6:

5:

PMAZ AA DEC

V5.3b

TCF0

(SCSI = 7)

(CI node address: 001\{d\}, PDFLT = e0\{x\})

2:

CITCA-AA DEC

V1.01

TCF0

```

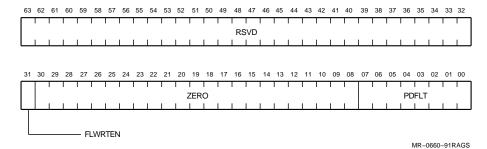

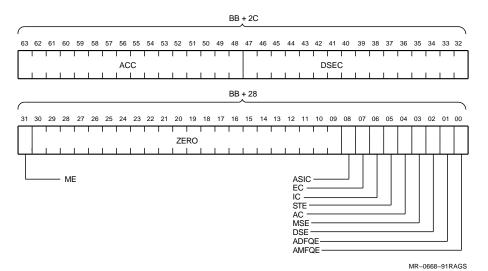

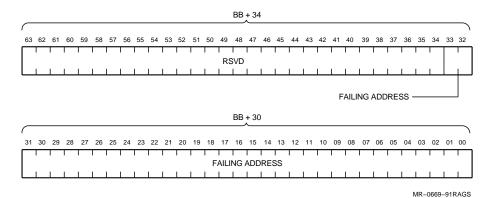

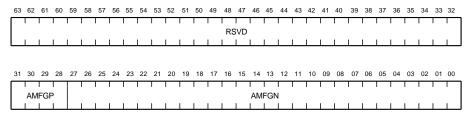

# **Functional Description**